AD9375 帶有觀察路徑的集成雙射頻收發(fā)器

數(shù)據(jù):

AD9375產(chǎn)品技術(shù)英文資料手冊

優(yōu)勢和特點(diǎn)

- 雙差分發(fā)射器 (Tx)

- 雙差分接收器 (Rx)

- 帶有 2 路輸入的觀察接收器

- 完全集成的超低功耗 DPD 勵(lì)磁器和適合 PA 線性化的自適應(yīng)引擎

- 帶有 3 路輸入的嗅探接收器

- 調(diào)諧范圍:300 MHz 到 6000 MHz

- 線性化信號(hào) BW 到 40 MHz

- 接收器合成 BW 到 250 MHz

- 接收器 (Rx) BW:8 MHz 到 100 MHz

- 支持 FDD 和 TDD 操作

- 完全集成的獨(dú)立小數(shù)分頻射頻合成器,可用于發(fā)射器 (Tx)、接收器 (Rx)、觀察接收器 (ORx) 和時(shí)鐘生成

- JESD204B 數(shù)字接口

產(chǎn)品詳情

AD9375 是高度集成的寬帶射頻 (RF) 收發(fā)器,提供雙通道發(fā)射器 (Tx) 和接收器 (Rx)、集成式合成器、完全集成的數(shù)字預(yù)失真 (DPD) 勵(lì)磁器和自適應(yīng)引擎,以及數(shù)字信號(hào)處理功能。在頻分雙工 (FDD) 和時(shí)分雙工 (TDD) 應(yīng)用中,該 IC 可實(shí)現(xiàn) 3G/4G 小蜂窩和大規(guī)模多入多出 (MIMO) 設(shè)備所需的多種高性能低功耗組合。AD9375 工作范圍為 300 MHz 到 6000 MHz,可覆蓋大部分許可和免許可蜂窩頻段。DPD 算法可線性化處理高達(dá) 40 MHz 的信號(hào)帶寬,具體取決于功率放大器 (PA) 特性(例如,兩個(gè)相鄰的 20 MHz 載波)。該 IC 支持的接收器 (Rx) 帶寬最高達(dá) 100 MHz;支持的觀察接收器 (ORx) 和發(fā)射器 (Tx) 合成帶寬高達(dá) 250 MHz,可適應(yīng)數(shù)字校正算法。

收發(fā)器包括寬帶直接轉(zhuǎn)換信號(hào)路徑,具有出色的噪聲指數(shù)和線性度。每個(gè)完整的接收器 (Rx) 和發(fā)射器 (Tx) 子系統(tǒng)都包括直流失調(diào)矯正、正交誤差校正 (QEC) 以及可編程數(shù)字濾波器,因此數(shù)字基帶中不再需要這些功能。它集成了輔助模擬數(shù)字轉(zhuǎn)換器 (ADC)、輔助數(shù)字模擬轉(zhuǎn)換器 (DAC) 以及通用輸入/輸出 (GPIO) 等若干輔助功能,因而可提供額外的監(jiān)測和控制能力。

該器件包含具有兩路輸入的觀察接收器 (ORx) 通道,以監(jiān)測每個(gè)發(fā)射器輸出并實(shí)施校準(zhǔn)應(yīng)用。這個(gè)通道還連接三個(gè)嗅探接收器 (SnRx) 輸入,可以監(jiān)測不同頻段上的無線電活動(dòng)。

高速 JESD204B 接口支持高達(dá) 6144 Mbps 的線速。四線專用于發(fā)射器,四線專用于接收器和觀察接收器通道。

完全集成的鎖相環(huán) (PLL) 為發(fā)射器 (Tx)、接收器 (Rx) 和觀察接收器 (ORx) 以及時(shí)鐘部分提供高性能、低功耗、小數(shù)分頻合成。精心選用的設(shè)計(jì)和布局技術(shù)提供了高性能基站應(yīng)用所要求的隔離。其中集成了全部壓控振蕩器 (VCO) 和環(huán)路濾波器元件,從而盡可能減少外部元件數(shù)量。

該器件包含完全集成的低功耗 DPD 勵(lì)磁器和適合 PA 線性化使用的自適應(yīng)引擎。DPD 特性支持使用高效 PA,大幅降低小蜂窩基站無線電的功耗,同時(shí)減少了連接基帶處理器所需的 JESD204B 線數(shù)。

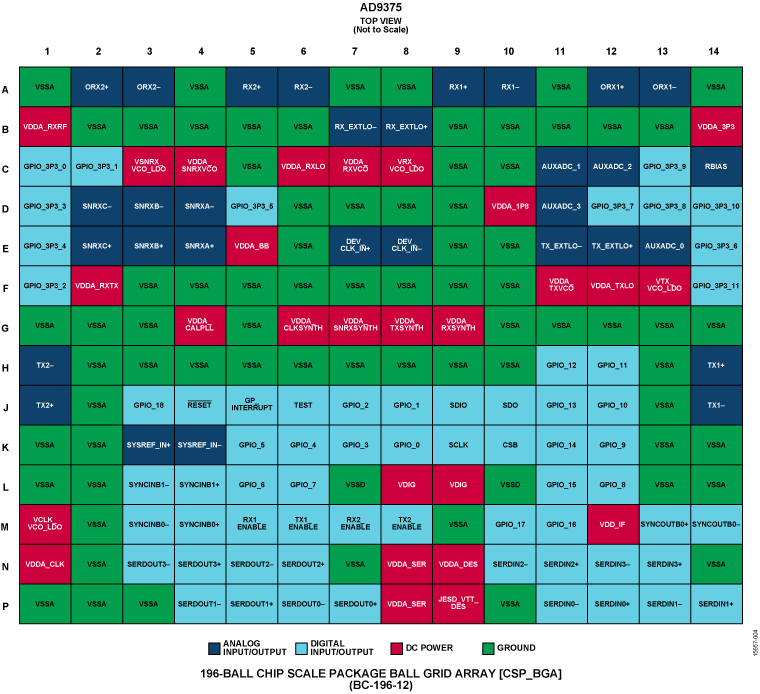

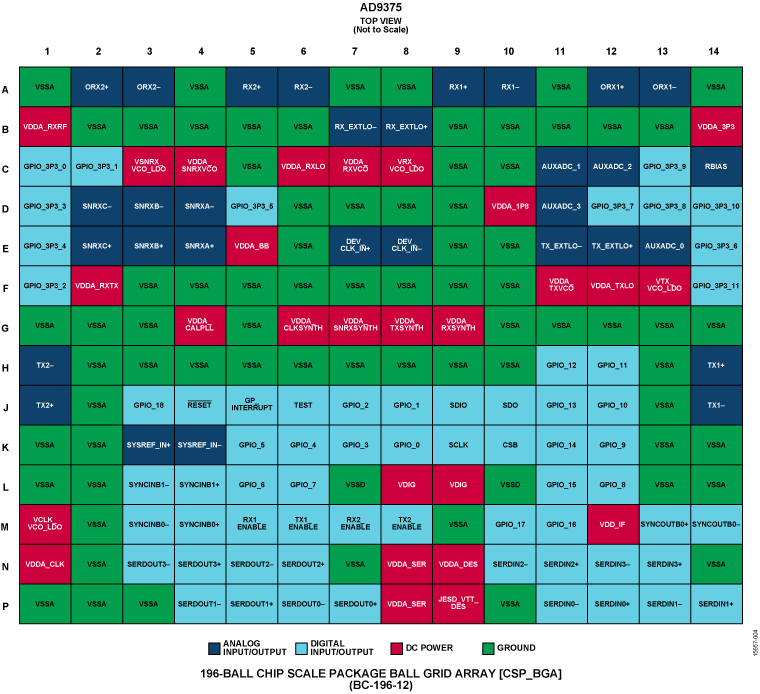

AD9375 內(nèi)核需由 1.3 V 電源供電,并通過標(biāo)準(zhǔn) 4 線串行端口進(jìn)行控制。其他電源提供正確的數(shù)字接口電平,并優(yōu)化發(fā)射器和輔助轉(zhuǎn)換器性能。AD9375 采用 12 mm × 12 mm、196 球芯片級球柵陣列 (CSP_BGA) 封裝。

應(yīng)用

- 3G/4G 小蜂窩基站 (BTS)

- 3G/4G 大規(guī)模 MIMO/有源天線系統(tǒng)

方框圖