“硬件系統龐雜、調試周期長”

“高頻模擬前端不穩定,影響采樣精度”

“接收和發射鏈路難以同步,難以擴展更多通道”

“數據流量大,處理與存儲跟不上”

這些是大部分客戶在構建多通道、高頻寬的射頻采樣鏈路時,面臨的主要問題。

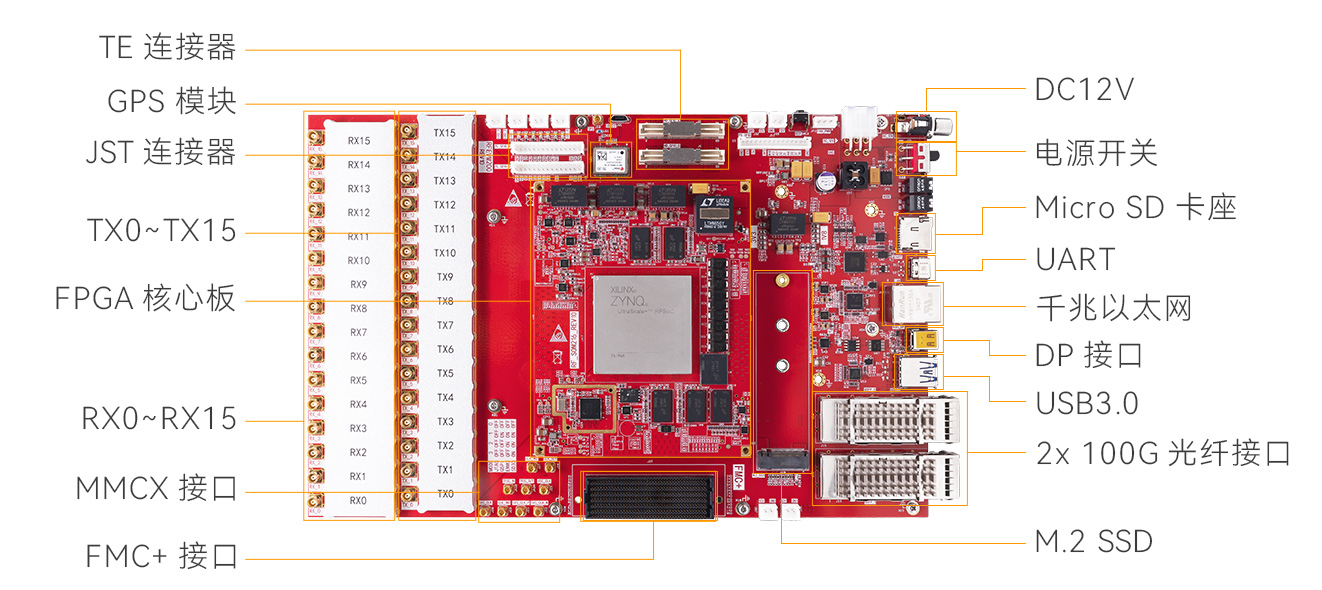

AXRF49 正是為解決這些瓶頸而來——它依托于 AMD 第三代 Zynq UltraScale+ RFSoC ZU49DR,整合了:

高性能射頻模擬前端(支持 sub-6GHz 直接采樣)

讓您從繁瑣的硬件集成中解脫出來,專注于算法和系統創新。

通信原型開發:從分立器件走向單芯片平臺

傳統的 Massive MIMO 或小基站原型開發通常需要多個高速 ADC/DAC 模塊、FPGA 板卡與嵌入式處理器組合而成,存在體積大、延時高、功耗高、接口調試復雜等問題,導致研發周期長、系統穩定性差。

AXRF49 通過內建的 16 路 14 位 DAC(最高 9.85GSPS)與 16 路 14 位 ADC(最高 2.5GSPS),實現了sub-6GHz頻段內的直接射頻采樣與發射,徹底省去了中頻變換鏈路。再加上其高達930K 邏輯單元、4272 DSP 單元的 FPGA 資源,可直接實現信道估計、波束賦形、DFFT、LDPC 解碼等物理層加速邏輯。

光纖接口支持2×100G QSFP28,配合 5GB PL DDR4 帶寬緩存與 M.2 NVMe,本地與遠端處理無縫銜接,打造低延時、高并發的無線接入測試平臺,適合 5G NR 和未來的 6G 空口研究。

相控陣雷達

同步、多通道、高速處理能力合一

雷達波束控制與干擾信號合成通常對多通道同步、采樣精度、低相位噪聲、高帶寬處理能力要求極高。而傳統以多卡片堆疊方式構建陣列系統,不僅接口繁雜,同步性差,且系統集成工作量巨大。

通過 RFSoC ZU49DR 的 RF-ADC/DAC 模塊,AXRF49 可同步采集/發射16 路射頻信號,為相控陣波束形成提供硬件基礎。利用其可編程插值/抽取(1x~40x)功能,在保證高采樣率的同時實現頻域調制、抗混疊處理,滿足雷達對不同信號體制的適配需求。

結合 FPGA 邏輯資源,可實現LFM 信號調制、脈壓、MTI/MTD 處理等關鍵算法,借助高速光口與外部后端進行實時數據記錄或識別。相比傳統方案,AXRF49 將“模擬前端+數字處理+系統控制”三者融合于單板,有效縮短系統搭建周期,并降低干擾路徑復雜度。

醫療/工業檢測新模式

高速數據采集與邊緣AI融合處理

在高端超聲、光學成像、射線檢測等場景中,既需要高采樣精度和實時性,又希望將更多智能前處理下沉至邊緣端。

AXRF49 通過 RFSoC 將高速模擬采集鏈路(ADC)與 AI 運算能力有機結合,16 路 14 位 ADC 可覆蓋多探頭傳感器陣列,用戶可基于強大的 FPGA 資源,靈活部署降噪、濾波、特征提取、智能壓縮等算法,在 ARM Cortex-A53 與 R5 核心上進行深度模型推理或控制邏輯處理。

數據可通過NVMe SSD 或 USB3.0實時落盤,或經高速光纖/以太網上傳至邊緣服務器,滿足工業質檢與遠程醫療對實時性與數據完整性的雙重需求。AXRF49 支持在本地 FPGA 內部署預處理邏輯,真正實現“邊采集、邊處理”的架構升級,順應“采集即智能”的行業趨勢。

從多通道射頻采集到邊緣智能預處理,再到高速數據外聯,AXRF49 讓原型驗證不再受制于平臺碎片化。它能幫助您縮短研發路徑,助力您的方案更快落地、更穩健走向工程化。

ALINX 提供完整的用戶開發手冊和工具鏈與全備的技術支持,幫助您縮短從原型到量產的周期。歡迎您花 1 分鐘掃碼填寫“客戶信息登記表”,告訴我們您的需求。

審核編輯 黃宇

-

FPGA

+關注

關注

1643文章

21969瀏覽量

614275 -

射頻

+關注

關注

106文章

5729瀏覽量

169780 -

RFSoC

+關注

關注

0文章

36瀏覽量

2869

發布評論請先 登錄

米爾NXP i.MX 91核心板發布,助力新一代入門級Linux應用開發

新品!米爾NXP i.MX 91核心板,賦能新一代入門級Linux應用

nRF54系列新一代無線 SoC

直采+異構,看 RFSoC FPGA 開發板 AXW49 如何應對射頻信號處理高要求

芯華章推出新一代高性能FPGA原型驗證系統

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

推薦一款極具性價比的RFSoC開發平臺

一板多能,AXRF49 定義新一代 RFSoC FPGA 開發平臺

一板多能,AXRF49 定義新一代 RFSoC FPGA 開發平臺

評論