完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

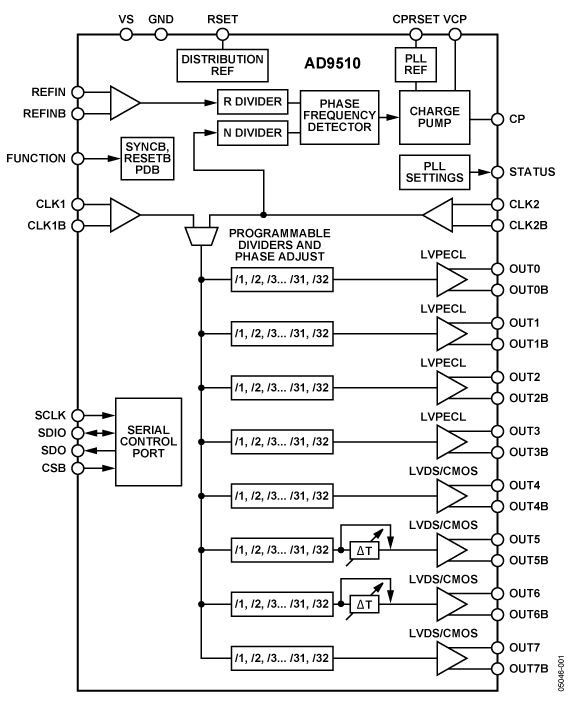

PLL部分由可編程參考分頻器(R)、低噪聲鑒頻鑒相器(PFD)、精密電荷泵(CP)和可編程反饋分頻器(N)組成。將外部VCXO或VCO連接到CLK2和CLK2B引腳時,最高達1.6 GHz的PLL輸出頻率可以與輸入參考REFIN同步。

時鐘分配部分提供LVPECL輸出和可編程為LVDS或CMOS的輸出。每路輸出都有一個可編程分頻器,可以旁路該分頻器或者設置最高32的整數分頻比。

用戶可以通過各分頻器改變一路時鐘輸出相對于其它時鐘輸出的相位,這種相位選擇功能可用于時序粗調。某些輸出還提供可編程延遲特性,具有最長10 ns的用戶可選滿量程延遲值。該精調延遲模塊通過一個5位字進行編程,提供32個可用的延遲時間供用戶選擇。

AD9510非常適合數據轉換器時鐘應用,利用亞皮秒抖動編碼信號,可實現最佳的轉換器性能。

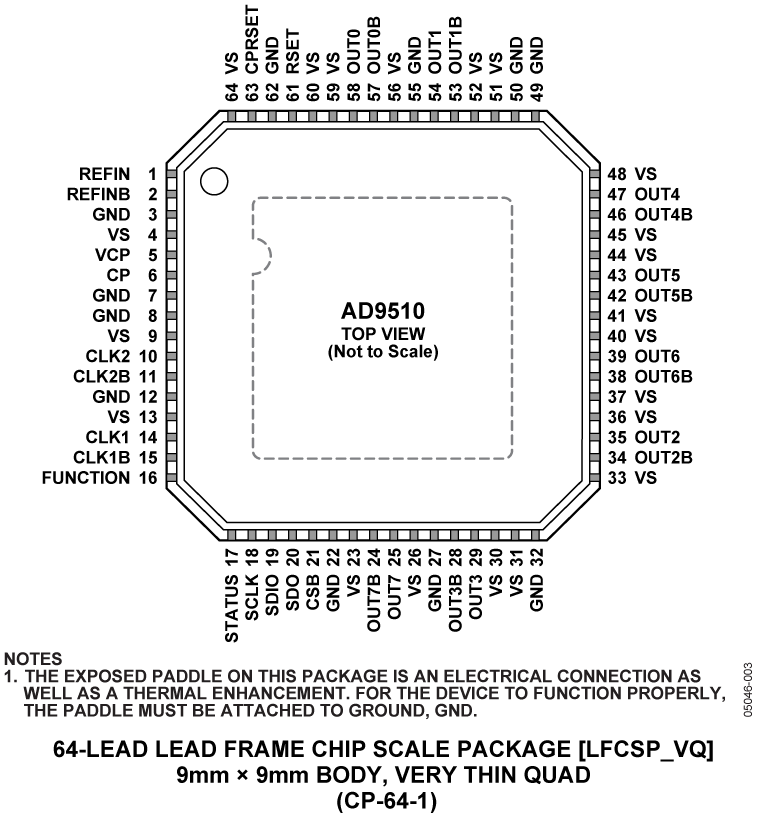

AD9510提供64引腳LFCSP封裝,額定溫度范圍為-40°C至+85°C,可以采用3.3 V單電源供電。如果用戶希望擴展外部VCO的電壓范圍,可以利用最高達5.5V的電荷泵電源VCP。