在數(shù)字電子系統(tǒng)的運(yùn)行中,時(shí)鐘電路掌控著各部件協(xié)同工作的節(jié)奏。它通常由時(shí)鐘發(fā)生器、時(shí)鐘分頻器、時(shí)鐘緩沖器等核心部分構(gòu)成,這些組件各司其職,共同確保電子系統(tǒng)的穩(wěn)定運(yùn)行。接下來,我們將深入探究時(shí)鐘電路的組成。

一、時(shí)鐘電路的核心組成部分

(一)時(shí)鐘發(fā)生器

時(shí)鐘發(fā)生器是時(shí)鐘電路的根基,其核心任務(wù)是產(chǎn)生穩(wěn)定的基準(zhǔn)時(shí)鐘信號。石英晶體振蕩器是最常用的選擇,它利用石英晶體的壓電效應(yīng),將機(jī)械振動(dòng)轉(zhuǎn)換為電信號,從而生成高度穩(wěn)定的頻率。由于石英晶體的物理特性,這種振蕩器能在 -40℃至 85℃的溫度范圍內(nèi),實(shí)現(xiàn)極低的頻率漂移,確保輸出信號的穩(wěn)定性。除了石英晶體振蕩器,RC 振蕩電路也會(huì)在一些對精度要求不高的場景中使用,它通過電阻和電容的充放電過程產(chǎn)生振蕩信號 ,成本較低但穩(wěn)定性相對較弱。此外,還有 MEMS 振蕩器等新型器件,為時(shí)鐘發(fā)生器提供了更多樣化的選擇。

(二)時(shí)鐘分頻器

當(dāng)基準(zhǔn)時(shí)鐘信號頻率過高或不符合系統(tǒng)需求時(shí),時(shí)鐘分頻器便發(fā)揮作用。它通過數(shù)字邏輯電路,如計(jì)數(shù)器等,對基準(zhǔn)時(shí)鐘信號進(jìn)行分頻處理。例如,在微控制器系統(tǒng)中,若基準(zhǔn)時(shí)鐘頻率為 100MHz,而某些外設(shè)僅需 10MHz 的時(shí)鐘信號,時(shí)鐘分頻器就能將 100MHz 的信號進(jìn)行 10 分頻,得到所需頻率。分頻器的設(shè)計(jì)靈活多樣,可根據(jù)不同的系統(tǒng)需求,實(shí)現(xiàn) 2 分頻、4 分頻甚至更高倍數(shù)的分頻操作,為系統(tǒng)各部分提供適配的時(shí)鐘頻率。

(三)時(shí)鐘緩沖器

時(shí)鐘緩沖器的主要功能是對時(shí)鐘信號進(jìn)行放大和驅(qū)動(dòng)。在復(fù)雜的電子系統(tǒng)中,時(shí)鐘信號需要傳輸?shù)奖姸嗖考S著傳輸距離的增加和負(fù)載的增多,信號會(huì)出現(xiàn)衰減、畸變等問題。時(shí)鐘緩沖器能夠增強(qiáng)時(shí)鐘信號的電平、幅度和電流驅(qū)動(dòng)能力,確保信號在長距離傳輸和多負(fù)載情況下,依然能保持準(zhǔn)確的波形和足夠的強(qiáng)度,使系統(tǒng)各部件都能接收到清晰穩(wěn)定的時(shí)鐘信號。

二、時(shí)鐘電路的設(shè)計(jì)要點(diǎn)

(一)穩(wěn)定性:頻率與相位的堅(jiān)守

穩(wěn)定性是時(shí)鐘電路的關(guān)鍵指標(biāo),它要求時(shí)鐘信號的頻率和相位保持高度穩(wěn)定。頻率的不穩(wěn)定會(huì)導(dǎo)致系統(tǒng)各部件工作節(jié)奏混亂,而相位的偏差則可能引發(fā)數(shù)據(jù)傳輸錯(cuò)誤。在設(shè)計(jì)中,選擇高品質(zhì)的振蕩器、合理布局電路、減少電磁干擾等措施,都有助于提升時(shí)鐘信號的穩(wěn)定性。例如,將時(shí)鐘發(fā)生器與其他高頻電路隔離,可降低電磁干擾對時(shí)鐘信號的影響。

(二)精確性:準(zhǔn)確一致的保障

精確性關(guān)乎時(shí)鐘信號的準(zhǔn)確度和一致性。在通信設(shè)備等對時(shí)間精度要求極高的系統(tǒng)中,時(shí)鐘信號的微小誤差都可能導(dǎo)致數(shù)據(jù)傳輸錯(cuò)誤。通過采用高精度的晶體振蕩器、進(jìn)行溫度補(bǔ)償以及優(yōu)化電路設(shè)計(jì)等方法,可以提高時(shí)鐘信號的精確性,確保系統(tǒng)運(yùn)行的可靠性。

(三)時(shí)延:信號傳遞的效率

時(shí)鐘信號在電路中的傳輸延遲時(shí)間,即時(shí)延,也不容忽視。過長的時(shí)延會(huì)使系統(tǒng)各部件之間的時(shí)序出現(xiàn)偏差,影響系統(tǒng)性能。在設(shè)計(jì)時(shí),需要合理規(guī)劃時(shí)鐘信號的傳輸路徑,減少信號走線長度,選擇合適的緩沖器等,以降低時(shí)延,保證時(shí)鐘信號能夠快速、準(zhǔn)確地傳遞到各個(gè)部件。

(四)功耗:能量的合理利用

時(shí)鐘電路本身的功耗也是設(shè)計(jì)時(shí)需要考慮的因素。在便攜式電子設(shè)備等對功耗敏感的場景中,降低時(shí)鐘電路的功耗可以延長設(shè)備的續(xù)航時(shí)間。通過選擇低功耗的器件、優(yōu)化電路結(jié)構(gòu)等方式,能夠有效減少時(shí)鐘電路的功耗,實(shí)現(xiàn)能量的合理利用。

時(shí)鐘電路的各個(gè)組成部分緊密協(xié)作,其設(shè)計(jì)需綜合考慮穩(wěn)定性、精確性、時(shí)延和功耗等多方面因素。隨著電子技術(shù)的不斷發(fā)展,對時(shí)鐘電路的要求也日益提高,未來,它將在更多領(lǐng)域發(fā)揮關(guān)鍵作用,推動(dòng)電子系統(tǒng)向更高性能邁進(jìn)。

-

時(shí)鐘緩沖器

+關(guān)注

關(guān)注

2文章

142瀏覽量

51233 -

分頻器

+關(guān)注

關(guān)注

43文章

490瀏覽量

50803 -

時(shí)鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

223瀏覽量

68842 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

243瀏覽量

51235

發(fā)布評論請先 登錄

計(jì)算機(jī)組成原理各章復(fù)習(xí)重點(diǎn),計(jì)算機(jī)組成原理復(fù)習(xí)要點(diǎn)說明.doc 精選資料分享

DCDC電源模塊組成及要點(diǎn)

DCDC電源模塊的組成及要點(diǎn)

用于高速AD的低抖動(dòng)時(shí)鐘穩(wěn)定電路

AT89C2051組成的時(shí)鐘電路原理圖

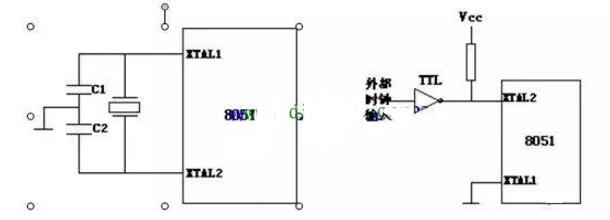

單片機(jī)時(shí)鐘電路

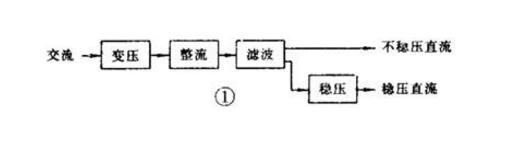

將對電源電路圖的讀圖要點(diǎn)進(jìn)行介紹并舉例

電源電路組成及作用介紹_電源電路原理圖及工作原理

51單片機(jī)時(shí)鐘電路圖匯總(八款單片機(jī)時(shí)鐘電路圖)

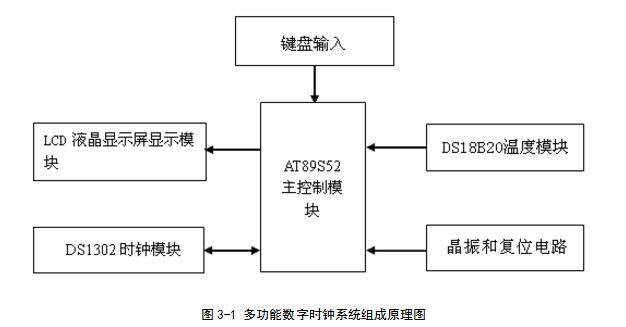

單片機(jī)多功能數(shù)字時(shí)鐘設(shè)計(jì)電路大全(五款單片機(jī)多功能數(shù)字時(shí)鐘設(shè)計(jì)電路)

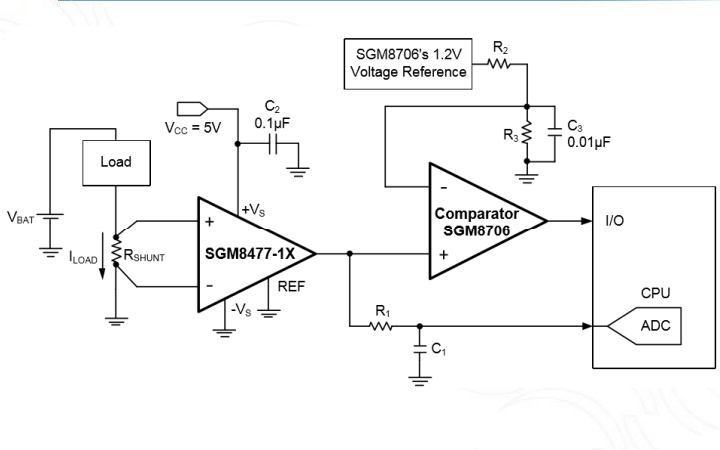

高精度電流采樣電路設(shè)計(jì)要點(diǎn)的詳細(xì)說明

MSP430G2553時(shí)鐘系統(tǒng)要點(diǎn)總結(jié)

時(shí)鐘電路的組成與設(shè)計(jì)要點(diǎn)介紹

時(shí)鐘電路的組成與設(shè)計(jì)要點(diǎn)介紹

評論