易靈思的FPGA在生成PLL的方式與別的廠家稍有區別,這與其的core和interface架構是相對應的。對于易靈思的FPGA來講,PLL,GPIO,MIPI,LVDS和DDR相對于core部分都是外設。而這些外設的設置都是在interface designer中的。下面以pll的添加為例,對于trion系列的設置簡單說明。鈦金系列會稍微的區別,但是只要了解了一個,另一個都是大同小異的。

一、PLL的添加

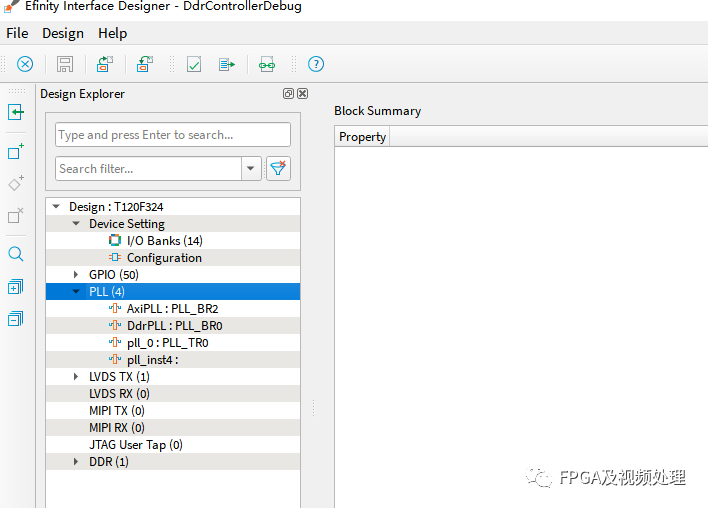

(1)打開interface desinger。

(2)選擇pll 右擊選擇Create block,就可以添加pll

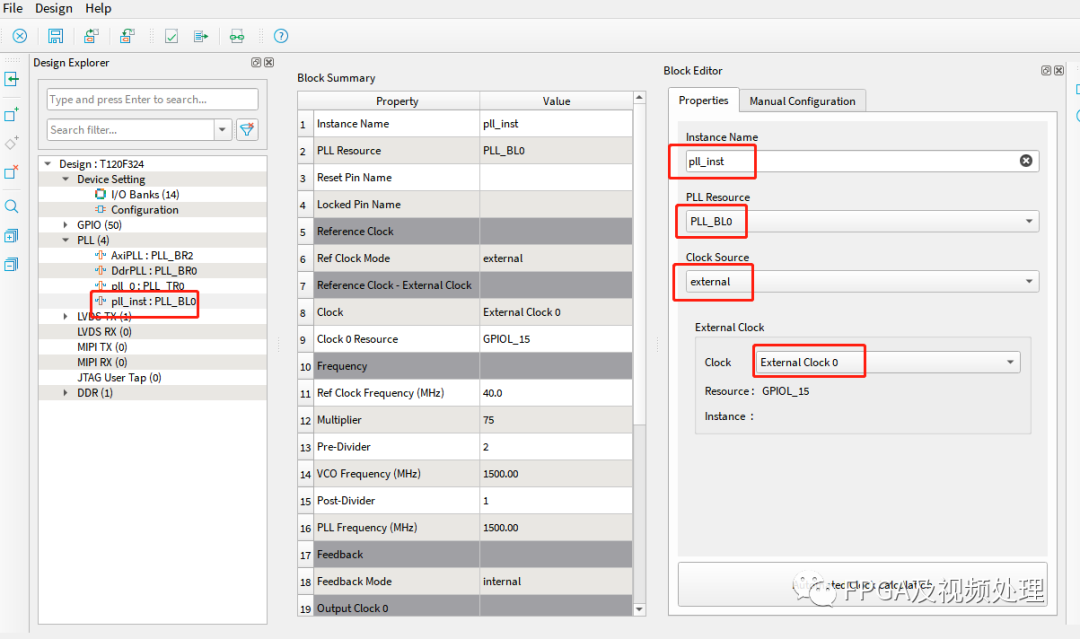

(3)這里我們把pll的例化名修改為pll_inst,并且按回車(必須回車)。

PLL resource對應PLL的位置,這也是易靈思的PLL使用與別家有區別的地方,必須要指定PLL的位置。

clock source是指pll參考時鐘的源來自哪里,包括外部和內部。

External clock:指示參考時鐘的源,包括參考時鐘0,參考時鐘1。

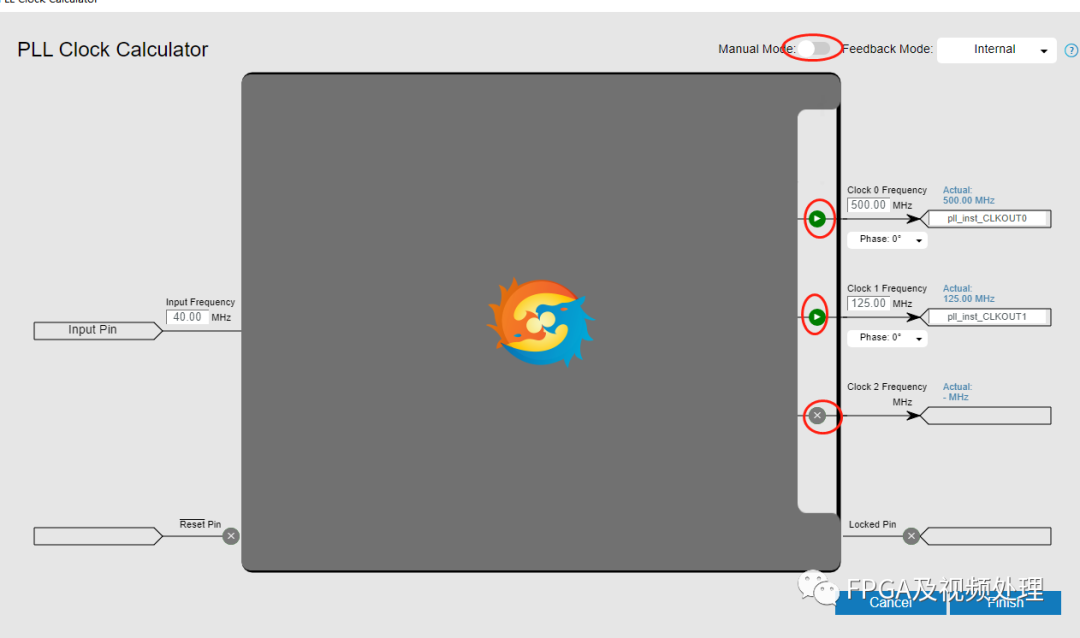

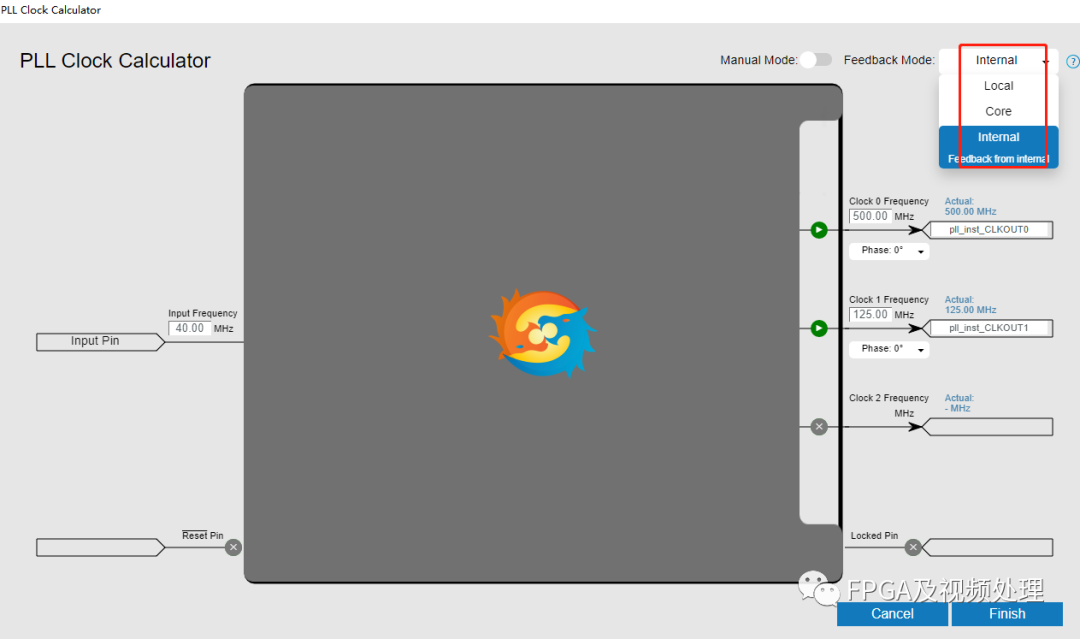

(4)點擊Automated Clock Calculation打開時鐘設置界面。trion最多可以設置3個時鐘,紅包框中的箭頭和x可以用于打開和關閉相應的時鐘。

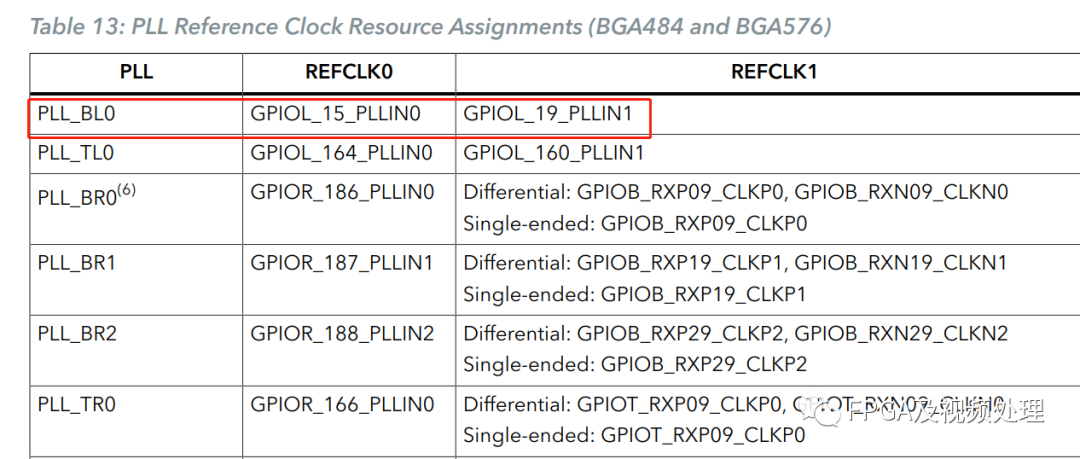

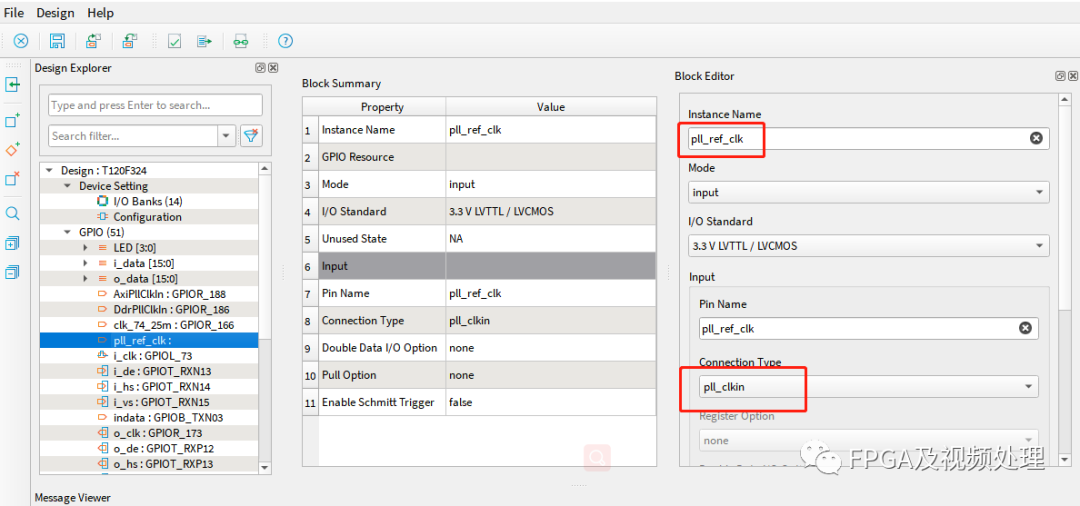

(5)設置完成上面的操作之后,我們需要指定PLL的參考時鐘來源。從ds上我們可以看到PLL_BL0有兩個時鐘源,分別是REFCLK0和REFCLK1,分別對應GPIOL_15_PLLIN0和GPIOL_19_PLLIN1。

然后再添加PLL的參考時鐘腳,這里我們例化為pll_ref_clk,并要把connection Type設置為pll_clkin。并分配到GPIOL_15_PLLIN0上,因為上面選擇了External Clock0。這樣PLL的設置就差不多了。

二、關于時鐘源

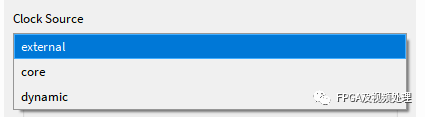

在選擇clock source時,有三個選項,分別是external, core和dynamic。

external好理解,就是參考時鐘從外部IO進入的,上面的設置就是。

core是指時鐘從FPGA內部給PLL的參考,比如一個PLL的輸出給另一個PLL做參考時,第二個PLL的參考就是設置成core,或者從GCLK進入FPGA再環到PLL的輸入。

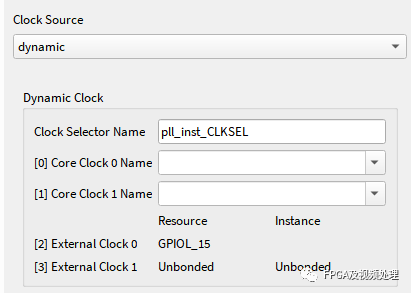

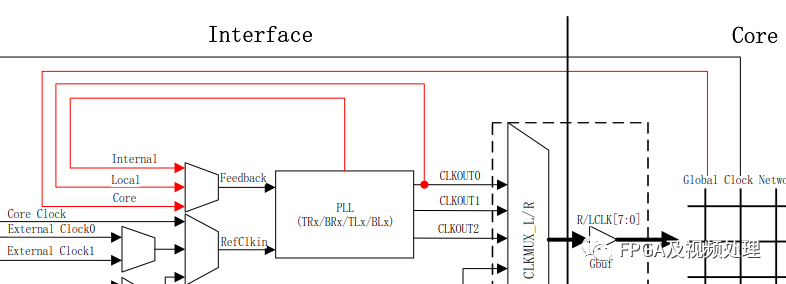

至于Dynamic Clock就是動態輸入選擇,支持多路選擇,如下圖,可以支持兩個core和兩個external時鐘。但是因為PLL不支持動態重配置,所以這個功能應用有限。

三、PLL的反饋方式

PLL有三種反饋,core,Local和internal。

從下面的圖來看,不同的反饋位置是不一樣的。core的反饋路徑是從FPGA的core內部來反饋,可以保證輸入時鐘與輸出時鐘同頻同相。這在源同步設計中是很有用的。而local和internal可以支持輸出更多的頻率,大家可以在操作中發現如果是core反饋的話,有些頻率是設置不出來的,而local和interanl卻可以。

關于PLL的注意事項

(1) PLL的反饋時鐘的頻率不能超過refclk的4倍。

(2)經常會有客戶反應上電之后PLL存在失鎖的情況,這是什么原因呢?這個是因為上電時PLL的參考時鐘不穩定,造成PLL不能鎖定在固定的頻率,這樣之后,即使后繼參考時鐘穩定也不能鎖定。

那解決方案是什么呢?要求等參考時鐘穩定之后再釋放PLL的復位,或者等參考時鐘穩定之后再復位一次。

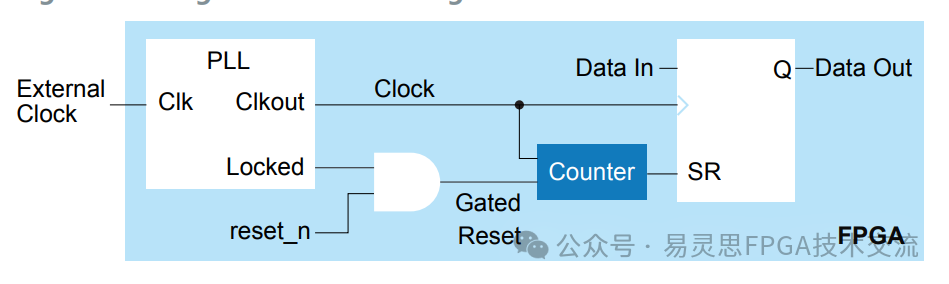

(3)當需要使用PLL的locked信號做為復位時,要求pll的locked信號拉高25us之后再釋放復位。如下圖,在locked信號之后添加計數器,記數到25us之后釋放器件的SR。

上面描述其實描述相對粗糙,語句什么的也沒有太去考慮措辭,花半個小時BB下,能用起來就行,如果實在有看不懂的,歡迎留言。

審核編輯 黃宇

-

pll

+關注

關注

6文章

884瀏覽量

136055

發布評論請先 登錄

原廠方案:利用力科示波器設置PLL參數

harmony OS NEXT-Navagation基本用法

LMX2820 PLL_NUM / PLL_DEN減到最低項是什么意思呢?

鎖相環PLL的噪聲分析與優化 鎖相環PLL與相位噪聲的關系

鎖相環PLL的常見故障及解決方案

鎖相環PLL在無線電中的應用 鎖相環PLL與模擬電路的結合

Linux lsof命令的基本用法

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發生器數據表

PLL是什么意思

LVDS用法:LVDS RX 時鐘選擇 LVDS的PLL的復位信號的處理

PLL用法

PLL用法

評論