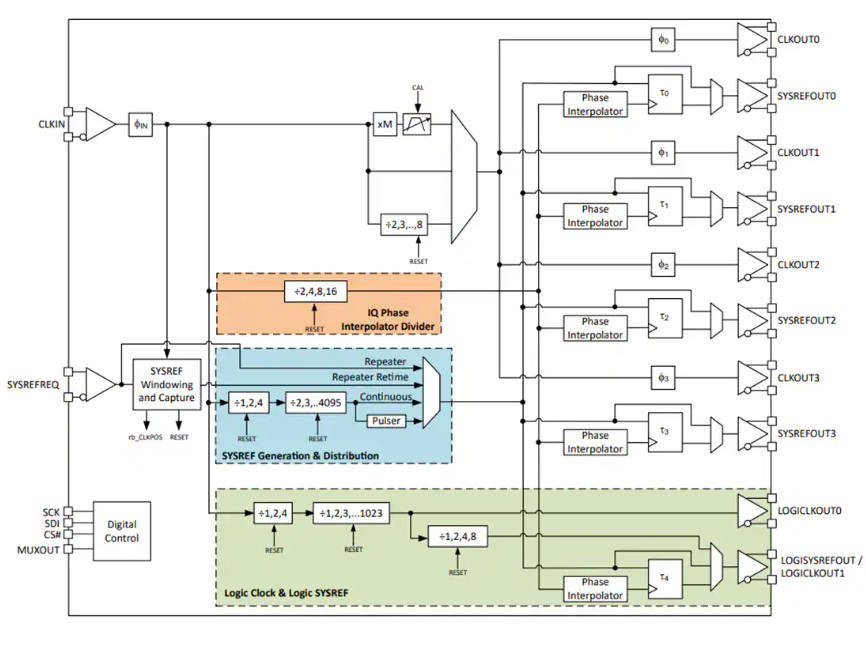

Texas Instruments LMX1205 JESD緩沖器/乘法器/分頻器具有高頻能力、極低抖動以及可編程時鐘輸入和輸出延遲。得益于以上特性,該器件非常適用于時鐘高精度高頻數據轉換器,且不會降低信噪比。四個高頻時鐘輸出和具有較大分頻器范圍的額外LoICLK輸出均與SYSREF輸出時鐘信號配對。用于JESD204B/C接口的SYSREF信號可以作為輸入通過或內部生成,并重新計時到器件時鐘。高頻時鐘輸入和單獨時鐘輸出路徑的輸入路徑上的無噪聲延遲調整可確保多通道系統中的低偏移時鐘。對于數據轉換器時鐘應用,時鐘抖動小于數據轉換器的孔徑抖動至關重要。在需要計時超過四個數據轉換器的應用中,可以使用多個器件開發各種級聯架構,分配所需的所有SYSREF信號和高頻時鐘。Texas Instruments LMX1205與超低噪聲參考時鐘源結合使用時,非常適用于時鐘數據轉換器,尤其是在高于3GHz時。

數據手冊:*附件:Texas Instruments LMX1205 JESD緩沖器,乘法器,除法器數據手冊.pdf

特性

- 輸出頻率:300MHz至12.8GHz

- 無噪聲可調輸入延遲高達60ps,分辨率為1.1ps

- 獨立可調輸出延遲高達55ps,分辨率為0.9ps

- 四個具有相應SYSREF輸出的高頻時鐘

- 共享1分頻(旁路)、2、3、4、5、6、7和8

- 共享可編程乘法器x2、x3、x4、x5、x6、x7和x8

- 具有相應SYSREF輸出的LOGICLK輸出

- 在單獨的分頻器組上

- 1、2、4預分頻器

- 1(旁路)、2、......、1023后分頻器

- 第二個邏輯時鐘選項,帶額外分頻器1、2、4和8

- 超低噪聲

- 噪聲基底:-159dBc/Hz(6GHz輸出時)

- 附加抖動(直流至fCLK):36fs

- 附加抖動(100Hz至100MHz):10fs

- 六個可編程輸出功率電平

- 同步SYSREF時鐘輸出

- 508個延遲步進調整,在12.8GHz時小于2.5ps

- 發生器、中繼器和中繼器重時模式

- 系統參考請求引腳的窗口功能,以優化時序

- 針對所有分頻和倍頻器件的同步功能

- 工作電壓:2.5V

- 工作溫度:-40oC至85oC

應用

框圖

-

緩沖器

+關注

關注

6文章

2056瀏覽量

47008 -

分頻器

+關注

關注

43文章

492瀏覽量

51145 -

乘法器

+關注

關注

9文章

212瀏覽量

37958

發布評論請先 登錄

求助,LMX2572LP參考時鐘路徑中的乘法器MULT的輸入頻率范圍問題求解

并行除法器 ,并行除法器結構原理是什么?

MPY600 具有負載驅動功能的乘法器

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

CDCS503帶可選SSC的時鐘緩沖器/時鐘乘法器數據表

Texas Instruments LMX1205 JESD緩沖器/乘法器/除法器數據手冊

Texas Instruments LMX1205 JESD緩沖器/乘法器/除法器數據手冊

評論