No.1引言

隨著現代電子系統的不斷發展,時鐘管理成為影響系統性能、穩定性和電磁兼容性(EMI)的關鍵因素之一。在FPGA設計中,PLL因其高精度、靈活性和可編程性而得到廣泛應用,本文將深入探討PLL技術在FPGA中的動態調頻與展頻功能應用。

No.2PLL技術基礎

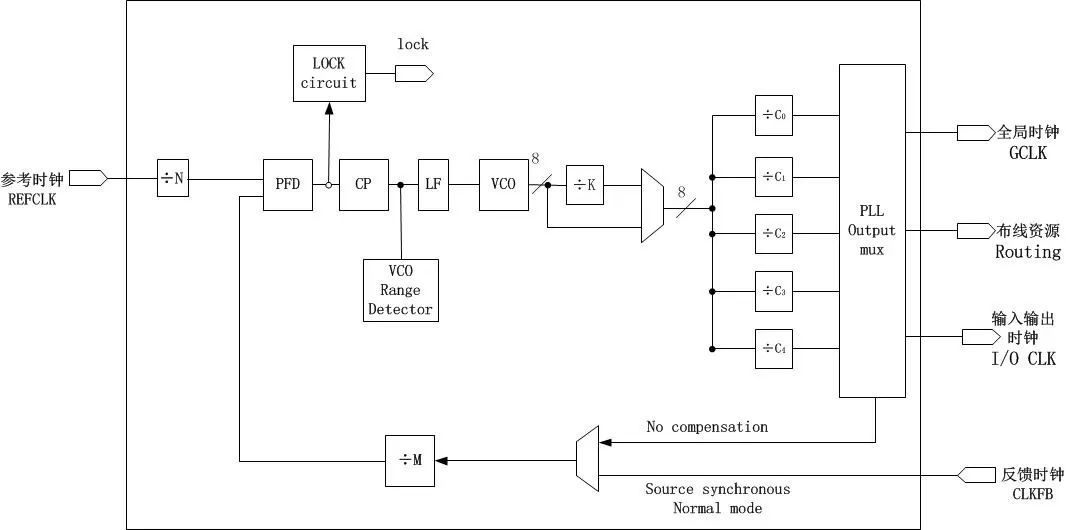

PLL(Phase-Locked Loop,相位鎖定環)是一種反饋控制系統,用于生成和穩定時鐘信號。它主要由鑒相器(PD)、環路濾波器(LF)、壓控振蕩器(VCO)和分頻器組成。PLL通過不斷調整VCO的輸出頻率,使其與參考時鐘信號保持穩定的相位關系,從而實現高精度的時鐘合成。

在FPGA中,PLL模塊提供了可靠的時鐘管理與綜合功能,支持精準分頻和動態調頻。通過PLL,FPGA可以生成多個不同頻率的時鐘信號,滿足復雜系統對時鐘資源的需求。

No.3動態調頻功能應用

動態調頻是指通過編程方式實時調整PLL輸出時鐘的頻率。這一功能在需要靈活配置時鐘頻率的應用場景中尤為重要,如通信系統中的頻率跳變、測試設備中的時鐘校準等。

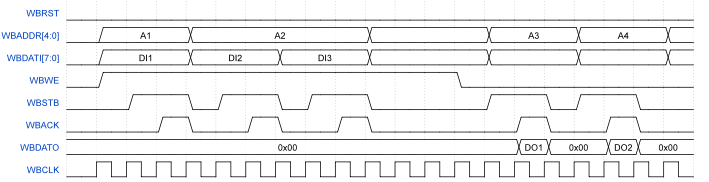

在Seal 系列FPGA中,動態調頻功能通過WISHBONE數據總線實現。用戶可以通過編程方式動態調整PLL的分頻系數,從而改變輸出時鐘的頻率。這一過程無需對FPGA工程進行反復編譯和配置,大大提高了開發效率。

WISHBONE數據總線時序

通過配置PLL的動態調頻功能,用戶可以根據系統需求實時調整時鐘頻率。例如,在無線通信系統中,可以根據信道切換的需求動態調整本地振蕩器的頻率,實現快速頻率跳變。

No.4展頻功能應用

展頻時鐘(Spread Spectrum Clocking, SSC)技術是一種通過動態調整時鐘頻率來降低電磁干擾(EMI)的方法。它將時鐘信號的頻譜能量分散到一定的頻率范圍內,從而降低在單一頻點上的峰值能量,減少電磁干擾。

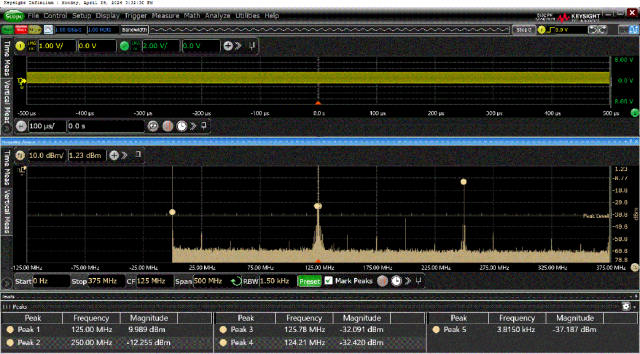

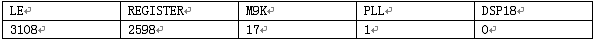

例如,在智多晶的SA5Z- 30 FPGA中,展頻功能通過PLL的精準分頻和動態配置實現。用戶可以通過編程方式動態調整PLL參數,從而改變輸出時鐘的頻率。通過周期性地調整這些參數,可以實現時鐘信號的展頻效果,可以有效降低時鐘信號的電磁干擾,提高系統的電磁兼容性。在高性能計算系統中,可以通過展頻技術減少時鐘信號對其他敏感電路的干擾,提高系統的整體穩定性。

沒有啟動SSC功能時,對125 MHz時鐘信號進行測試,此時看示波器FFT圖,可以看出時鐘頻率在125 MHz集中,容易產生電磁干擾(EMI)的風險。

未啟動展頻信號測試

SSC功能打開,測試展頻后的125 MHz時鐘信號,查看FFT圖,時鐘頻率分散在125 MHz附近,從而降低了電磁干擾(EMI)的風險。

啟動展頻信號測試

No.5結論

PLL技術在FPGA中的動態調頻與展頻功能應用為現代電子系統設計提供了強大的支持。通過靈活配置PLL參數,用戶可以實現實時調整時鐘頻率和降低電磁干擾的目標,滿足復雜系統對時鐘資源的高要求。隨著技術的不斷發展,PLL技術將在更多領域發揮重要作用,推動電子系統的性能提升和創新發展。

本文基于西安智多晶微電子有限公司提供的《AN05104_SA5Z-30 SA5Z-30 PLL展頻功能應用指導》和《AN05001_Seal 5000 FPGA PLL動態調頻應用指導》兩篇技術文檔編寫,技術文檔可在智多晶微電子有限公司官網進行查閱。希望本文能對您在FPGA設計和開發中有所幫助。如果對PLL在FPGA中的使用有疑問,歡迎咨詢西安智多晶微電子有限公司的技術支持團隊!

-

FPGA

+關注

關注

1644文章

21993瀏覽量

615296 -

濾波器

+關注

關注

162文章

8107瀏覽量

181342 -

pll

+關注

關注

6文章

888瀏覽量

136162 -

時鐘管理

+關注

關注

0文章

17瀏覽量

8437

原文標題:“芯”技術分享 | PLL技術在動態調頻與展頻功能的應用

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

XILINX FPGA IP之MMCM PLL DRP時鐘動態重配詳解

PLL技術在FPGA中的動態調頻與展頻功能應用

PLL技術在FPGA中的動態調頻與展頻功能應用

評論