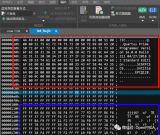

打開后的界面如下圖所示,全英文顯示。如果感覺自己的英文水平欠佳,可以使用谷歌瀏覽器打開該網頁,并選擇....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-23 10:33

?5561次閱讀

在做在線遠程升級的時候,一般需要兩步:1、將數據寫到外掛的flash中。2重新啟動FPGA配置。 不....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-23 10:24

?1995次閱讀

據《華爾街日報》最新報道,超微半導體(AMD)正就收購芯片制造商賽靈思(Xilinx)展開深入談判,....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-23 10:16

?2022次閱讀

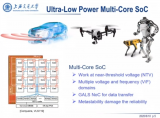

本文是一篇詳細介紹ISSCC2020會議上一篇有關亞穩態解決方案的文章,該技術也使得FPGA在較高頻....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-22 18:00

?4660次閱讀

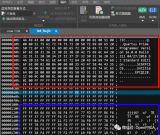

在基本的FPGA模塊編寫完成后,要使用仿真工具對設計的模塊進行仿真,驗證模塊的基本功能是否符合設計。....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-21 09:44

?2645次閱讀

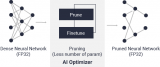

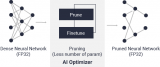

通過將 32 位浮點權值和激活量轉換為 INT8 這樣的定點,AI 量化器可在不影響預測精度的情況下....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-21 09:40

?4610次閱讀

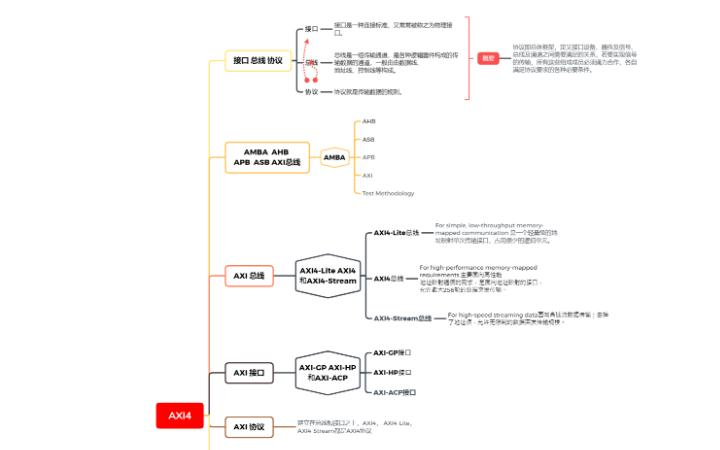

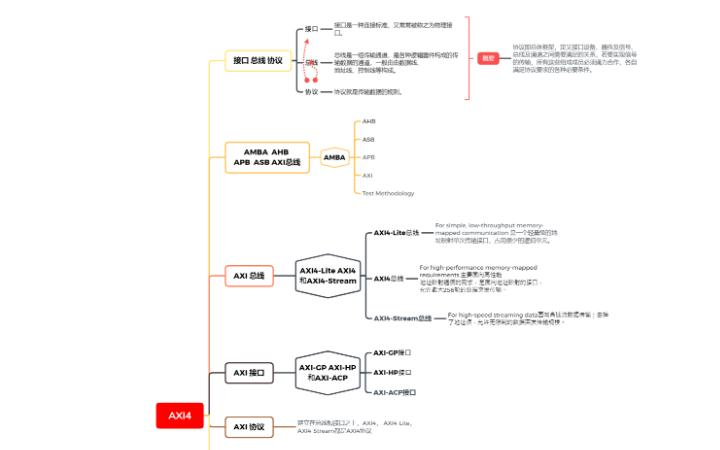

V1.0 ASB、APB是第一代AMBA協議的一部分。主要應用在低帶寬的外設上,如UART、 I2C....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-10 17:19

?3064次閱讀

很多工程師在使用Xilinx開發板時都注意到了一個問題,就是開發板中將LVDS的時鐘輸入(1.8V電....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 10-10 09:25

?12280次閱讀

總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。 總線是一組傳輸通道,是各....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-27 10:28

?6506次閱讀

作為一名程序員,與計算機打交道的日子不計其數,不管你玩硬件還是做軟件,你的世界自然都少不了計算機最核....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-27 10:10

?3525次閱讀

描述 在《Zynq UltraScale+ MPSoC 數據手冊》(DS925) 中,XAZU7EV....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-25 14:58

?6884次閱讀

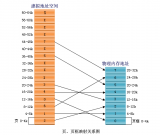

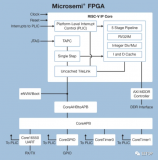

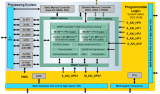

本文主要介紹CPLD和FPGA的基本結構。 CPLD是復雜可編程邏輯器件(Complex Progr....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-25 14:56

?13818次閱讀

從在2010年夏天,RISC-V項目啟動到今天已經整整十周年了。緊隨RISC-V十歲生日,讓我們來簡....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-25 14:52

?2800次閱讀

3線SPI的時鐘產生方式和上一篇的4線SPI相同,這里不在敘述。兩者的不同點在于:三線SPI模式需要....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:17

?7076次閱讀

無論實現讀還是寫功能,都先要提供SCLK。假如FPGA系統工作時鐘40MHz,我們可以利用計數器產生....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:15

?4014次閱讀

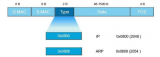

3線SPI與4線SPI配置的主要不同之處在傳輸的數據格式以及I/O轉換上。其讀寫數據格式由控制命令+....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:12

?7067次閱讀

從ads52j90的數據手冊我們不難發現,其SPI控制模塊主要包含4根信號線SEN,SCLK,SDI....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:09

?7083次閱讀

SDIO—當進行讀操作時,SDIO作為輸出口SDO,串行數據從ADC輸出,進入FPGA;當進行寫操作....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:07

?5495次閱讀

最熟悉的度量兩個量之間的相關性的方法是皮爾遜乘積矩相關系數(PPMCC),也稱為“皮爾遜相關系數”,....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-07 17:04

?27302次閱讀

近日,一名黑客公布了從英特爾竊取的 20GB芯片機密工程數據。這些數據可能會導致多個平臺的用戶面臨新....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-05 11:49

?3702次閱讀

同學們在學網絡課程的時候都知道,除巨幀外,常見的以太網幀的長度范圍是64字節到1518字節,并且因為....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-05 11:46

?8889次閱讀

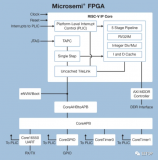

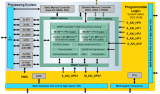

基于ZYNQ實現復雜嵌入式系統非常便利,其應用領域也越來越廣泛,本文來從對ZYNQ芯片架構的理解來談....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-05 11:44

?5064次閱讀

Linux 內存是后臺開發人員,需要深入了解的計算機資源。合理的使用內存,有助于提升機器的性能和穩定....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-01 10:46

?2622次閱讀

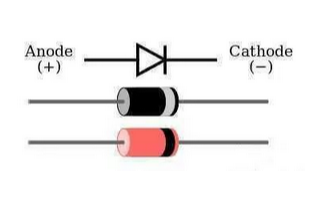

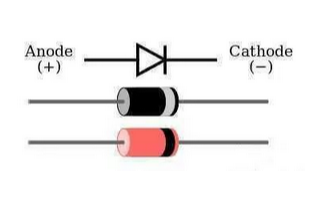

首先要開始這個話題要先說一下半導體。啥叫半導體? 半導體其實就是介于導體和絕緣體中間的一種東西,比如....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 08-25 17:41

?7044次閱讀

8月30日,中國移動副總裁李正茂在2019世界人工智能大會“5G與人工智能”主題論壇上表示,2019....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-01 10:20

?3680次閱讀

微軟小冰一直是比較特殊的人工智能產品。相較于其他助手型人工智能產品,以少女形態出現在人們面前的小冰,....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-01 10:09

?4979次閱讀

8月29日下午,LG Display宣布,其在廣州建設的8.5代OLED面板生產線正式投產。了解到該....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 09-01 09:51

?2945次閱讀

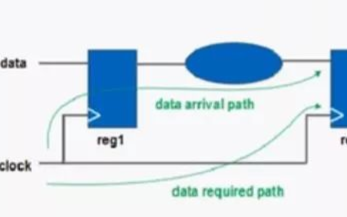

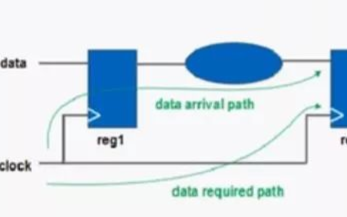

在輸入信號到輸出信號中,因為經過的傳輸路徑、寄存器、門電路等器件的時間,這個時間就是時序。開發工具不....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 07-31 14:50

?6685次閱讀

接著開始正文。據觀察,HLS的發展呈現愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 07-31 09:45

?7037次閱讀

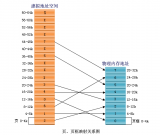

比如,一個16MB的程序和一個內存只有4MB的機器,OS通過選擇,可以決定各個時刻將哪4M的內容保留....

![的頭像]() FPGA之家 發表于

FPGA之家 發表于 07-28 09:56

?13677次閱讀