SPI(Serial Peripheral Interface),即串行外設(shè)接口。它是一種高速、全雙工的數(shù)據(jù)通信總線,并且在芯片的管腳只占4根線,節(jié)省芯片管腳的同時極大的方便了PCB的布局。正是由于這種簡單易用的特性,如今越來越多的芯片集成了該通信協(xié)議,比如我們經(jīng)常使用的ADC芯片。

目前,市面上絕大多數(shù)的ADC芯片都內(nèi)嵌專用的SPI配置接口,通過配置其SPI接口可以對ADC內(nèi)部的控制寄存器進行讀、寫操作,從而靈活的使用ADC芯片的各種功能。甚至對于某些ADC來說,如果不事先對其進行正確、有效的配置,則該ADC無法正常工作。

用于ADC配置的SPI接口分為4線模式(例如Analog Device的AD9639)和3線模式(Analog Device的AD9249)。對于4線模式來說,它有4根信號線,分別為:

SDI:Serial Data In

SDO:Serial Data Out

SCLK:Serial Clock

CS:Chip Select

3線模式與4線模式的不同之處在于SDI與SDO信號合并,稱為SDIO。另外,某些ADC的三線模式較為簡單,SDIO只用做輸入端口SDI(例如德州儀器的ADS5281芯片),沒有SDO的功能,實現(xiàn)起來較為簡單。

4線模式:

SDI—串行數(shù)據(jù)從FPGA輸出,進入ADC;

SDO—串行數(shù)據(jù)從ADC輸出,進入FPGA;

SCLK—時鐘信號從FPGA輸出,進入ADC;

CS—ADC使能信號從FPGA輸出,進入ADC;

3線模式:

SDIO—當進行讀操作時,SDIO作為輸出口SDO,串行數(shù)據(jù)從ADC輸出,進入FPGA;當進行寫操作時,SDIO作為輸入口SDI,串行數(shù)據(jù)從FPGA輸出,進入ADC;

SCLK—時鐘信號從FPGA輸出,進入ADC;

CS—ADC使能信號從FPGA輸出,進入ADC;

3線模式和4線模式相比,表面上看只是少了1根信號線,實際上在讀寫操作時,涉及到了ADC端與FPGA端的SDIO接口的三態(tài)轉(zhuǎn)換控制,這點需要大家特別注意。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21957瀏覽量

614038 -

adc

+關(guān)注

關(guān)注

99文章

6637瀏覽量

548239 -

SPI

+關(guān)注

關(guān)注

17文章

1782瀏覽量

94707

原文標題:FPGA通過SPI對ADC配置簡介(一)----- 什么是SPI?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何使用Tresos for S32K344通過SPI配置DMA?

Java的SPI機制詳解

AN-878: 高速ADC SPI控制軟件[中文版]

![AN-878: 高速<b class='flag-5'>ADC</b> <b class='flag-5'>SPI</b>控制軟件[中文版]](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

FPGA通過SPI對DAC進行了配置,用頻譜儀測不到輸出是怎么回事?

使用FPGA與DAC53202進行通訊,通過SPI配置DAC但是讀取失敗了,為什么?

能否在純fpga上通過verilog實現(xiàn)SPI控制器去配置adc12dj3200?

spi master接口的fpga實現(xiàn)

采用Xilinx FPGA的AFE79xx SPI啟動指南

ADC3663的SPI配置管腳連接至FPGA時遇到IO電平不匹配怎么解決?

LMK04821NKDT通過SPI無法配置是怎么回事?

PCM5142如何在FPGA中通過SPI配置寄存器?

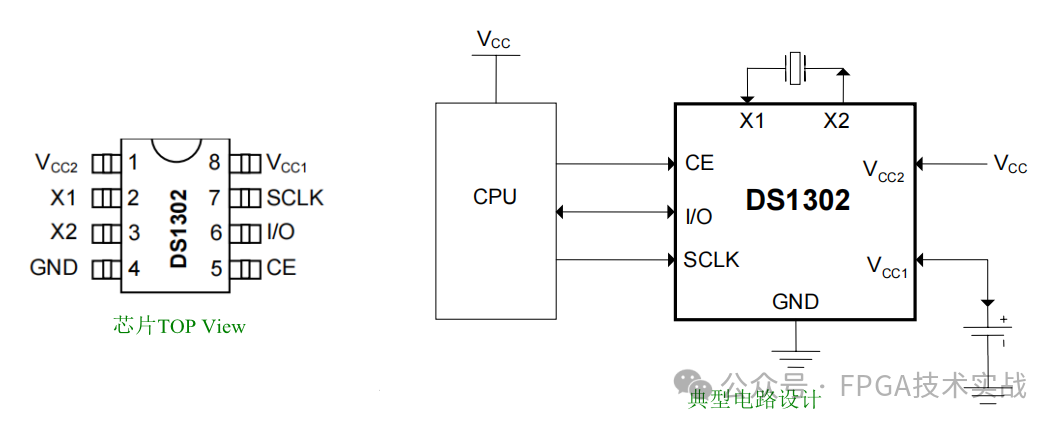

DS1302芯片與FPGA之間SPI通信原理

單片機SPI通信實現(xiàn)

【GD32H757Z海棠派開發(fā)板使用手冊】第十一講 SPI-SPI NOR FLASH讀寫實驗

Vision Board上的SPI設(shè)備驅(qū)動配置和SPI主控的外部loopback功能測試

FPGA通過SPI對ADC配置簡介-----什么是SPI?

FPGA通過SPI對ADC配置簡介-----什么是SPI?

評論