統(tǒng)計(jì)嵌入式代碼覆蓋率的方法和經(jīng)驗(yàn)

代碼覆蓋率是衡量軟件測(cè)試完成情況的指標(biāo),通常基于測(cè)試過(guò)程中已檢查的程序源代碼比例計(jì)算得出。代碼覆蓋率....

如何理解和使用做FPGA設(shè)計(jì)時(shí)的過(guò)約束?

有人希望能談?wù)勗谧鯢PGA設(shè)計(jì)的時(shí)候,如何理解和使用過(guò)約束。我就以個(gè)人的經(jīng)驗(yàn)談?wù)劊?什么是過(guò)約束; ....

C代碼常用校驗(yàn)方法函數(shù)介紹

01 前言 在項(xiàng)目開(kāi)發(fā)中,通常會(huì)用到一些通用或者經(jīng)常使用的工具函數(shù)或者計(jì)算函數(shù),一般我都會(huì)把這些函數(shù)....

如何寫(xiě)一個(gè)簡(jiǎn)易AM信號(hào)的FPGA實(shí)現(xiàn)?

前幾天,臨危受命,幫幾個(gè)初學(xué)者的學(xué)生寫(xiě)一個(gè)簡(jiǎn)易AM信號(hào)的FPGA實(shí)現(xiàn),以幫助他們搭建一個(gè)相對(duì)完整的系....

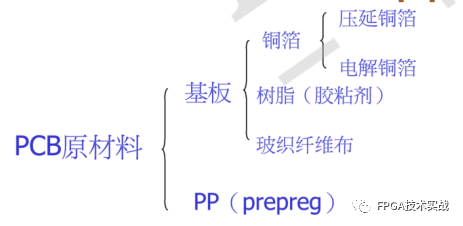

FPGA PCB設(shè)計(jì)如何選擇傳輸介質(zhì)?

引言:傳輸介質(zhì)的選擇,無(wú)論是PCB材料還是電纜類(lèi)型,都會(huì)對(duì)系統(tǒng)性能產(chǎn)生很大的影響。盡管任何傳輸介質(zhì)在....

如何讓自己創(chuàng)建的tcp協(xié)議棧為其他應(yīng)用程序提供網(wǎng)絡(luò)服務(wù)?

一般來(lái)說(shuō),使用套接字進(jìn)行網(wǎng)絡(luò)編程時(shí),默認(rèn)使用linux內(nèi)核提供的網(wǎng)絡(luò)服務(wù)。但是,現(xiàn)在我們自己在用戶(hù)空....

Xilinx 7系列FPGA PCB的設(shè)計(jì)指導(dǎo)

引言:傳輸線沿其長(zhǎng)度定義并控制特性阻抗。然而,它們接口的三維結(jié)構(gòu)在信號(hào)路徑上沒(méi)有容易定義的或恒定的阻....

C語(yǔ)言u(píng)thash簡(jiǎn)介的使用

1. uthash簡(jiǎn)介 2. uthash的使用 2.1 定義結(jié)構(gòu)體 2.2 添加 2.3 查找 2....

CERN如何使用深度學(xué)習(xí)和英特爾oneAPI加速蒙特卡洛模擬介紹

獨(dú)立顧問(wèn) James Reinders 剛剛在 NextPlatform.com 網(wǎng)站上發(fā)表了題為“....

VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)

前年,發(fā)表了一篇文章《VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)》(鏈接在參考資料1),里面簡(jiǎn)....

Xilinx 7系列FPGA時(shí)鐘和前幾代有什么差異?

引言:從本文開(kāi)始,我們陸續(xù)介紹Xilinx 7系列FPGA的時(shí)鐘資源架構(gòu),熟練掌握時(shí)鐘資源對(duì)于FPG....

計(jì)算機(jī)中的高速緩存詳解

1. 什么是緩存??緩存又叫高速緩存,是計(jì)算機(jī)存儲(chǔ)器中的一種,本質(zhì)上和硬盤(pán)是一樣的,都是用來(lái)存儲(chǔ)數(shù)據(jù)....

如何用C語(yǔ)言實(shí)現(xiàn)MD5加密?

一、摘要算法 摘要算法又稱(chēng)哈希算法。 它表示輸入任意長(zhǎng)度的數(shù)據(jù),輸出固定長(zhǎng)度的數(shù)據(jù),它的主要特征是加....

Xilinx 7系列中FPGA架構(gòu)豐富的時(shí)鐘資源介紹

引言:7系列FPGA具有多個(gè)時(shí)鐘路由資源,以支持各種時(shí)鐘方案和要求,包括高扇出、短傳播延遲和極低的偏....

SpinalHDL里時(shí)鐘域中的定制與命名

聊一聊在SpinalHDL里時(shí)鐘域中時(shí)鐘的定制與命名。 相較于Verilog,在SpinalHDL里....

FPGA架構(gòu)中的全局時(shí)鐘資源介紹

引言:本文我們介紹一下全局時(shí)鐘資源。全局時(shí)鐘是一個(gè)專(zhuān)用的互連網(wǎng)絡(luò),專(zhuān)門(mén)設(shè)計(jì)用于到達(dá)FPGA中各種資源....

RAM的Parity與ECC概念和實(shí)現(xiàn)

RAM的 Parity 與 ECC 一、概念介紹 1.1 Parity的概念 Parity,即奇偶校....

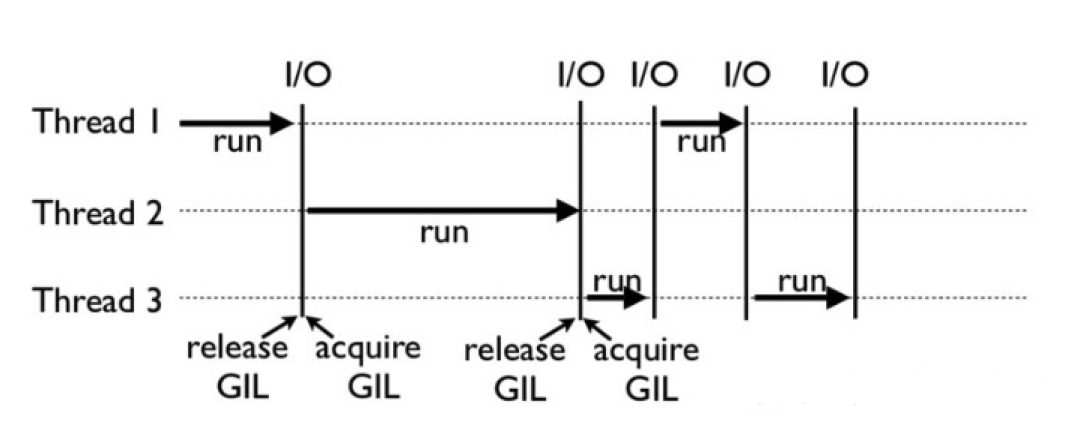

GIL在CPython解釋器中的工作原理是什么?

我是一個(gè)Python線程,我的工作就是解釋執(zhí)行程序員編寫(xiě)的Python代碼。 之所以說(shuō)是解釋執(zhí)行,是....

Xilinx 7系列FPGA架構(gòu)的區(qū)域時(shí)鐘資源介紹

引言:本文我們介紹區(qū)域時(shí)鐘資源。區(qū)域時(shí)鐘網(wǎng)絡(luò)是獨(dú)立于全局時(shí)鐘的時(shí)鐘網(wǎng)絡(luò)。不像全局時(shí)鐘,一個(gè)區(qū)域時(shí)鐘信....

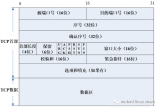

tcp數(shù)據(jù)包接口封裝的介紹

TCP報(bào)文格式 TCP協(xié)議有著自己的數(shù)據(jù)包格式,這里把TCP的數(shù)據(jù)包稱(chēng)為報(bào)文段(segment),T....

英特爾異構(gòu)3D系統(tǒng)級(jí)封裝集成

異構(gòu) 3D 系統(tǒng)級(jí)封裝集成 3D 集成與封裝技術(shù)的進(jìn)步使在單個(gè)封裝(包含采用多項(xiàng)技術(shù)的芯片)內(nèi)構(gòu)建復(fù)....

FPGA的選型策略有哪些?

引言:FPGA作為數(shù)字電路三大基石之一,其選型的好壞決定了產(chǎn)品的成本、項(xiàng)目研發(fā)效率、產(chǎn)品上市時(shí)間、產(chǎn)....

double buffer的fbdev驅(qū)動(dòng)與應(yīng)用

由于存在競(jìng)爭(zhēng)關(guān)系且讀寫(xiě)沒(méi)有同步機(jī)制,framebuffer 里必須會(huì)發(fā)生同時(shí)存在frame N 和 ....

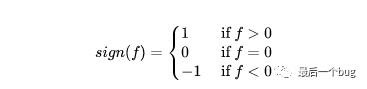

信號(hào)波峰波谷的用處與檢測(cè)方法及實(shí)戰(zhàn)

對(duì)于信號(hào)波峰波谷識(shí)別在嵌入式領(lǐng)域應(yīng)該是非常廣泛的,因?yàn)榇蟛糠值男盘?hào)都處于一種時(shí)變的狀態(tài),信號(hào)在時(shí)域上....

陶瓷PCB板的介紹與優(yōu)缺點(diǎn)及用途

在PCB加工過(guò)程中由于熱應(yīng)力、化學(xué)因素、生產(chǎn)工藝不當(dāng)?shù)仍颍蛘呤窃谠O(shè)計(jì)過(guò)程中由于兩面鋪銅不對(duì)稱(chēng),很....

關(guān)于PHY的三大寄存器詳解

STM32只有網(wǎng)絡(luò)外設(shè)時(shí)不能進(jìn)行網(wǎng)絡(luò)通信的,因?yàn)镾TM32只提供了SMI接口,MII和RMII接口。

關(guān)于BDC碼的介紹與最常用的方法

在使用RTC外設(shè)時(shí),我們常常會(huì)接觸 BCD碼的概念,同時(shí)魚(yú)鷹在介紹 USB 協(xié)議版本時(shí)也說(shuō)了 BCD....

機(jī)器人是如何實(shí)現(xiàn)自我編程的?與大批量/小批量生產(chǎn)的AI

幾十年來(lái),機(jī)器人技術(shù)的故事一直是一樣的:您需要大量的批量生產(chǎn)才能獲得任何收益。在許多領(lǐng)域,機(jī)器人技術(shù)....

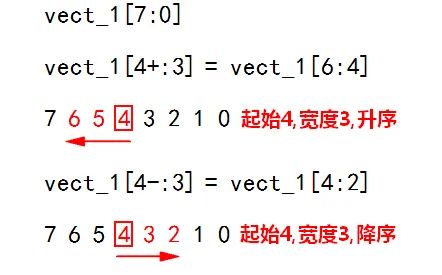

關(guān)于Verilog語(yǔ)法你不知道的方法

Verilog比較方便的一個(gè)特點(diǎn)就是數(shù)據(jù)的截取和拼接功能了,截取使用方括號(hào)[],拼接使用大括號(hào){}。