聊一聊在SpinalHDL里時鐘域中時鐘的定制與命名。

相較于Verilog,在SpinalHDL里,其對時鐘域有著更細致的描述,從而也能夠更精細的控制和描述。而對于時鐘域,我們往往關系的是:

時鐘頻率

復位電平:是高電平還是低電平

復位方式,是同步復位還是異步復位。

對于帶有時序電路的邏輯而言,最常用的生成Verilog代碼方式如下:

時鐘域默認為異步高電平復位:

倘若要“定制”時鐘域,那么往往采用下面的方式生成RTL代碼:

這里在SpinalConfig里常用的用于“定制”時鐘的有兩個參數:

defaultConfigForClockDomains

defaultClockDomainFrequency

defaultConfigForClockDomains參數可指定時鐘域的配置,ClockDomainConfig中可指定的參數包含:

clockEdge:指定有效時鐘沿(RISING、FALLING)

resetKind: 指定復位類型(ASYNC、SYNC)

resetActiveLevel: 指定復位類型(HIGH,LOW)

softResetActiveLevel:指定softReset類型(HIGH,LOW)

clockEnableActiveLevel: 指定時鐘使能信號電平(HIGH,LOW)

上述代碼最終生成的RTL為:

可以看到,復位信號變成了同步高電平復位形式。通過這種時鐘域配置的方式,可以做到一鍵修改適配,從而避免一遍又一遍的posedge、negedge啰嗦~,同時又避免自己在繁雜的Verilog代碼里手誤(真實遇到過別人代碼里復位一會兒posedge、一會兒negedge、估計是寫懵了)。

而defaultClockDomainFrequency則用于指定時鐘頻率,當你的代碼里若調用類似這樣的lib函數那么指定時鐘頻率就尤為重要了:

val timeout = Timeout(10 ms) //Timeout who tick after 10 mswhen(timeout){ //Check if the timeout has tick timeout.clear() //Ask the timeout to clear its flag}》》時鐘重命名

在當前的開發模式下,很難做到每個人都使用SpinalHDL,而當牽涉到多人合作時,時鐘與復位信號的命名往往需達成一致,通過下面的方式可以修改默認時鐘域的信號命名:

對應的RTL:

更通用一些,也可以根據復位信號的特征來指定名稱:

原文標題:時鐘域“定制”

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1645文章

22036瀏覽量

618106 -

時鐘

+關注

關注

11文章

1898瀏覽量

133191

原文標題:時鐘域“定制”

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

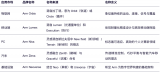

旺詮合金電阻的命名規則

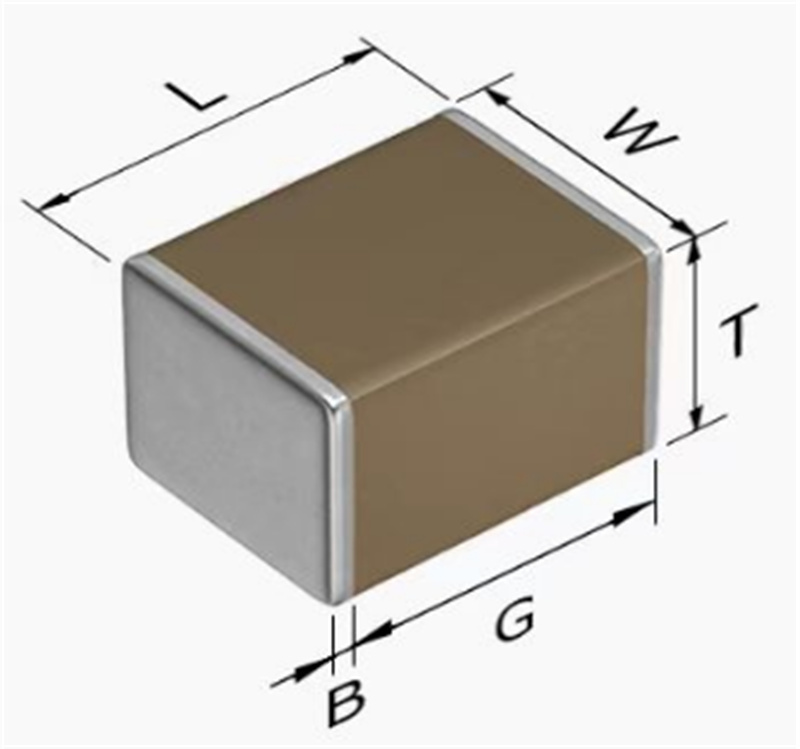

順絡貼片電容規格都是怎么命名的

是否可以在沒有RTC時鐘輸入的情況下在基于LS1043的定制板上使看門狗正常工作?

風華電容命名方法深度解析

ads7882里面的RD是不是一個同步用的時鐘脈沖?

時序約束一主時鐘與生成時鐘

貼片共模電感的命名規格、特征及應用

臺灣華科貼片電容的命名及封裝

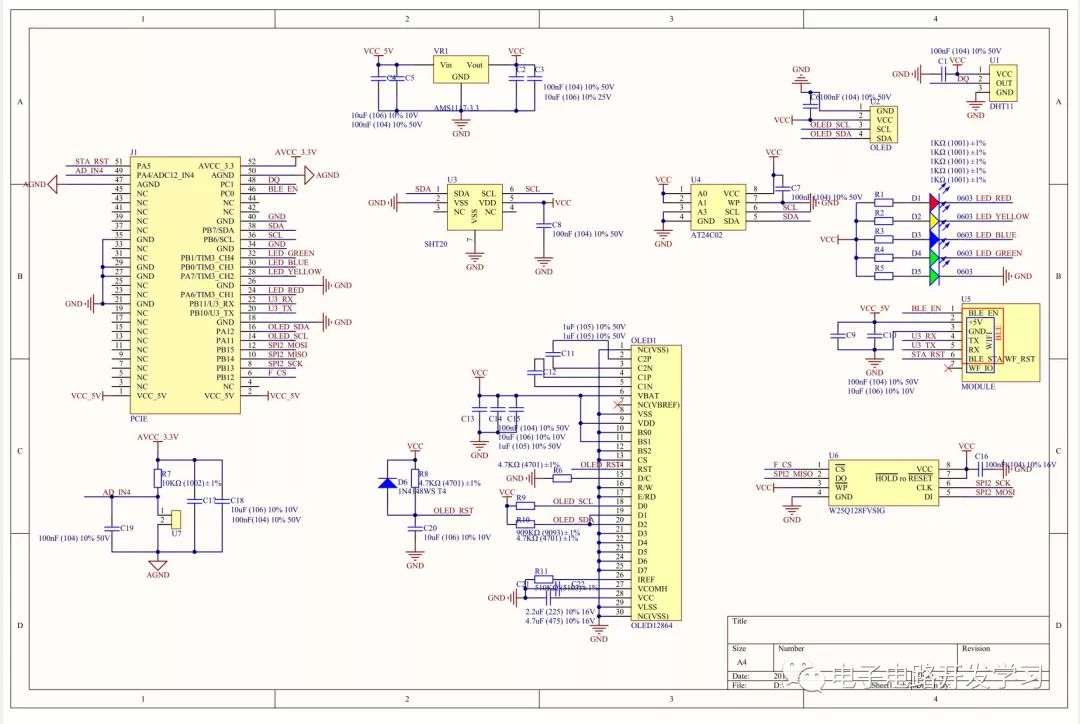

基于STM32的WiFi聯網自動校準時鐘設計

SpinalHDL里時鐘域中的定制與命名

SpinalHDL里時鐘域中的定制與命名

評論