三星電子宣布開(kāi)發(fā)了業(yè)內(nèi)首款容量達(dá)到512GB的DDR5內(nèi)存模組

Intel副總裁Carolyn Duran確認(rèn),三星的新款DDR5內(nèi)存和下一代至強(qiáng)可擴(kuò)展處理器(Sa....

Xilinx將可能以哪種方式影響AMD的未來(lái)業(yè)務(wù)和戰(zhàn)略?

作為去年的重大收購(gòu)之一,AMD收購(gòu)Xilinx將對(duì)電子行業(yè)的合并產(chǎn)生重大影響。在閱讀他們關(guān)于合并的介....

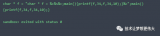

淺談Python中的opencv

作為時(shí)下最時(shí)尚的python語(yǔ)言,簡(jiǎn)潔的代碼,借助于向軍火庫(kù)一般的各種開(kāi)源工具包,你可以完成你想做的....

Sapphire Rapids對(duì)應(yīng)第四代至強(qiáng)可擴(kuò)展處理器預(yù)計(jì)今年底登場(chǎng)

在爆料Up主Moore’s Law Is Dead的最新視頻中,他探聽(tīng)到了Intel神秘新項(xiàng)目,隸屬....

關(guān)于CPU運(yùn)行速度計(jì)算詳解

相對(duì)人的感官來(lái)說(shuō)CPU跑的太快了——即便是人們常常用來(lái)描述時(shí)間短暫的“一眨眼功夫”對(duì)CPU來(lái)說(shuō)也是及....

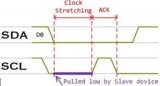

從IIC實(shí)測(cè)波形入手,去理解IIC的通信原理

玩單片機(jī)的朋友都知道IIC通信這個(gè)工具,但好多人只是會(huì)用,內(nèi)部的原理不求甚解,或是想要了解其原理,但....

探討有關(guān)AXIIIC和PSIIC的自調(diào)試技巧

“IIC 協(xié)議與編程序列” 一文,我們?yōu)閮?nèi)部集成電路 (IIC) 協(xié)議的初學(xué)者們提供了有關(guān)該協(xié)議基礎(chǔ)....

剖析STM32的FLASH和SRAM的使用情況

01前言 STM32片上自帶FLASH和SRAM,簡(jiǎn)單講FLASH用來(lái)存儲(chǔ)程序的,SRAM是用來(lái)存儲(chǔ)....

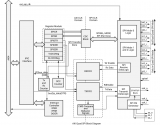

怎么樣利用AXI Quad SPI快速打通Linux至PL端SPI從設(shè)備?

[導(dǎo)讀] 前面寫(xiě)過(guò)篇介紹ZYNQ基本情況的文章,今天來(lái)肝一篇實(shí)戰(zhàn)文章介紹AXI quad SPI 使....

如何在Vmware虛擬機(jī)上搭建Ubuntu Linux開(kāi)發(fā)環(huán)境詳解

對(duì)于剛接觸嵌入式 Linux 系統(tǒng)開(kāi)發(fā)的同學(xué)來(lái)說(shuō),搭建開(kāi)發(fā)環(huán)境是一個(gè)不小的挑戰(zhàn),我看到過(guò)很多在入門(mén)邊....

淺析嵌入式開(kāi)發(fā)五種存儲(chǔ)方式

RAM通常都是在掉電之后就丟失數(shù)據(jù),如計(jì)算機(jī)的內(nèi)存條就是RAM,關(guān)機(jī)后內(nèi)存數(shù)據(jù)被自動(dòng)清空。

教你們STM32如何收發(fā)float類(lèi)型數(shù)據(jù)

實(shí)際應(yīng)用中,我們可能需要兩個(gè)設(shè)備通過(guò)串口傳輸浮點(diǎn)數(shù)據(jù): 本篇筆記為了方便演示,使用串口助手模擬其中一....

在SpinalHDL中如何優(yōu)雅地實(shí)現(xiàn)寄存器總線讀寫(xiě)

在SpinalHDL里,其Libraries里提供了關(guān)于總線相關(guān)的庫(kù)。包含AMBA3、AMBA4、A....

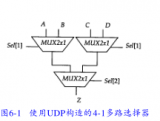

Verilog HDL指定用戶(hù)定義原語(yǔ)U D P的能力

定義U D P。U D P只能有一個(gè)輸出和一個(gè)或多個(gè)輸入。第一個(gè)端口必須是輸出端口。此外,輸出可以取....

為什么要為開(kāi)源重新構(gòu)建FINN?

2020 年 5 月,賽靈思研究實(shí)驗(yàn)室的論文《FINN-R:快速探索量化神經(jīng)網(wǎng)絡(luò)的端到端深度學(xué)習(xí)框架....

C語(yǔ)言指針到應(yīng)用層的各種指針使用技巧

那么,我們定義一個(gè)變量之后,這個(gè)變量放在哪里呢?那就是內(nèi)存的數(shù)據(jù)區(qū)。內(nèi)存是一個(gè)很大的存儲(chǔ)區(qū)域,被操作....

軟件無(wú)線電技術(shù)中的關(guān)鍵技術(shù)——軟件無(wú)線電的架構(gòu)

軟件無(wú)線電(SDR)最初的概念是一種通信技術(shù)或者體系結(jié)構(gòu),而現(xiàn)在SDR,確切地說(shuō)是軟件定義無(wú)線電,更....

簡(jiǎn)要地學(xué)習(xí)x86硬件體系,為閱讀linux0.12內(nèi)核源碼掃清障礙

程序我已經(jīng)打包好放在自己的服務(wù)器上,倘若你手上有Ubuntu系統(tǒng)的話(huà),相信不用五分鐘你就可以在你的p....

解密英特爾? Agilex? FPGA家族的八大特性

數(shù)字經(jīng)濟(jì)的快速發(fā)展催生了海量數(shù)據(jù)需求,現(xiàn)代企業(yè)需要出色的解決方案幫助整合和處理不斷激增的數(shù)據(jù)流量。而....

如何去正確理解采樣時(shí)鐘抖動(dòng)(Jitter)對(duì)ADC信噪比SNR的影響

前言 :本文我們介紹下ADC采樣時(shí)鐘的抖動(dòng)(Jitter)參數(shù)對(duì)ADC采樣的影響,主要介紹以下內(nèi)容:....

嵌入式系統(tǒng)中常用的IIC與SPI該怎么選?

現(xiàn)今,在低端數(shù)字通信應(yīng)用領(lǐng)域,我們隨處可見(jiàn)IIC(Inter-Integrated Circuit)....

Xilinx FPGA收發(fā)器參考時(shí)鐘設(shè)計(jì)要求與軟件配置及結(jié)果測(cè)試

晶振是數(shù)字電路設(shè)計(jì)中非常重要的器件,時(shí)鐘的相位噪聲、頻率穩(wěn)定性等特性對(duì)產(chǎn)品性能影響很大。本文基于可編....

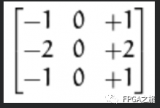

關(guān)于FPGA中Sobel的簡(jiǎn)介與實(shí)現(xiàn)

一句話(huà)可以概況為,分別求水平與豎直梯度,然后求平方和再開(kāi)方(近似的話(huà)就直接求絕對(duì)值之和),最后與設(shè)定....

5G時(shí)代對(duì)FPGA的影響與挑戰(zhàn)?

在最近的一篇博客文章“FPGA In the 2020 - the New Old Thing”中,....

單片機(jī)中為什么軟件能控制硬件?

我們通過(guò)IO和串口的軟件開(kāi)發(fā),已經(jīng)體驗(yàn)了嵌入式軟件開(kāi)發(fā)。不知道大家有沒(méi)有疑惑,為什么軟件能控制硬件?....

你有見(jiàn)到過(guò)最美的c語(yǔ)言代碼嗎?

我們都知道雷軍雷布斯說(shuō)過(guò)當(dāng)時(shí)他寫(xiě)的代碼像詩(shī)一樣優(yōu)美,那已經(jīng)是三十年前的匯編時(shí)代了,那么現(xiàn)在你有見(jiàn)到過(guò)....

PCIe中三種基本的I/O架構(gòu)

導(dǎo)言:這篇為PCIe要提及的時(shí)鐘類(lèi)型作個(gè)小鋪墊,可以大致作一個(gè)了解,想深入了解可以參考更加細(xì)致的文獻(xiàn)....