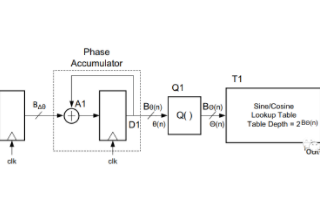

如何基于DDS IP實現(xiàn)線性調(diào)頻信號

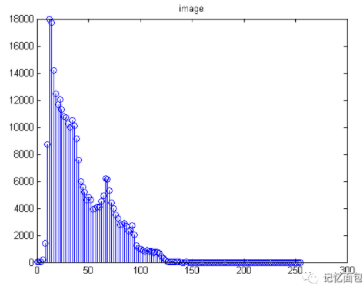

利用DDS IP實現(xiàn)線性調(diào)頻信號 1 DDS技術(shù)簡介隨著電子技術(shù)的不斷發(fā)展,傳統(tǒng)的頻率合成技術(shù)逐漸不....

基于FPGA的DDS IP實現(xiàn)線性調(diào)頻信號的設(shè)計方案

利用DDS IP實現(xiàn)線性調(diào)頻信號1 DDS技術(shù)簡介隨著電子技術(shù)的不斷發(fā)展,傳統(tǒng)的頻率合成技術(shù)逐漸不能....

Verilog HDL語言中任務與函數(shù)的比較

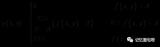

其中,返回值的類型和位寬是可選項,如果缺省會返回一位寄存器類型數(shù)據(jù)。Verilog HDL認為函數(shù)的....

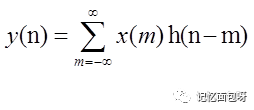

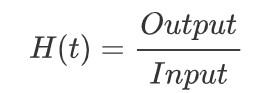

什么是零點和極點?時域上系統(tǒng)穩(wěn)定性和S域的穩(wěn)定性有什么關(guān)系?

PID是十分優(yōu)美的控制算法,在工業(yè)控制應用地十分廣泛,有的時候,無需知道系統(tǒng)模型的情況下,只要經(jīng)驗法....

如何利用Vivado集成開發(fā)環(huán)境進行FPGA的應用開發(fā)

隨著5G、AI、航天等領(lǐng)域迅猛發(fā)展,高速信號處理需求日益突出,硬件加速勢在必行。異構(gòu)多核架構(gòu)近年來得....

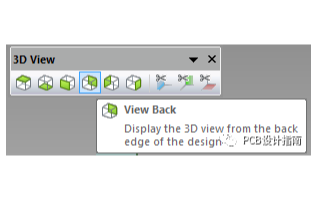

利用3D Layout解決PCB設(shè)計流程集成到機電設(shè)計的難題

Xpedition/PADS Professional Layout 為 PCB 設(shè)計人員提供了通過....

你們知道always,assign和always@(*)之間的區(qū)別嗎

1.always@后面內(nèi)容是敏感變量,always@(*)里面的敏感變量為*,意思是說敏感變量由綜合....

XILINX FPGA的硬件設(shè)計總結(jié)之PCIE硬件設(shè)計避坑指南

隨著FPGA的不斷發(fā)展,F(xiàn)PGA本身自帶的PCIE硬核的數(shù)量越來越多,本文以ZU11EG為例介紹,如....

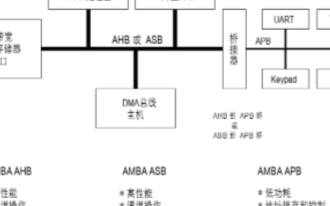

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

什么是AMBA? 現(xiàn)如今,集成電路芯片的規(guī)模越來越大。數(shù)字IC從基于時序驅(qū)動的設(shè)計方法,發(fā)展到基于I....

Verilog設(shè)計過程中狀態(tài)機的設(shè)計方法

“本文主要分享了在Verilog設(shè)計過程中狀態(tài)機的一些設(shè)計方法。 關(guān)于狀態(tài)機 狀態(tài)機本質(zhì)是對具有邏輯....

如何在VScode中自動生成Verilog仿真文件

一、實現(xiàn)功能 1、可以自動創(chuàng)建文件夾 2、根據(jù)Verilog文件自動生成測試文件模板(TB文件名字是....

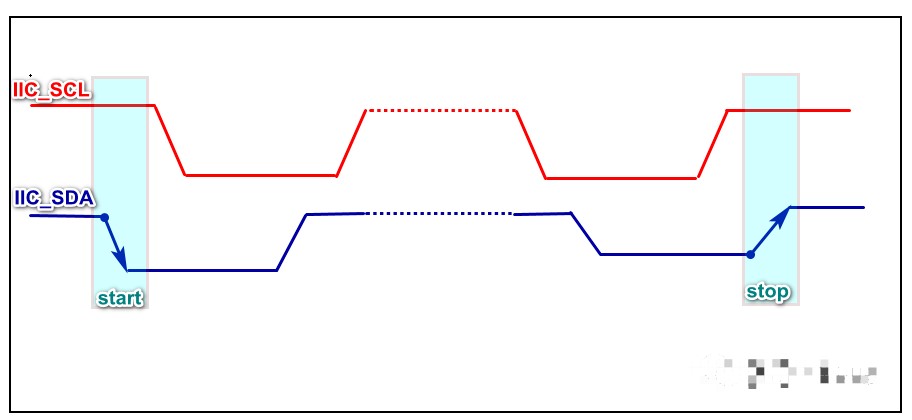

SPI、UART、IIC總線之間有什么區(qū)別與聯(lián)系

SPI 總線 SPI(Serial Peripheral Interface,串行外設(shè)接口)是一種高....

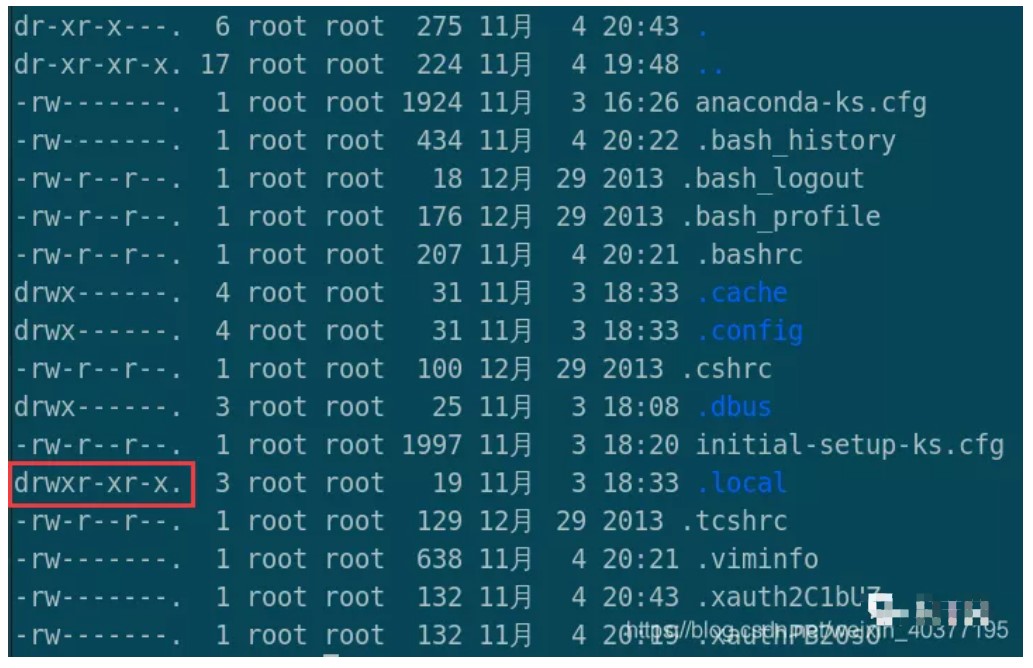

Linux中的軟鏈接、硬鏈接都用在哪些場合?

最近,看到很多文章都在介紹 Linux 中的文件系統(tǒng),其中就包括:inode 節(jié)點、軟鏈接、硬鏈接等....

Zynq-7000系列可編程邏輯PL是什么?

剛學ZYNQ的時候,看到里面反復提到PS和PL,還以為PS是PhotoShop的意思,PL是哪種型號....

芯片技術(shù)中就有了“層”的概念是什么?

前言:集成電路(芯片)是用光刻為特征的制造工藝,一層一層制造而成。所以,芯片技術(shù)中就有了“層”的概念....

芯片能屯一堆十年后暴漲再賣掉嗎?

何止?jié)q 5 倍,聽說有的 MCU 都漲了幾十倍。所以有人建議多囤點芯片,十年后再賣。酒越存越香,股票....

時序問題常見的跨時鐘域亞穩(wěn)態(tài)問題

今天寫一下時序問題常見的跨時鐘域的亞穩(wěn)態(tài)問題。 先說明一下亞穩(wěn)態(tài)問題: D觸發(fā)器有個明顯的特征就是建....

Verilog的兩種塊語句解析

1. 塊語句有兩種,一種是 begin-end 語句, 通常用來標志()執(zhí)行的語句;一種是 fork....

將FPGA集成進SoC的好處顯而易見

FPGA以其強大的靈活性和適應性見長。系統(tǒng)設(shè)計師在設(shè)計大容量復雜應用時,越來越多的考慮使用SoC中集....