KEIL 調(diào)試方法經(jīng)驗(yàn)總結(jié)

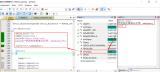

我們已經(jīng)了解了很多的 KEIL 調(diào)試方法,但是到底該怎么使用這些方法呢?這篇文章將介紹個(gè)人的調(diào)試經(jīng)驗(yàn)....

Vivado調(diào)用Questa Sim或ModelSim仿真小技巧

Vivado調(diào)用Questa Sim或ModelSim仿真中存在的一些自動(dòng)化問題的解決方案。 Viv....

開發(fā)板KC705設(shè)計(jì)中涉及到兩個(gè)時(shí)鐘域問題

Q1 背景: 軟件 vivado2018.2 開發(fā)板 KC705 設(shè)計(jì)中涉及到兩個(gè)時(shí)鐘域(外部提供的....

芯片RTL設(shè)計(jì)中如何做到低功耗設(shè)計(jì)

做芯片第一應(yīng)該關(guān)注的是芯片的PPA(Performance, Power, Area),本篇淺顯的部....

FPGA外設(shè)DDR2/DDR3硬件設(shè)計(jì)相關(guān)內(nèi)容

引言:本文我們介紹FPGA外設(shè)DDR2/DDR3硬件設(shè)計(jì)相關(guān)內(nèi)容,包括PCB板層數(shù)估計(jì),信號(hào)端接、信....

Verilog中四個(gè)基礎(chǔ)的時(shí)序分析

下列 時(shí)序檢查語句 錯(cuò)誤的是() A. $setup(posedge clk, data, tSU)....

數(shù)字電路設(shè)計(jì)中跨時(shí)鐘域處理的亞穩(wěn)態(tài)

數(shù)字電路設(shè)計(jì)中遇到跨時(shí)鐘域(Clock Domain Crossing, CDC)的電路時(shí)一般都需要....

你們會(huì)設(shè)計(jì)CPU取指執(zhí)行電路嗎?

【前言】 最近手上寫了一個(gè)練手的小項(xiàng)目,項(xiàng)目的大致要求是實(shí)現(xiàn)一個(gè)取指,執(zhí)行電路。取指的指令預(yù)存在,從....

如何使用Icarus Verilog+GTKWave來進(jìn)行verilog文件的編譯和仿真

本文將介紹如何使用Icarus Verilog+GTKWave來進(jìn)行verilog文件的編譯和仿真。....

示波器直連電腦波形讀取教程

最近在使用示波器測(cè)一些波形數(shù)據(jù),需要保存記錄,以前通常是使用U盤的方式來存波形數(shù)據(jù),然后拿到電腦端去....

教大家在Vivado中FFT IP調(diào)配置及應(yīng)用

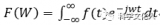

01 FFT簡(jiǎn)介 快速傅里葉變換 (Fast Fourier Transform,F(xiàn)FT), 即利用....

SERDES的優(yōu)勢(shì) SERDES演變的看法

SERDES的優(yōu)勢(shì) 引腳數(shù)量和通道優(yōu)勢(shì) SERDES最明顯的優(yōu)勢(shì)是具備更少的引腳數(shù)量和線纜/通道數(shù)量....

基于ModelSim使用modelsim手動(dòng)時(shí)序仿真教程

時(shí)序仿真與功能仿真的步驟大體相同,只不過中間需要添加仿真庫、網(wǎng)表(.vo)文件和延時(shí)(.sdo)文件....

為什么串行接口(以SERDES為代表)變得如此流行

盡管SERDES(SERializer/DESerializer)擁有十分復(fù)雜的設(shè)計(jì)和驗(yàn)證過程,但已....

基于ModelSim使用四ModelSim手動(dòng)仿真教程

4.1 新建仿真工程 在開始動(dòng)手仿真之前,首先,我們需要?jiǎng)?chuàng)建一個(gè)文件夾用來放置我們的 ModelSi....

簡(jiǎn)述FPGA中亞穩(wěn)態(tài)的產(chǎn)生機(jī)理及其消除方法

亞穩(wěn)態(tài)的概念 亞穩(wěn)態(tài)是指觸發(fā)器無法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)引時(shí)....

基于ModelSim使用二聯(lián)合Quarus自動(dòng)仿真教程

3 ModelSim工程實(shí)戰(zhàn)之自動(dòng)仿真說完了 ModelSim 的使用流程,接下來我們將會(huì)對(duì)每個(gè)流程....

給大家分享一個(gè)非常簡(jiǎn)單的IO輸入輸出框架

在一個(gè)嵌入式系統(tǒng)中,可能存在許多輸入或輸出的IO口,輸入有霍爾傳感器、紅外對(duì)管等,輸出有LED、電源....

解析CPU究竟是怎么執(zhí)行一條指令的?

【Linux 從頭學(xué)】是什么這兩年多以來,我的本職工作重心一直是在 x86 Linux 系統(tǒng)這一塊,....

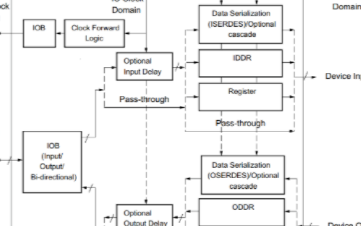

Xilinx SelectIO IP的GUI參數(shù)詳解及應(yīng)用設(shè)計(jì)

雷達(dá)信號(hào)處理離不開高速ADC/DAC的使用,而高速ADC/DAC的信號(hào)處理對(duì)時(shí)序的要求非常苛刻。Xi....

Verilog HDL中定義的26個(gè)有關(guān)門級(jí)的關(guān)鍵字中常用的有哪些?

1、結(jié)構(gòu)描述形式 從電路結(jié)構(gòu)的角度來描述電路模塊,稱為結(jié)構(gòu)描述形式。 Verilog HDL中定義了....

你真的了解Zynq的學(xué)習(xí)嗎?

一、簡(jiǎn)介部分 Zynq是由兩個(gè)主要部分組成的:一個(gè)是由雙核 ARM CortexA9 構(gòu)成的處理系統(tǒng)....

Verilog HDL提供了哪兩種類型的顯式時(shí)序控制

Verilog HDL提供了兩種類型的顯式時(shí)序控制:一種是延遲控制,即定義執(zhí)行語句的延遲時(shí)間;另一種....

設(shè)計(jì)仿真時(shí)PUR和GSR的加入

仿真是我們?cè)隍?yàn)證邏輯功能的常用手段。通過仿真,我們可以提早發(fā)現(xiàn)一些隱含的邏輯Bug。仿真一般分為功能....

怎么利用DDS IP實(shí)現(xiàn)非重復(fù)掃描系統(tǒng)

一個(gè)不容忽視的現(xiàn)實(shí)是:很多時(shí)候,我們穿衣服時(shí)第一道扣子扣錯(cuò)了,卻總在扣最后一道扣子的時(shí)候才發(fā)現(xiàn)。衣服....

仿真的時(shí)候最主要的細(xì)節(jié)是啥?

仿真是我們?cè)隍?yàn)證邏輯功能的常用手段。通過仿真,我們可以提早發(fā)現(xiàn)一些隱含的邏輯Bug。仿真一般分為功能....