仿真是我們在驗證邏輯功能的常用手段。通過仿真,我們可以提早發現一些隱含的邏輯Bug。仿真一般分為功能仿真和時序仿真,有的時候也稱作前仿真和后仿真。這兩者的主要區別是在功能仿真里暫時忽略了邏輯延時和布局布線延時,仿真的模型相對簡單,仿真的運行速度更快。可以用來驗證功能的正確性。時序仿真通過反標的方式將加入延時信息,這樣仿真的結果更接近實際芯片的工作情況。但正因為如此,時序仿真的模型更為復雜,需要計算的信息更多,運行的時間更長。一般情況下,我們首先通過邏輯仿真驗證功能,然后再運行時序仿真驗證時序的正確性。當然現在也有一些做法是在做功能仿真的時候,人為的設定一些延時,雖然不能百分之百的擬合實際的芯片運行情況,但可以覆蓋大多數的應用場景。帶來的好處是仿真的運行比時序仿真要快很多。

各個EDA公司都有自己的仿真工具,針對FPGA/CPLD來說,用的比較多的是Modelsim和Aldec。無論用哪個仿真工具,有一個細節經常會被初學者會忽略。在設計好testbench后,編譯都沒有問題,但在開始仿真的時候,軟件會報類似這樣的錯誤:

Fatal Error: ELAB2_0036 Unresolved hierarchical reference to"PUR_INST.PURNET" from module"tb_cdr_tb.UUT.top_cdr_u.receive_top_u.serial_data_in.FF_3" (modulenot found).

Fatal Error: ELAB2_0036 Unresolved hierarchical reference to"GSR_INST.GSRNET" from module "tb_cdr_tb.UUT.top_cdr_u.receive_top_u.serial_data_in.FF_3"(module not found).

這是因為在芯片工作的時候,內部有PUR(Power Up Reset)和GSR(Global Set/Reset)模塊產生上電復位信號和接入全局復位/置位信號。這個信號在做綜合的時候是自動生成并加入的設計中的,但在仿真的時候編譯并不會加入這兩個模塊。所以如果要做仿真,一定要在你的testbench中加入這樣一段描述:

PUR PUR_INST(.PUR(1'b1));

GSRGSR_INST(.GSR(1'b1));

這樣就可以繼續你的仿真工作了。

文章出處:【微信公眾號:FPGA之家】

責任編輯:gt

-

芯片

+關注

關注

459文章

52452瀏覽量

439978 -

仿真

+關注

關注

52文章

4268瀏覽量

135704

原文標題:仿真的時候不要忘了PUR和GSR

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

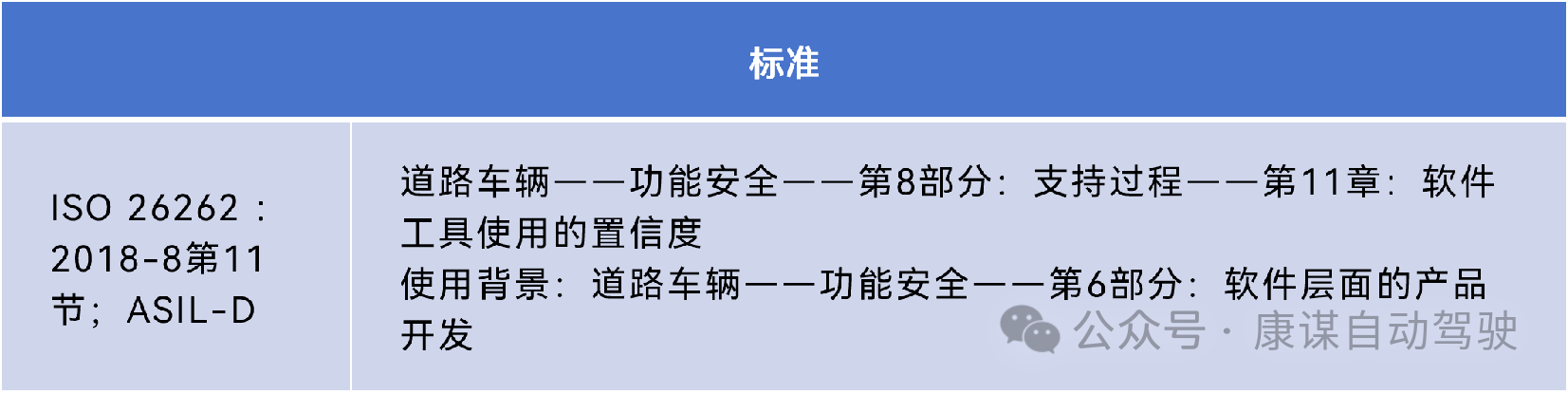

康謀加入ASAM組織,自動駕駛仿真平臺aiSim引領安全新標桿

《聊一聊ZXDoc》之CAN總線仿真、面板仿真

使用MIMXRT685-EVK將WM8904連接到RT685的I3C總線,并通過I2C進行控制遇到的幾個問題求解

LPC553x MCU具有硬件I3C外設,“PUR” 上拉電阻控制引腳是否僅提供100引腳封裝?

AG32 SDK 更新版本1.7.0:加入dsp例程和Slave SPI例程

三伍微電子 IoT FEM芯片 GSR2501:射頻系統設計的性能與效率革新

Lilian Weng加入Fellows Fund Fellow團隊

PanoSim加入MathWorks Connections計劃

躍昉科技正式加入openGauss社區

設計仿真 基于VTD的AR-HUD仿真測試解決方案

設計仿真時PUR和GSR的加入

設計仿真時PUR和GSR的加入

評論