【前言】

最近手上寫了一個練手的小項目,項目的大致要求是實(shí)現(xiàn)一個取指,執(zhí)行電路。取指的指令預(yù)存在,從ROM中讀取指令后,根據(jù)預(yù)定的解碼規(guī)則,對指令進(jìn)行解碼,并執(zhí)行相對應(yīng)的操作。發(fā)出來和大家共同分享。

該工程的設(shè)計要求如下:

在ram模塊中,儲存有初始化的指令數(shù)據(jù)。我們要設(shè)計一個取指電路,并能根據(jù)不同的指令執(zhí)行不同的操作。指令數(shù)據(jù)為16bit.

指令編碼定義如下:

如果指令代碼為0,則下一個狀態(tài)為空閑。如果指令的低位8位為0,高位8位非0,則讀取指定高位8位的存儲器,并將其寫入obuf0。如果指令的低8位非0,且高8位也不是0,則將下8位作為數(shù)據(jù),寫入地址為上8位的存儲器中。

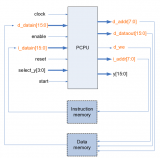

List4顯示了指令獲取電路。它實(shí)例化了五個模塊:PC0(程序計數(shù)器、8位計數(shù)器)、Ir0(指令寄存器、16位計數(shù)器)、OBUF0(輸出緩沖器、16位計數(shù)器)、STATE0(狀態(tài)機(jī))和RAM0(存儲器,8位256字塊RAM)。模塊pc0用于指定要讀取的地址,以便從ram0獲取(提取)指令代碼。指令代碼存儲在IR0中。

此指令獲取操作在兩種狀態(tài)下執(zhí)行:fetcha和fetchb。fetcha用于取地址操作,該地址作為讀取ram中指令的地址,fetchb用于指令寄存操作,將指令寄存到指令寄存器中。

在execa和execb狀態(tài)下,執(zhí)行表1中的操作。如果存儲在IR0中的指令代碼為0,則下一個狀態(tài)為空閑。如果指令的低位8位為0,高位8位非0,則讀取指定高位8位的存儲器,并將其寫入obuf0。如果指令的下8位非0,則將下8位寫入地址為上8位的存儲器。

指令解碼列在table1中

頂層代碼如圖所示:

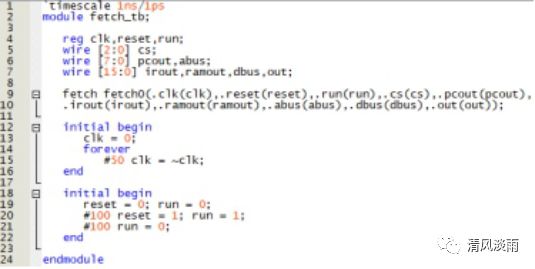

下面是該工程的測試模塊:

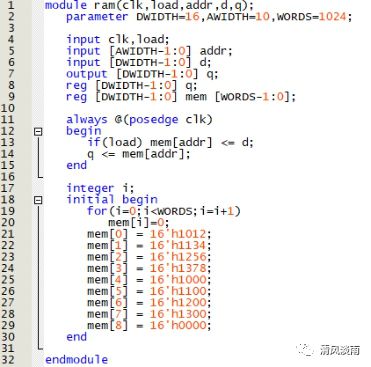

下面的ram模塊的代碼:

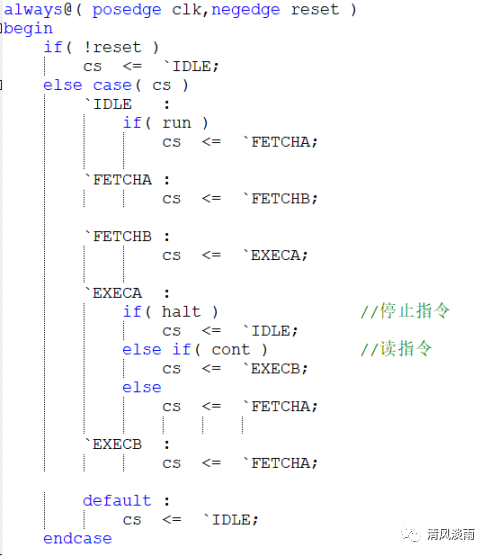

狀態(tài)控制模塊的代碼:

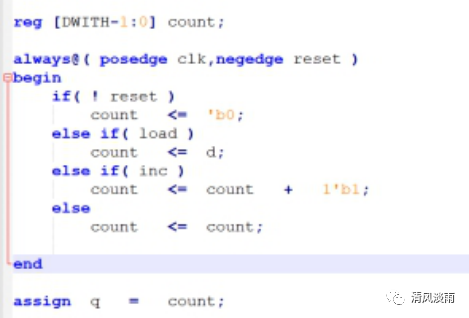

計數(shù)器模塊的代碼:

設(shè)計說明

該工程有以下模塊組成:

PC0(程序計數(shù)器、8位計數(shù)器)、

Ir0(指令寄存器、16位計數(shù)器)、

OBUF0(輸出緩沖器、16位計數(shù)器)、

STATE0(狀態(tài)機(jī))、

RAM0(存儲器,8位256字塊RAM)。

其中,PC0,IR0,OBUF0是例化計數(shù)器模塊得到的,該計數(shù)器模塊擁有計數(shù)和寄存數(shù)據(jù)兩個功能,分別由端口 inc 和 端口 load 控制。

當(dāng) inc有效時,在下一個時鐘,會將計數(shù)器內(nèi)部的計數(shù)器自增1,并在q端輸出。

當(dāng)load信號有效時,在下一個時鐘會將D端 的數(shù)據(jù)寄存到該計數(shù)器的寄存器中,并在Q端輸出。

PC0利用的是計數(shù)器的計數(shù)功能,用于產(chǎn)生取指令的地址信息。

IR0利用的是計數(shù)器的寄存功能,用于將ram中取出的指令暫時寄存。

OBUF0利用的是計數(shù)器的寄存功能,用于將輸出中暫時寄存。

在狀態(tài)機(jī)控制模塊中,設(shè)置了以下五個狀態(tài):

IDLE:空閑態(tài)。

FETCHA:取地址狀態(tài)。同時將程序計數(shù)器的內(nèi)部計數(shù)值加一。

FETCHB:取指令,指令寄存狀態(tài)。將從ram中讀出的指令寫入到指令寄存器模塊中。

EXECA:指令解碼模塊,判斷指令的停止,讀,寫控制信號。如果為寫信號,將指令的低8位作為數(shù)據(jù)寫到高8位對應(yīng)的地址中。如果為讀指令,跳轉(zhuǎn)到EXECB狀態(tài),將指令的低8位輸出。如果停止信號為真3,跳轉(zhuǎn)到空閑狀態(tài)。

EXECB:執(zhí)行狀態(tài)。用于將指令的低8位輸出。

在ram模塊中,儲存有初始化的指令數(shù)據(jù)。

編輯:jq

-

cpu

+關(guān)注

關(guān)注

68文章

11031瀏覽量

215946

原文標(biāo)題:簡單的CPU取指執(zhí)行電路設(shè)計

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

CPU的各種指令和執(zhí)行流程

RISC-V五級流水線CPU設(shè)計

堆取料機(jī)DCS數(shù)據(jù)采集物聯(lián)網(wǎng)解決方案

Linux之CPU調(diào)度策略和CPU親和性

數(shù)控車床m99指令的用法

功率放大電路的轉(zhuǎn)換效率是指什么

為什么外設(shè)要通過接口與CPU相連

雙核cpu和單核cpu的區(qū)別

CPU主要參數(shù)有哪些

如何用LM324做PI電路?

Imagination CPU 系列研討會 | RISC-V 平臺的性能分析和調(diào)試

你們會設(shè)計CPU取指執(zhí)行電路嗎?

你們會設(shè)計CPU取指執(zhí)行電路嗎?

評論