CPU(中央處理器)是計(jì)算機(jī)的核心部件,負(fù)責(zé)執(zhí)行程序指令和處理數(shù)據(jù)。CPU主要由控制器和運(yùn)算器組成,這兩個(gè)部件共同完成計(jì)算機(jī)的運(yùn)算任務(wù)。下面詳細(xì)介紹CPU控制器和運(yùn)算器組成的部件。

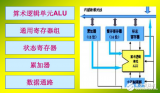

- 運(yùn)算器(ALU)

運(yùn)算器(Arithmetic Logic Unit,簡(jiǎn)稱ALU)是CPU中負(fù)責(zé)執(zhí)行算術(shù)和邏輯運(yùn)算的部分。ALU的主要功能包括:

1.1. 算術(shù)運(yùn)算:ALU可以執(zhí)行加法、減法、乘法和除法等基本算術(shù)運(yùn)算。

1.2. 邏輯運(yùn)算:ALU可以執(zhí)行與(AND)、或(OR)、非(NOT)、異或(XOR)等基本邏輯運(yùn)算。

1.3. 比較運(yùn)算:ALU可以比較兩個(gè)數(shù)的大小,判斷它們是否相等、大于或小于。

1.4. 位移運(yùn)算:ALU可以對(duì)數(shù)據(jù)進(jìn)行左移、右移等位移操作。

1.5. 位運(yùn)算:ALU可以對(duì)數(shù)據(jù)的特定位進(jìn)行設(shè)置、清除、翻轉(zhuǎn)等操作。

- 控制器(CU)

控制器(Control Unit,簡(jiǎn)稱CU)是CPU中負(fù)責(zé)控制和管理整個(gè)計(jì)算機(jī)系統(tǒng)的部件。CU的主要功能包括:

2.1. 指令獲取:CU從內(nèi)存中獲取指令,并將其解碼為可執(zhí)行的操作。

2.2. 指令執(zhí)行:CU根據(jù)解碼后的指令,控制ALU和其他部件執(zhí)行相應(yīng)的操作。

2.3. 數(shù)據(jù)傳輸:CU負(fù)責(zé)管理數(shù)據(jù)在CPU內(nèi)部和外部的傳輸。

2.4. 異常處理:CU可以處理程序運(yùn)行過(guò)程中出現(xiàn)的異常情況,如除零錯(cuò)誤、越界錯(cuò)誤等。

2.5. 中斷處理:CU可以響應(yīng)外部設(shè)備的中斷請(qǐng)求,暫停當(dāng)前程序的執(zhí)行,轉(zhuǎn)而執(zhí)行中斷服務(wù)程序。

- 寄存器組(Register Set)

寄存器組是CPU內(nèi)部用于存儲(chǔ)數(shù)據(jù)和指令的高速存儲(chǔ)器。寄存器組的主要部件包括:

3.1. 程序計(jì)數(shù)器(Program Counter,簡(jiǎn)稱PC):PC用于存儲(chǔ)下一條要執(zhí)行的指令的地址。

3.2. 指令寄存器(Instruction Register,簡(jiǎn)稱IR):IR用于存儲(chǔ)當(dāng)前正在執(zhí)行的指令。

3.3. 累加器(Accumulator,簡(jiǎn)稱ACC):ACC用于存儲(chǔ)ALU執(zhí)行算術(shù)運(yùn)算和邏輯運(yùn)算的結(jié)果。

3.4. 狀態(tài)寄存器(Status Register,簡(jiǎn)稱SR):SR用于存儲(chǔ)CPU的狀態(tài)信息,如進(jìn)位標(biāo)志、零標(biāo)志等。

3.5. 基址寄存器(Base Register,簡(jiǎn)稱BR):BR用于存儲(chǔ)內(nèi)存的基地址,以便進(jìn)行內(nèi)存訪問(wèn)。

3.6. 索引寄存器(Index Register,簡(jiǎn)稱IX):IX用于存儲(chǔ)數(shù)組或表的索引值。

3.7. 數(shù)據(jù)寄存器(Data Register,簡(jiǎn)稱DR):DR用于存儲(chǔ)ALU執(zhí)行操作的數(shù)據(jù)。

- 時(shí)鐘和總線系統(tǒng)

4.1. 時(shí)鐘系統(tǒng):CPU內(nèi)部有一個(gè)時(shí)鐘信號(hào)發(fā)生器,用于控制CPU的工作節(jié)奏。時(shí)鐘信號(hào)的頻率決定了CPU的運(yùn)行速度。

4.2. 總線系統(tǒng):CPU內(nèi)部和外部的數(shù)據(jù)傳輸都通過(guò)總線系統(tǒng)進(jìn)行。總線系統(tǒng)包括數(shù)據(jù)總線、地址總線和控制總線。

4.2.1. 數(shù)據(jù)總線:用于傳輸CPU內(nèi)部和外部的數(shù)據(jù)。

4.2.2. 地址總線:用于指定內(nèi)存中數(shù)據(jù)的地址。

4.2.3. 控制總線:用于傳輸CPU內(nèi)部和外部的控制信號(hào)。

- 緩存(Cache)

緩存是CPU內(nèi)部的高速存儲(chǔ)器,用于存儲(chǔ)最近訪問(wèn)過(guò)的數(shù)據(jù)和指令。緩存的主要作用是減少CPU訪問(wèn)內(nèi)存的時(shí)間,提高計(jì)算機(jī)的運(yùn)行速度。緩存分為一級(jí)緩存(L1 Cache)和二級(jí)緩存(L2 Cache)。

5.1. 一級(jí)緩存:L1 Cache是CPU內(nèi)部的最小緩存,通常分為數(shù)據(jù)緩存和指令緩存兩部分。

5.2. 二級(jí)緩存:L2 Cache是CPU內(nèi)部的較大緩存,通常與L1 Cache一起工作,提高數(shù)據(jù)訪問(wèn)速度。

- 微架構(gòu)(Microarchitecture)

微架構(gòu)是CPU內(nèi)部的組織結(jié)構(gòu),決定了CPU的指令執(zhí)行方式和性能。常見(jiàn)的微架構(gòu)包括:

6.1. CISC(Complex Instruction Set Computer):CISC架構(gòu)的CPU具有豐富的指令集,每個(gè)指令可以完成復(fù)雜的操作。

6.2. RISC(Reduced Instruction Set Computer):RISC架構(gòu)的CPU具有簡(jiǎn)化的指令集,每個(gè)指令執(zhí)行簡(jiǎn)單的操作,但執(zhí)行速度更快。

6.3. VLIW(Very Long Instruction Word):VLIW架構(gòu)的CPU可以在一個(gè)時(shí)鐘周期內(nèi)執(zhí)行多個(gè)指令,提高指令的并行度。

-

控制器

+關(guān)注

關(guān)注

114文章

16933瀏覽量

182695 -

cpu

+關(guān)注

關(guān)注

68文章

11028瀏覽量

215787 -

運(yùn)算器

+關(guān)注

關(guān)注

1文章

164瀏覽量

16734

發(fā)布評(píng)論請(qǐng)先 登錄

CPU怎樣通過(guò)控制器將待運(yùn)行的程序從FLASH中讀入內(nèi)存中

CPU=運(yùn)算器+控制器

運(yùn)算器的相關(guān)資料下載

運(yùn)算器,運(yùn)算器的作用和原理是什么?

定點(diǎn)運(yùn)算器的基本結(jié)構(gòu)(圖解篇)

運(yùn)算器部件的組成及原理設(shè)計(jì)

什么是運(yùn)算器_運(yùn)算器由什么組成

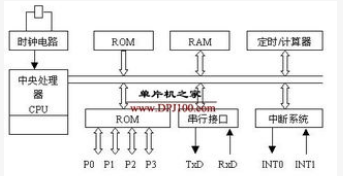

MCS-51單片機(jī)中各個(gè)邏輯部件的功能是什么

計(jì)算機(jī)cpu主要由什么組成

實(shí)驗(yàn)一 運(yùn)算器實(shí)驗(yàn)

cpu控制器和運(yùn)算器組成的部件有哪些

cpu控制器和運(yùn)算器組成的部件有哪些

評(píng)論