前言:集成電路(芯片)是用光刻為特征的制造工藝,一層一層制造而成。所以,芯片技術(shù)中就有了“層”的概念。那么,芯片技術(shù)中有多少關(guān)于“層”的概念?媒體報(bào)道說(shuō)美光公司推出了176層的3D NAND閃存芯片,這里的“層”又是什么意思?本文從科普的視角,來(lái)個(gè)“層層”全解析。

要說(shuō)明芯片技術(shù)中“層”的概念,要先大致了解一下芯片的設(shè)計(jì)和制造過(guò)程。這些科普內(nèi)容已在我的另一片文章“【芯論語(yǔ)】光刻如何一步一步變成了芯片制造的卡脖子技術(shù)?”中介紹過(guò)[5]。該文介紹了光刻工藝如何按照芯片設(shè)計(jì)布圖(Layout),一層一層把不同的半導(dǎo)體材料制作在硅片上,最后形成了一個(gè)有結(jié)構(gòu)的電路元器件層的過(guò)程。本文不再展開(kāi)論述,僅引用了這篇文章中如下兩張圖加以說(shuō)明。

芯片布圖在制造準(zhǔn)備過(guò)程中被分離成多個(gè)掩膜圖案,并制成一套多張的掩膜版(圖2b)。芯片制造廠按照工藝順序安排,逐層把掩膜版上的圖案制作在硅片上,形成了一個(gè)立體的晶體管(圖2c)。

一個(gè)芯片上可以包含數(shù)億~數(shù)百億個(gè)晶體管,并經(jīng)過(guò)互連實(shí)現(xiàn)了芯片的整體電路功能。經(jīng)過(guò)制造工藝的各道工序后,這些晶體管將被同時(shí)加工出來(lái)。并且,在硅晶圓上整齊排滿了數(shù)量巨大的相同芯片,經(jīng)過(guò)制造工藝的各道工序后,這些芯片也將被同時(shí)加工出來(lái)。

一、材料介質(zhì)層 vs電路層

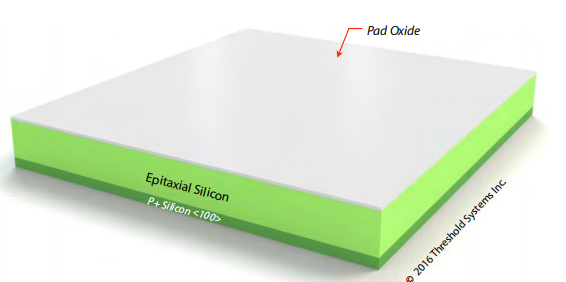

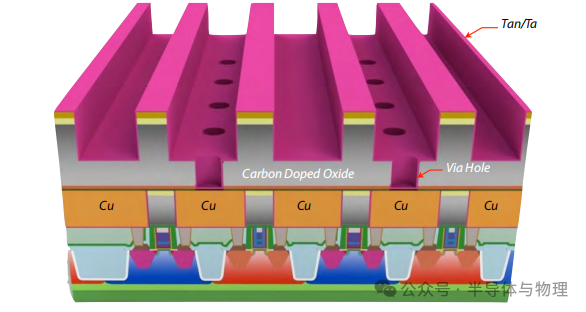

芯片布圖上的每一層圖案用不同顏色標(biāo)示。對(duì)應(yīng)每一層的圖案,制造過(guò)程會(huì)在硅晶圓上制做出一層由半導(dǎo)體材料或介質(zhì)構(gòu)成的圖形。本文把這些圖形層稱(chēng)之為材料介質(zhì)層。例如P型襯底層、N型擴(kuò)散區(qū)層、氧化膜絕緣層、多晶硅層、金屬連線層等。芯片布圖有多少層,制造完成后的硅晶圓上基本就有多少材料介質(zhì)層。根據(jù)工藝安排,材料介質(zhì)層的層數(shù)也許還會(huì)有增加。

芯片制造就是按照芯片布圖,在硅晶圓上逐層制做材料介質(zhì)層的過(guò)程。材料介質(zhì)層在硅晶圓上疊加在一起,就形成了整個(gè)芯片上,乃至整個(gè)硅晶圓上所有的電路元器件。它們主要包括晶體管(三極管)、存儲(chǔ)單元、二極管、電阻、連線、引腳等。

圖4.芯片微觀示意圖 (從材料介質(zhì)層角度看是縱橫交錯(cuò)的線條,從電路層角度看是平鋪在硅片上的一層電路元器件)

這些電路元器件從材料介質(zhì)層的角度上看是有結(jié)構(gòu)的、立體的。但是,電路元器件是平面分布在硅片上,乃至整個(gè)硅晶圓上,它們是二維(2D)分布的,是一個(gè)平面層。本文把硅晶圓上的電路元器件層稱(chēng)之為電路層。這樣的芯片裸片封裝起來(lái)就是早期傳統(tǒng)的平面芯片(2D芯片)。

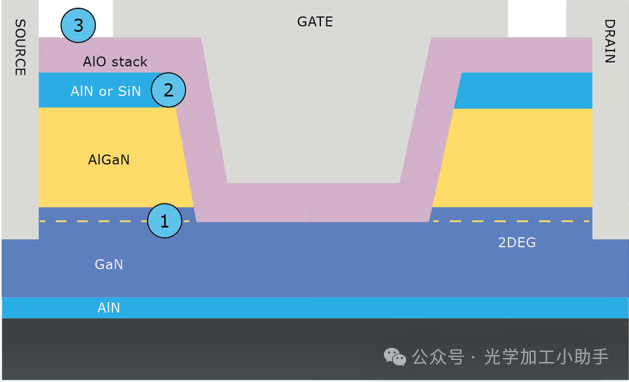

二、平面結(jié)構(gòu)器件 vs側(cè)向結(jié)構(gòu)器件

電路層中,早期電路元器件的結(jié)構(gòu)是平面擺放的,稱(chēng)為平面(Planar)結(jié)構(gòu)器件。為了提高芯片集成度,電路元器件特別是晶體管尺寸一直在按照摩爾定律縮小,當(dāng)器件尺寸縮小到不能再縮小的時(shí)候,業(yè)界發(fā)明了把電路元器件豎起來(lái)的結(jié)構(gòu)形式,以縮小芯片面積。有人把這種豎起來(lái)的器件稱(chēng)為三維(3D)、立體的結(jié)構(gòu)器件。筆者覺(jué)得將其稱(chēng)為側(cè)向(Sideways)結(jié)構(gòu)器件更為準(zhǔn)確。因?yàn)槿缯撈矫娼Y(jié)構(gòu)器件還是側(cè)向結(jié)構(gòu)器件,雖然從材料介質(zhì)層角度看都是立體的,但是從元器件整體來(lái)看,它們平面分布在硅晶圓上,只是一層電路元器件,并沒(méi)有立體的概念。

早期的芯片制造工藝比較傳統(tǒng),在硅晶圓上只能制造一個(gè)電路層。電路元器件的結(jié)構(gòu)不管是平面的(圖5a、圖6a),或者是側(cè)向的(圖5b、圖6b),元器件上面不再有元器件的堆疊。經(jīng)過(guò)電路層制造、劃片、封裝和測(cè)試,就完成了芯片制造的全過(guò)程。這種單個(gè)電路層的芯片就是早期傳統(tǒng)的平面芯片(2D芯片)。

三、多層芯片堆疊封裝,形成偽3D芯片

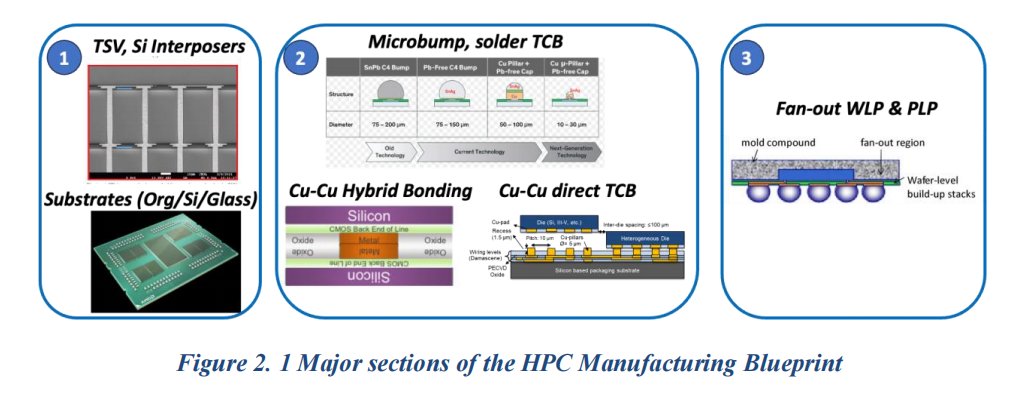

隨著芯片封裝工藝進(jìn)步,為了縮小芯片尺寸,業(yè)界發(fā)明了多層芯片堆疊封裝技術(shù)。開(kāi)始時(shí),堆疊封裝是把多個(gè)芯片裸片堆疊放置在一起,把芯片之間的信號(hào)通過(guò)邦定(bonding)技術(shù)連結(jié),組成內(nèi)部的完整系統(tǒng),再把外部信號(hào)通過(guò)封裝引腳外連,最后封裝成為一個(gè)完整芯片(圖7a)。后來(lái),業(yè)界發(fā)明了硅通孔(TSV)技術(shù),堆疊的芯片裸片之間的信號(hào)是通過(guò)TSV連接,形成了更加緊湊的多芯片堆疊封裝芯片。

這種芯片內(nèi)部有多個(gè)電路層,它們可以稱(chēng)為立體芯片,或者稱(chēng)為3D芯片。但是,這種3D芯片是在封裝階段通過(guò)多層芯片裸片堆疊形成的,從芯片制造角度看,這種3D芯片只能看作是偽3D芯片。

四、多層電路層堆疊制造,形成真3D芯片

目前,芯片制造工藝已發(fā)展到爐火純青的地步。為了節(jié)省硅片面積,在下面的電路層制作完成之后,可以繼續(xù)在其上制做另一層電路層,形成兩個(gè)、甚至多個(gè)電路層在硅晶圓上的堆疊,在芯片制造階段就完成了3D芯片的制造。這樣就實(shí)現(xiàn)了真正意義上的立體芯片,也簡(jiǎn)稱(chēng)3D芯片。

這種技術(shù)目前主要用在3DNAND閃存等很規(guī)則的芯片制造領(lǐng)域。存儲(chǔ)單元(Memory Cell)采用側(cè)向結(jié)構(gòu)。一般地,閃存芯片如果號(hào)稱(chēng)是N層的NAND閃存,就至少有N個(gè)電路層。目前,三星的3D V-NAND存儲(chǔ)單元的層數(shù)已由2009年的2層逐漸提升至24層、64層,再到2018年的96層[2],2019年8月完成128層V-NAND閃存的開(kāi)發(fā),并實(shí)現(xiàn)量產(chǎn)。三星計(jì)劃2021年下半年則會(huì)量產(chǎn)第7代V-NAND閃存,堆疊層數(shù)提升到176層。美光已發(fā)布了采用最新技術(shù)的第五代176層3D NAND閃存芯片[4]。

在國(guó)內(nèi),長(zhǎng)江存儲(chǔ)2017年7月研制成功了國(guó)內(nèi)首顆3D NAND閃存芯片;2018年三季度32層產(chǎn)品實(shí)現(xiàn)量產(chǎn);2019年三季度64層產(chǎn)品實(shí)現(xiàn)量產(chǎn)。目前已宣布成功研發(fā)出128層3D NAND閃存芯片系列[3]。長(zhǎng)江存儲(chǔ)3D NAND閃存技術(shù)的快速發(fā)展,得益于其獨(dú)創(chuàng)的“把存儲(chǔ)陣列(Cell Array)和外圍控制電路(Periphery)分開(kāi)制造,再合并封裝在一起”的XtackingTM技術(shù)。

圖9.長(zhǎng)江存儲(chǔ)的XtackingTM技術(shù)演示(來(lái)源:長(zhǎng)江存儲(chǔ)官網(wǎng))

據(jù)報(bào)道,美光最新一代的176層3D NAND將直接取代96層的版本。目前已知的是,美光首批176層3D NAND采用了將雙88層融合到一起的設(shè)計(jì)(堆疊512Gbit TLC閃存)。該芯片技術(shù)換用了電荷陷阱存儲(chǔ)單元的方案,似乎也極大地降低了每一層的厚度。目前176層的裸片僅為45μm,與美光的64層浮柵3D NAND相同。16層裸片堆疊式封裝的厚度不到1.5 mm,適用于大多數(shù)移動(dòng)/存儲(chǔ)卡使用場(chǎng)景[4]。

后記:本文通過(guò)光刻技術(shù)和芯片制造技術(shù)介紹,理清了芯片技術(shù)中的材料介質(zhì)層與電路層的概念,從而更清楚知道什么是2D芯片,什么是3D芯片?也了解到目前的3D閃存芯片,在制造時(shí)就可以堆疊集成多達(dá)176層的電路層。更甚者,這種3D芯片在封裝時(shí)還可以進(jìn)行多達(dá)16層裸片的堆疊封裝。在一塊厚度不到1.5mm的閃存卡中,竟然有多達(dá)2816層的電路層在工作,芯片技術(shù)的精妙之處可見(jiàn)一斑。

原文標(biāo)題:【芯論語(yǔ)】科普:芯片中的“層”,“層層”全解析

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52199瀏覽量

436400 -

集成電路

+關(guān)注

關(guān)注

5420文章

11955瀏覽量

367219

原文標(biāo)題:【芯論語(yǔ)】科普:芯片中的“層”,“層層”全解析

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

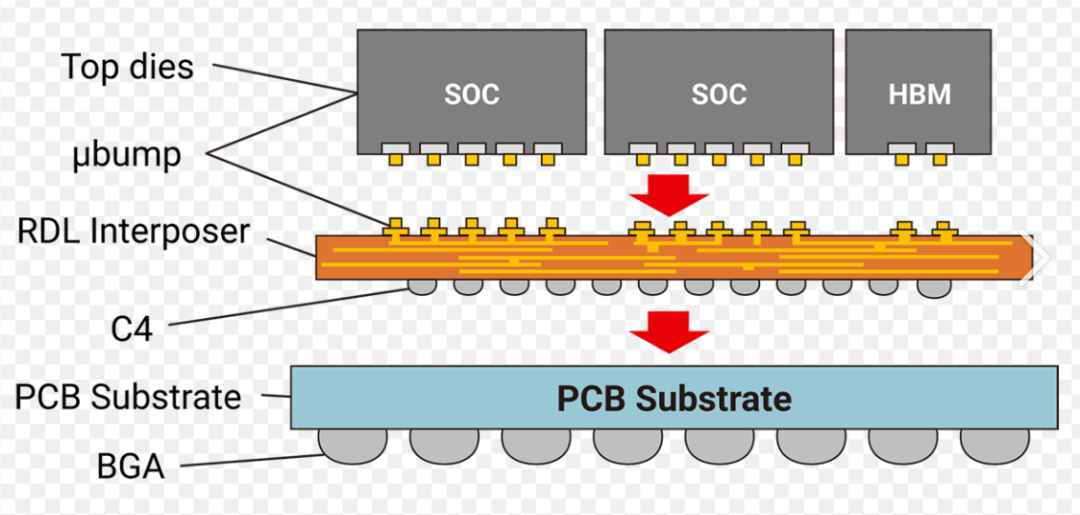

芯片封裝中的RDL(重分布層)技術(shù)

芯片制造的關(guān)鍵一環(huán):介質(zhì)層制備工藝全解析

DAC8760接上了24V以后,芯片表面就有啪的一聲,是哪里出了問(wèn)題?

先進(jìn)封裝的核心概念、技術(shù)和發(fā)展趨勢(shì)

OSI七層模型的每一層功能

tas5548接上usb在電腦上放音樂(lè),放著放著就有爆破音了,為什么?

原子層鍍膜在功率器件行業(yè)的應(yīng)用

tlv320aic3106老化一段時(shí)間聲音就有滋滋底噪了,為什么?

SK海力士引領(lǐng)未來(lái):全球首發(fā)12層HBM3E芯片,重塑AI存儲(chǔ)技術(shù)格局

AI網(wǎng)絡(luò)物理層底座: 大算力芯片先進(jìn)封裝技術(shù)

芯片技術(shù)中就有了“層”的概念是什么?

芯片技術(shù)中就有了“層”的概念是什么?

評(píng)論