文章來源:半導體與物理

原文作者:jjfly686

本文介紹了在芯片銅互連工藝中需要阻擋層的原因以及關鍵工藝流程。

為什么需要阻擋層?

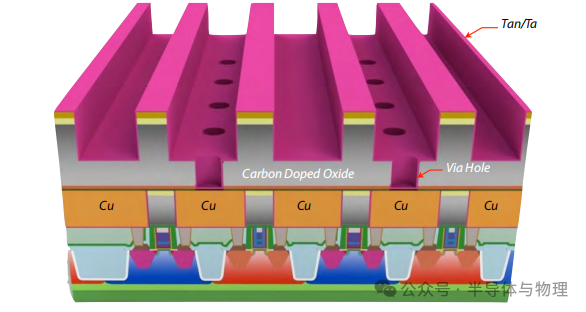

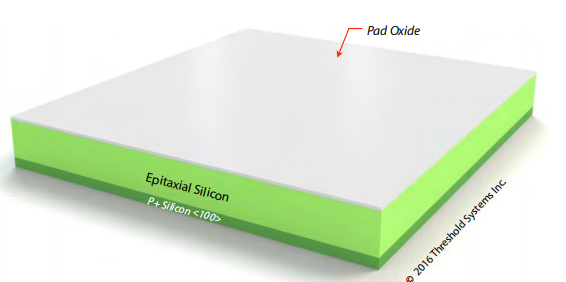

在芯片的銅互連工藝中,銅原子極易向周圍的絕緣介質(如SiO?或Low-K材料)擴散,導致電路短路或漏電失效。為了阻止這種擴散,必須在銅與介質之間沉積一層納米級阻擋層。氮化鉭(TaN)因其高致密性、抗擴散能力和導電性,成為主流選擇。然而,隨著制程進入28 nm以下節點,阻擋層的均勻性和覆蓋性面臨巨大挑戰。

物理氣相沉積(PVD)技術:

在22 nm和14 nm節點,PVD仍是阻擋層沉積的核心技術,其優勢與創新如下:

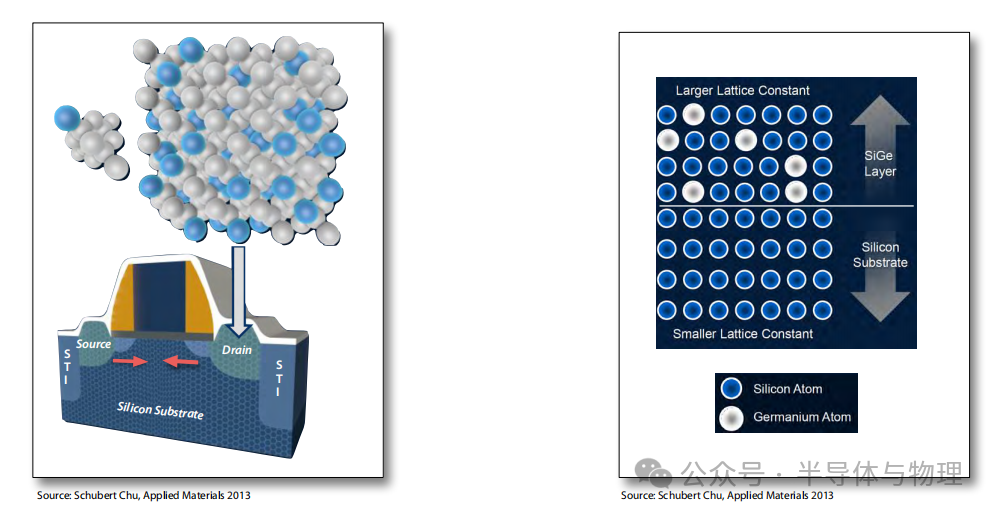

離子化金屬等離子體PVD

通過高能離子轟擊鉭靶材,濺射出鉭原子并與氮氣反應生成TaN薄膜。再濺射(Re-sputter)工藝。在沉積TaN后,用氬離子轟擊薄膜表面,將底部的TaN重新分布到側壁,顯著提升深寬比>5:1的通孔覆蓋率(如32 nm節點側壁覆蓋提升40%)。

工藝優勢

TaN薄膜(2-5 nm)的沉積速率可達10 nm/min,適合量產;無需碳基前驅體,避免ALD工藝中的碳殘留問題;設備成熟,單次工藝成本比ALD低30%以上。

局限性

深孔底部覆蓋率不足,需結合濺射清洗(Sputter Clean)去除殘留污染物;10 nm以下線寬中,PVD的臺階覆蓋率(<50%)難以滿足需求。

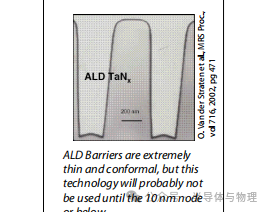

原子層沉積(ALD)

ALD雖在理論上具備原子級精度,但在實際應用中仍面臨多重挑戰:

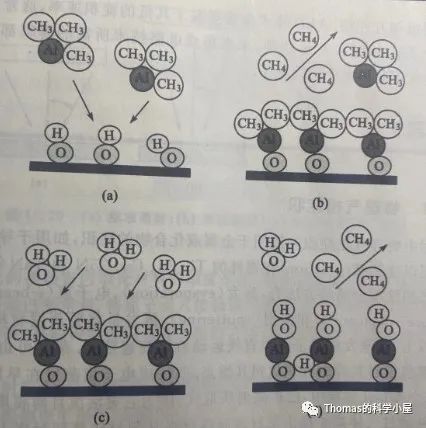

ALD TaN的工藝瓶頸

前驅體污染:使用有機鉭源(如Ta(NMe?)?)和氨氣(NH?)反應時,碳殘留會導致薄膜電阻率升高(比PVD TaN高3倍);空間位阻效應:在深寬比>10:1的結構中,前驅體分子無法有效擴散至底部,導致薄膜不連續;沉積速率低:ALD單循環僅生長0.1 nm,沉積5 nm薄膜需50次循環,耗時是PVD的10倍。

潛在優勢與未來應用

ALD可在3D FinFET側壁實現±0.2 nm的厚度控制;

隨著線寬縮至5 nm,ALD可能成為唯一滿足覆蓋性要求的技術。

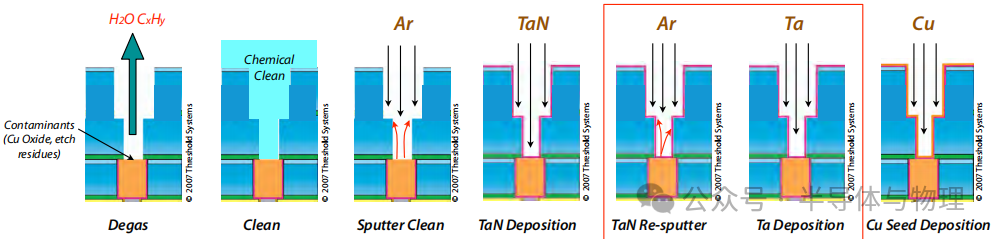

關鍵工藝流程解析(以28 nm雙大馬士革結構為例)

目的:去除通孔內的銅氧化物和刻蝕殘留。

方法:硝酸/氫氟酸(HNO?/HF)混合溶液腐蝕,隨后200℃烘烤去除水分。

參數:軟性氬離子轟擊(能量<50 eV),清除底部殘留污染物,提升TaN附著力。

PVD沉積:沉積2 nm TaN層,隨后氬離子再濺射,將底部TaN重新分布至側壁(覆蓋率從60%提升至85%)。

作用:作為銅種子層的黏附層,厚度1-2 nm,防止銅剝離。

工藝:PVD沉積300 nm銅層,為后續電鍍銅填充提供導電基底。

化學清洗(Chemical Clean)

濺射清洗(Sputter Clean)

TaN沉積與再濺射

鉭(Ta)層沉積

銅種子層(Cu Seed)沉積

-

芯片

+關注

關注

459文章

52192瀏覽量

436238 -

半導體

+關注

關注

335文章

28615瀏覽量

232644 -

工藝

+關注

關注

4文章

671瀏覽量

29254

原文標題:芯片制造中的阻擋層沉積

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

應用材料公司推出15年來銅互聯工藝最大變革[轉]

晶片清洗、阻擋層形成和光刻膠應用

基于PVD 薄膜沉積工藝

接觸刻蝕阻擋層應變技術介紹

芯片制造中的鈍化層工藝簡述

一文了解金屬互連中阻擋層

芯片制造中的阻擋層沉積技術介紹

芯片制造中的阻擋層沉積技術介紹

評論