前言

隨著5G、AI、航天等領域迅猛發展,高速信號處理需求日益突出,硬件加速勢在必行。異構多核架構近年來得到業界廣泛重視,一方面,CPU/GPU算力受限,無法應對高速海量數據實時計算;另一方面,以ASIC、FPGA為代表的硬件加速器具有并行計算優勢,可實現高吞吐率、低時延處理,但操控靈活性尚有不足。因此,基于CPU/GPU+ASIC/FPGA的異構計算平臺順勢推出,既能保證操控靈活性,又能保證高速低時延處理,可應對5G、AI、數據中心、航天等領域重大需求。

FPGA作為高度集成可編程芯片,在工業、通信、航天等行業得到廣泛應用,FPGA工程師將致力于實現功能需求定制開發FPGA。如何進行FPGA開發,需要掌握哪些技術,是每一個FPGA工程師面臨的首要問題。本系列文章基于高亞軍老師的視頻教程,結合Xilinx公司的Vivado集成開發環境,為大家講解如何利用Vivado進行FPGA開發。

Xilinx FPGA/ Vivado開發教程

01

第一講

Vivado設計流程及使用模式

注意,高老師在B站的視頻教程給出了demo工程演示,本文就不做演示部分的內容說明,自己動手新建一個工程,進行實踐。

在第一講中,我們將了解Xilinx的ISE和Vivado設計套件的不同點,以及如何使用Vivado進行FPGA開發。

Vivado是ISE的升級版,可應用于7系列FPGA、ZYNQ、SOC等開發,功能更強大。

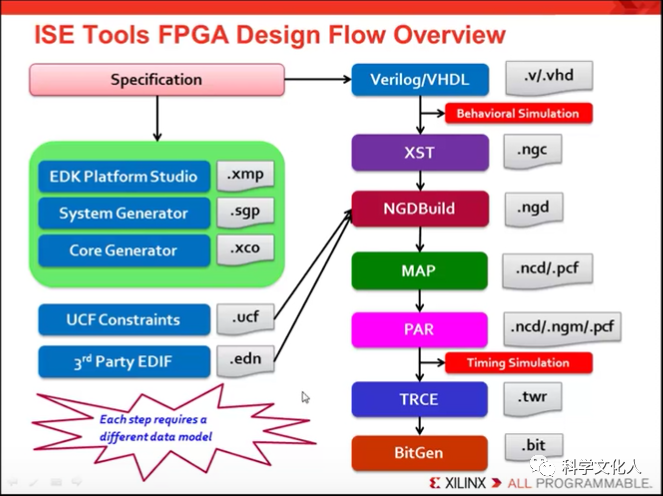

ISE工具FPGA設計流程:

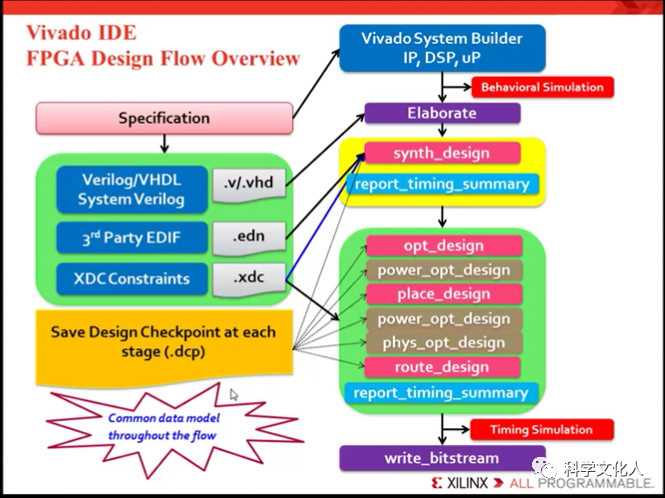

Vivado集成發開環境FPGA設計流程:

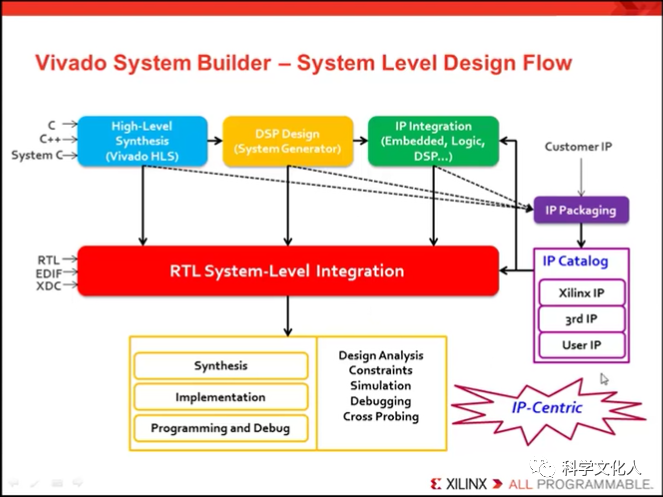

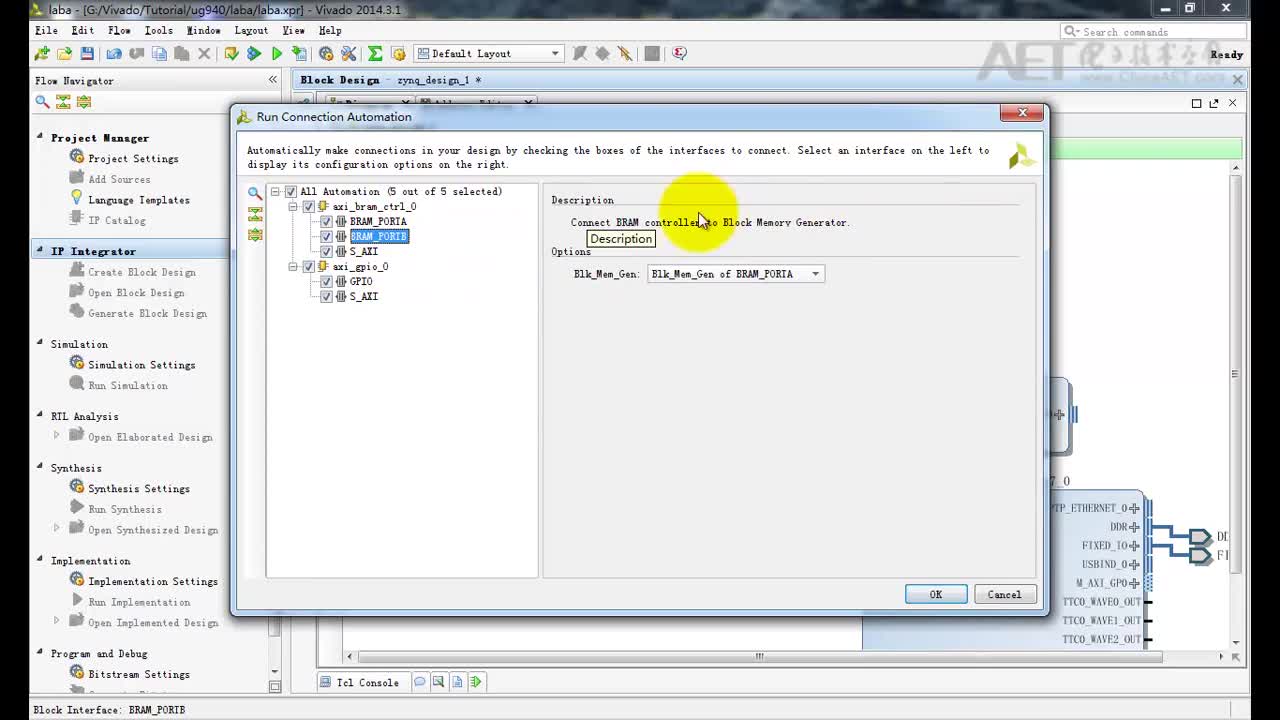

采用Vivado進行系統級設計時,IP模塊是一個重要組成部分,不論是軟核、硬核還是固核,或者自己用RTL邏輯開發的IP模塊,在Vivado中可快速集成。

在開發過程中,設計分析(如時序、邏輯),約束文件(如I/O、時鐘),仿真驗證,綜合與實現,在線debug(VIO、ILA)調試,更高一級技術要求,如方案與架構設計、資源與性能評估、系統算法,都需要工程師們掌握。

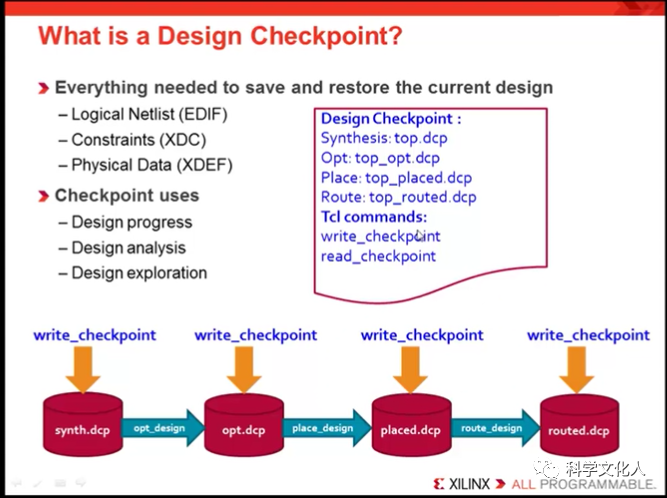

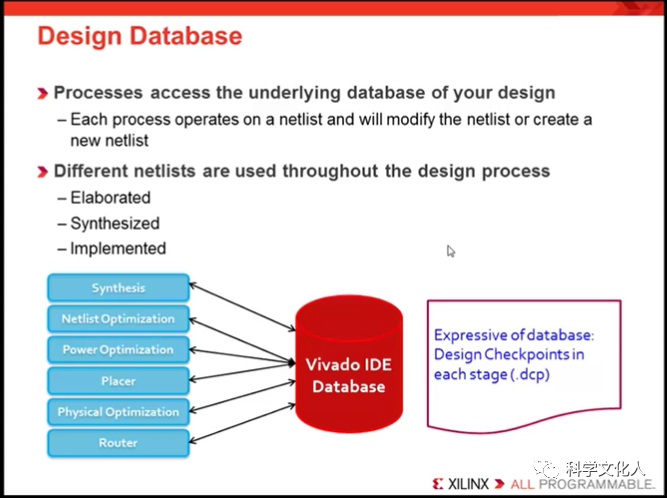

Vivado工具在設計的每個階段,會生成對應的文件和網表,并進行相應的檢查。

當新建一個工程后,工程文件夾包含整個工程的數據庫,并進行設計更新。

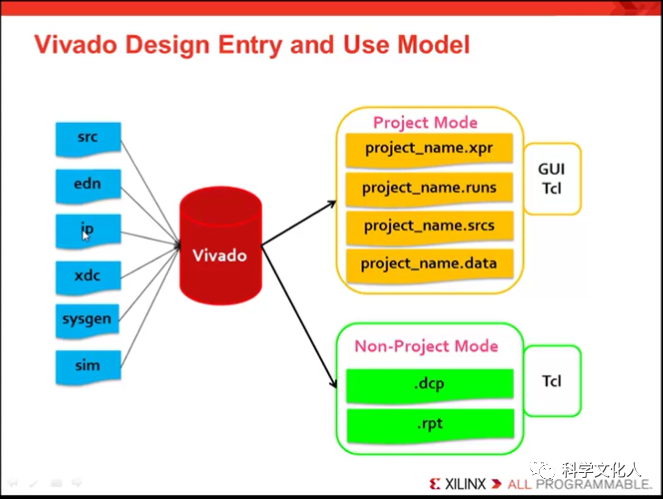

在利用Vivado進行設計時,使用模式有Project Mode和Non-Project Mode之分,我們常用的是Project Mode。

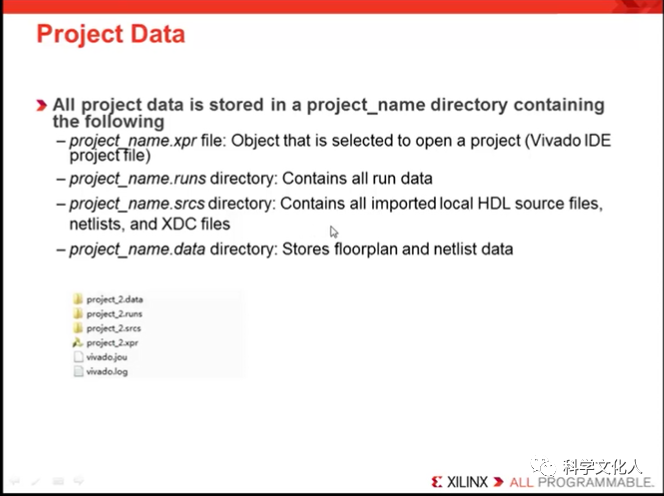

建立一個工程后,會將工程數據保存在工程文件夾下。

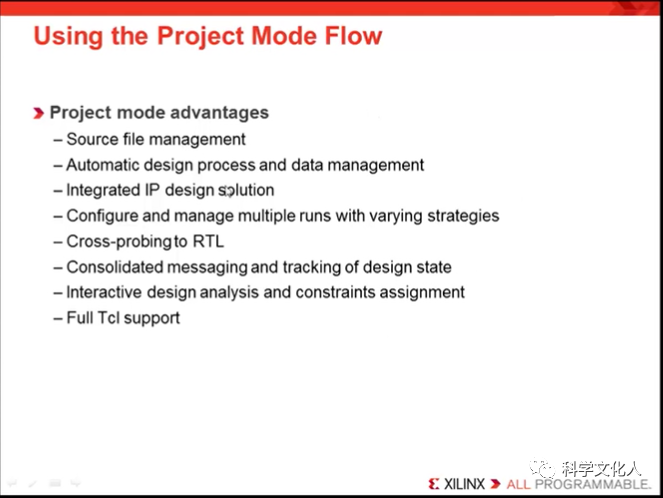

對于Project Mode,其特點為:

源文件管理、設計過程和數據管理、集成IP設計方案、配置和管理策略、RTL模塊移植、設計分析和約束管理、支持TCL命令操作等等,一應俱全。

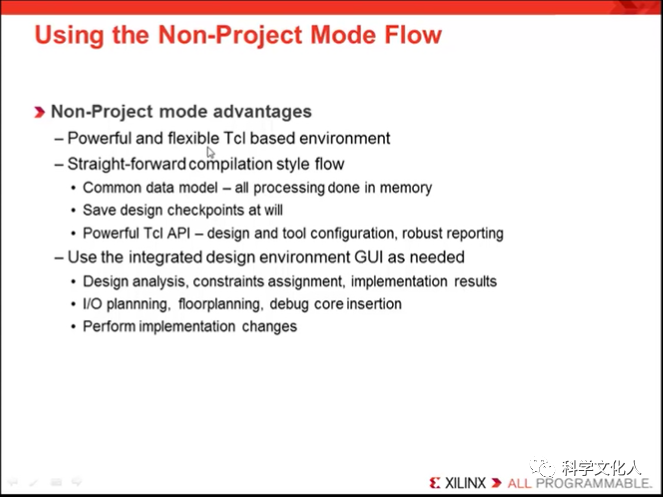

對于Non-Project Mode,其特點為:

該模式下,TCL用得多,感覺不是很適合做工程開發。

文章出處:【微信公眾號:FPGA之家】

-

FPGA

+關注

關注

1643文章

21946瀏覽量

613543 -

芯片

+關注

關注

459文章

52091瀏覽量

435382 -

cpu

+關注

關注

68文章

11028瀏覽量

215816

原文標題:Xilinx FPGA/Vivado開發教程

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA開發Vivado的仿真設計案例分析

FPGA開發如何降低成本,比如利用免費的IP內核

#硬聲創作季 #FPGA Xilinx開發-34 利用Vivado IP Integrator進行設計開發-1

#硬聲創作季 #FPGA Xilinx開發-34 利用Vivado IP Integrator進行設計開發-2

Xilinx FPGA Vivado開發流程介紹

利用FPGA開發板進行ASIC原型開發的技巧

如何讀懂FPGA開發過程中的Vivado時序報告?

如何利用Vivado集成開發環境進行FPGA的應用開發

如何利用Vivado集成開發環境進行FPGA的應用開發

評論