上一期,我們重點學習了ZYNQ的PL開發(fā),本期我們側重于進行PS開發(fā)的學習。我們將在 VIVADO 開發(fā)環(huán)境下搭建 ARM+FPGA 的系統(tǒng)架構,并在 SDK 中編譯軟件實現(xiàn)軟硬件聯(lián)合開發(fā)。

本部分的學習,我們依舊借助得力的助手與伙伴——PYNQ_z2來完成。

一. 實驗目的

1. 點亮開發(fā)板右下角三個燈

2. 輸出“Hello,World!”

二. 實驗要求

1. 在 VIVADO 中編譯 bit 文件;

2. 在 SDK 中編譯 elf 文件并將 FPGA 的 bit 文件和 ARM 處理器 的 elf 文件下載到開發(fā)板中

三. 實驗步驟

1. 啟動 VIVADO

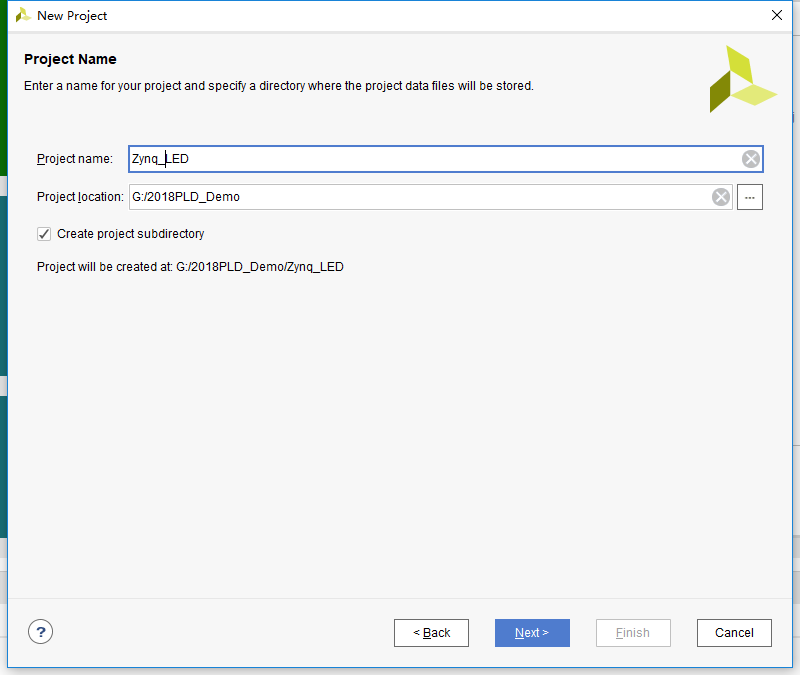

2. 在 File 菜單中選擇 New Project 選項啟動項目向導。填寫所要新建的工程名,然后點擊 Next

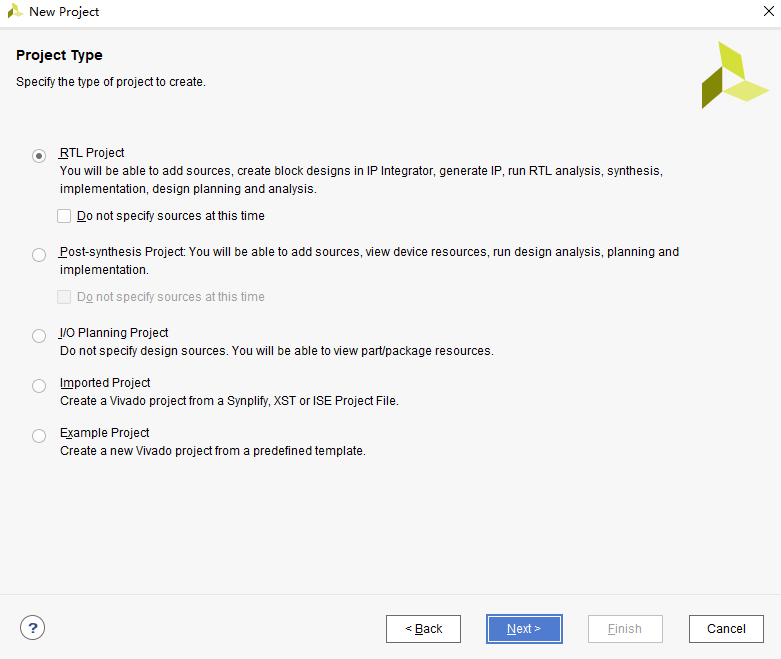

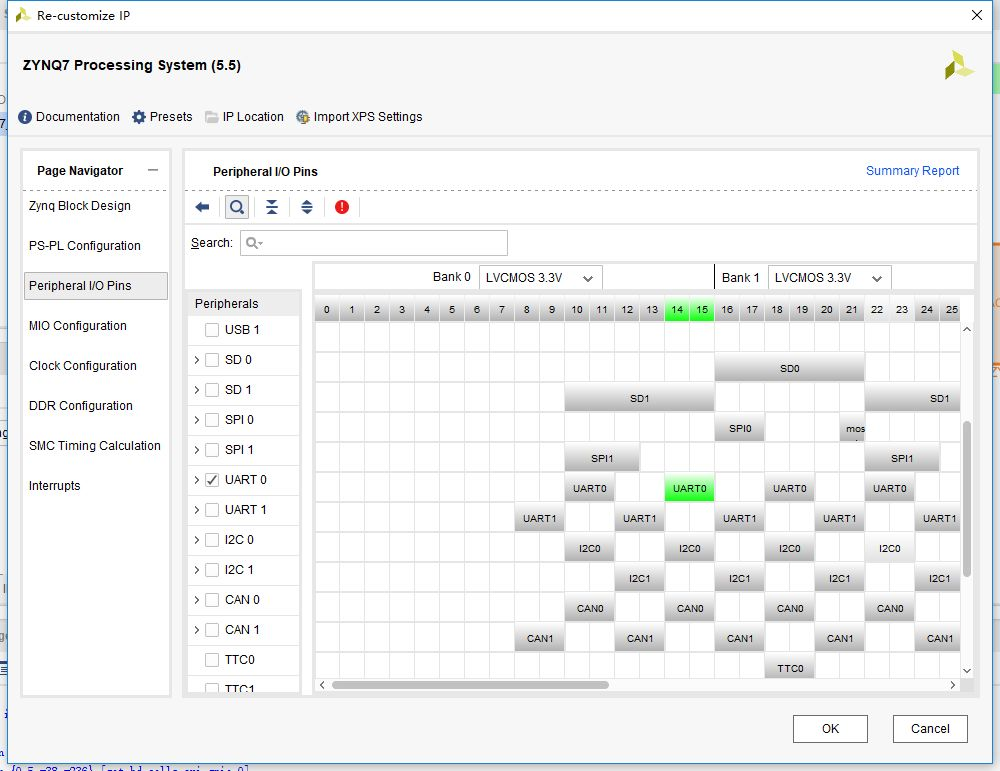

3. 在 File 選擇項目類型

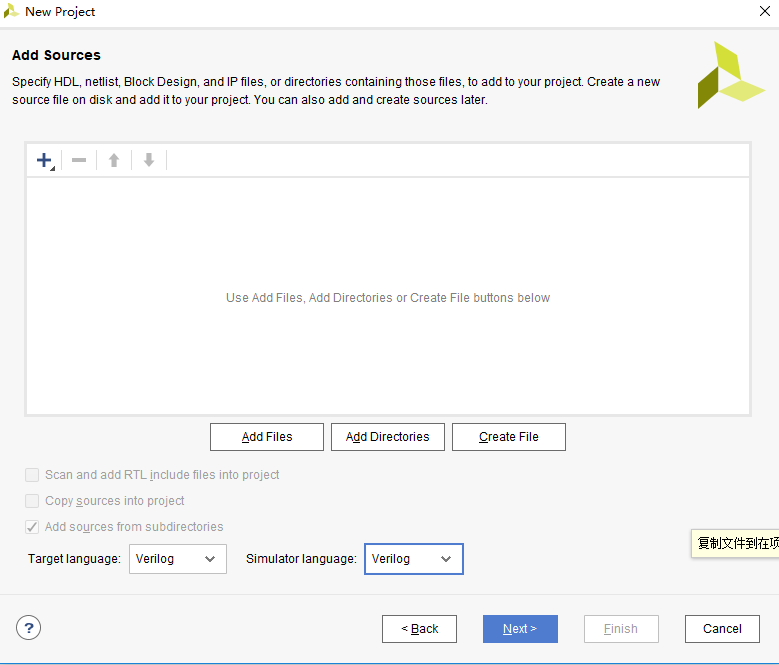

4. 此處默認沒有可以添加的源文件,并且設置編程語言和仿真語言均設置為 Verilog。點擊 Next

5. 沒有可以添加的 IP,所以不添加 IP,直接點擊 Next

6. 沒有可以添加的約束文件,所以不添加,直接點擊 Next

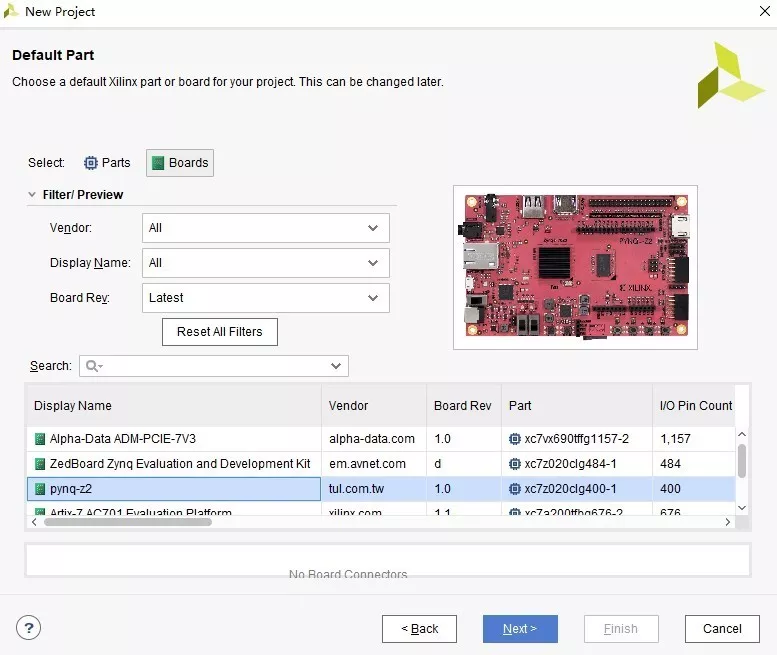

7. 器件的選擇是和實驗平臺的硬件相關的,根據(jù)我們的實驗開發(fā)板,它使用的是 Pynq 的器件,找到相應的器件

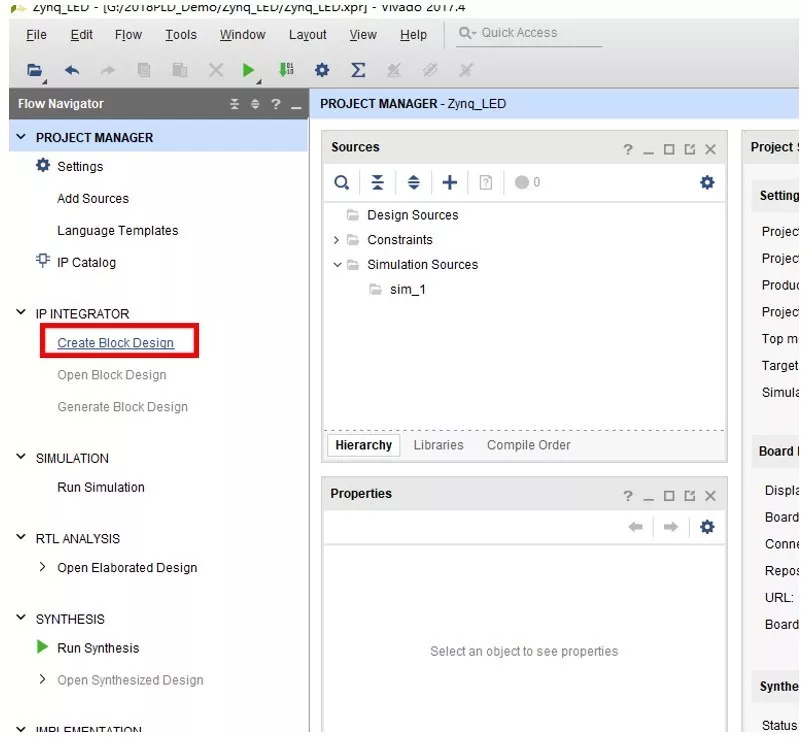

8. 創(chuàng)建 Block Design

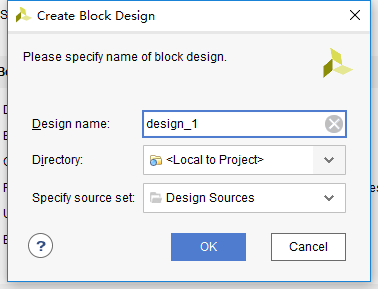

9. 輸入 name,然后 OK

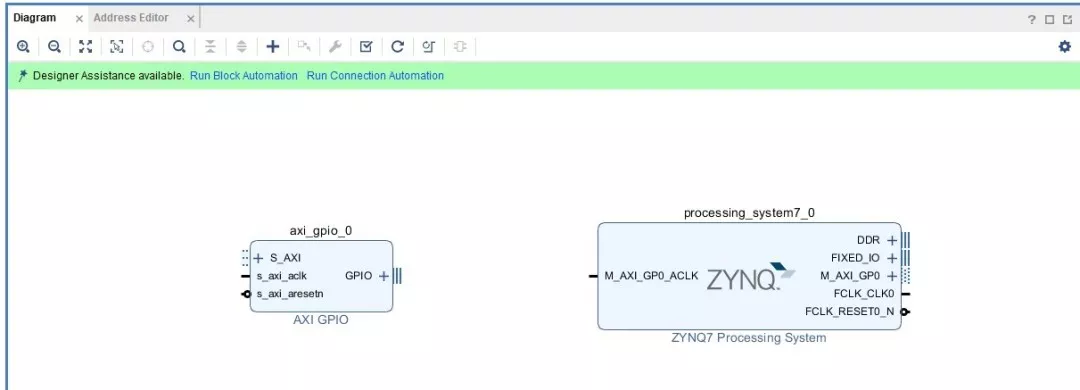

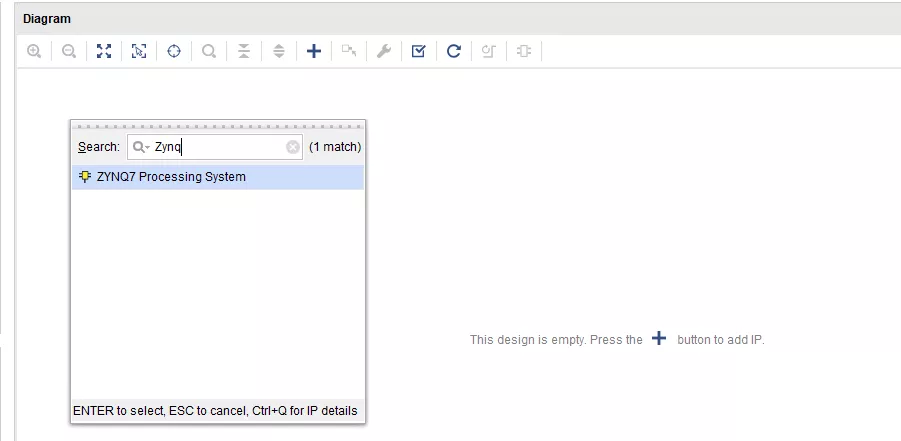

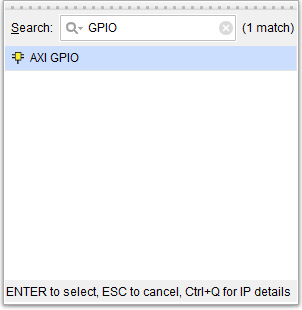

10. 選擇 add IP,輸入 zynq

11. 再次添加 IP,輸入 GPIO

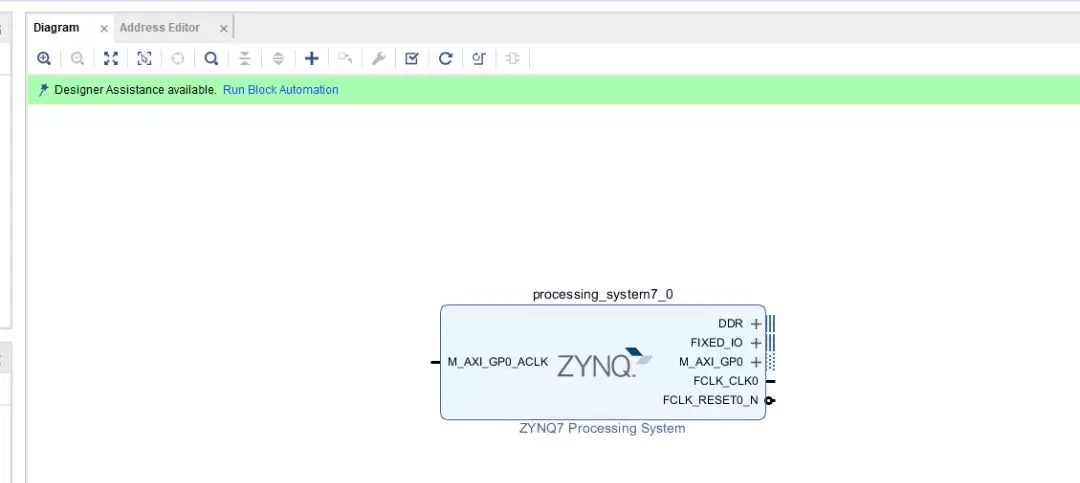

12. 雙擊 Zynq 模塊,勾選上 UART0

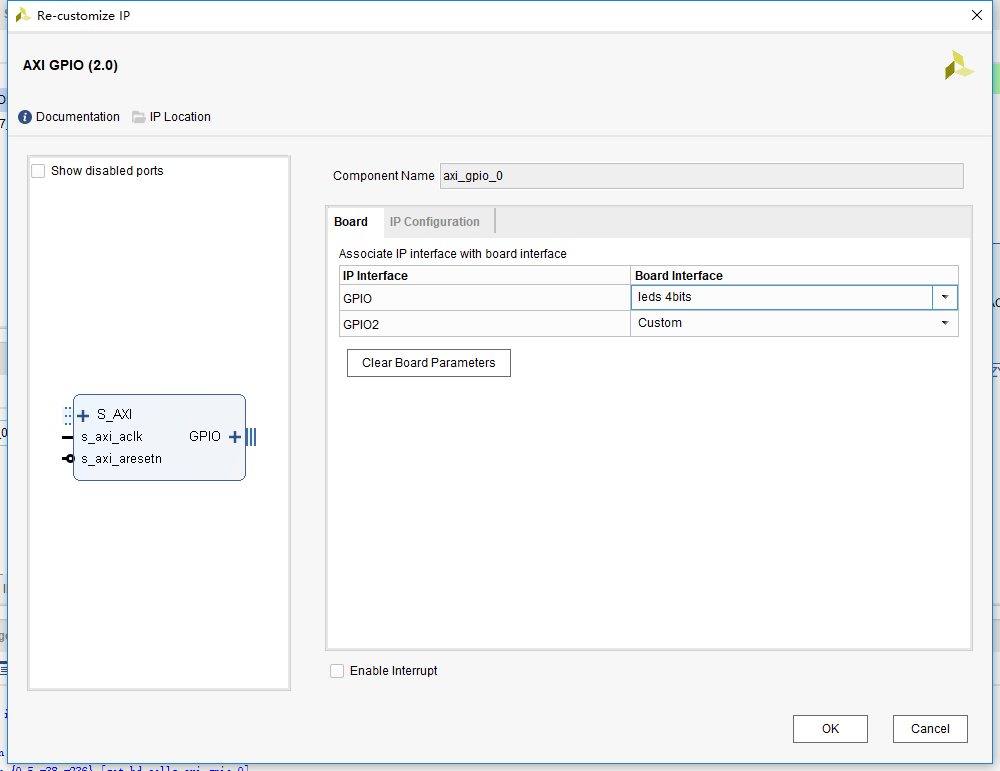

13. 雙擊 GPIO

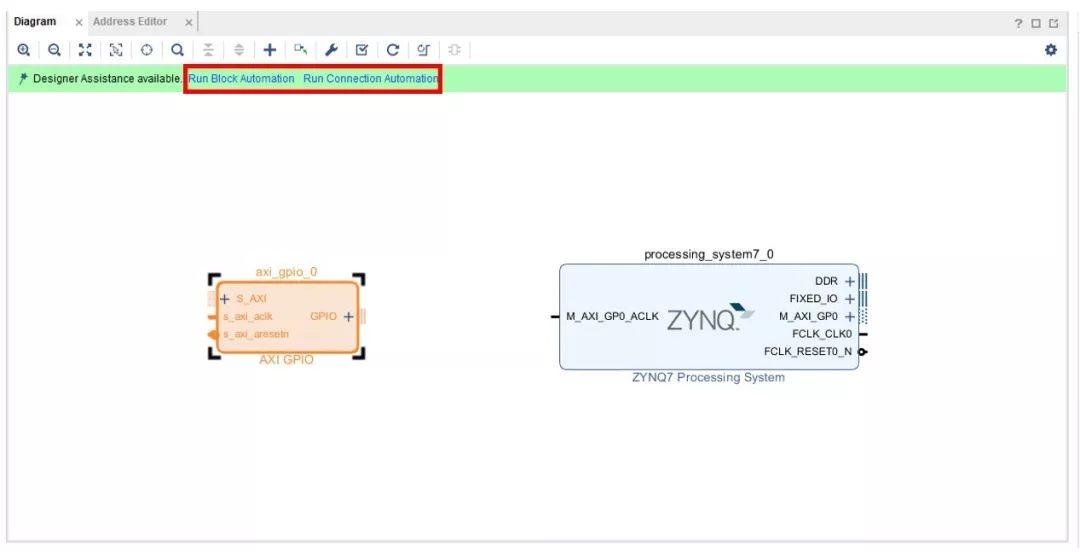

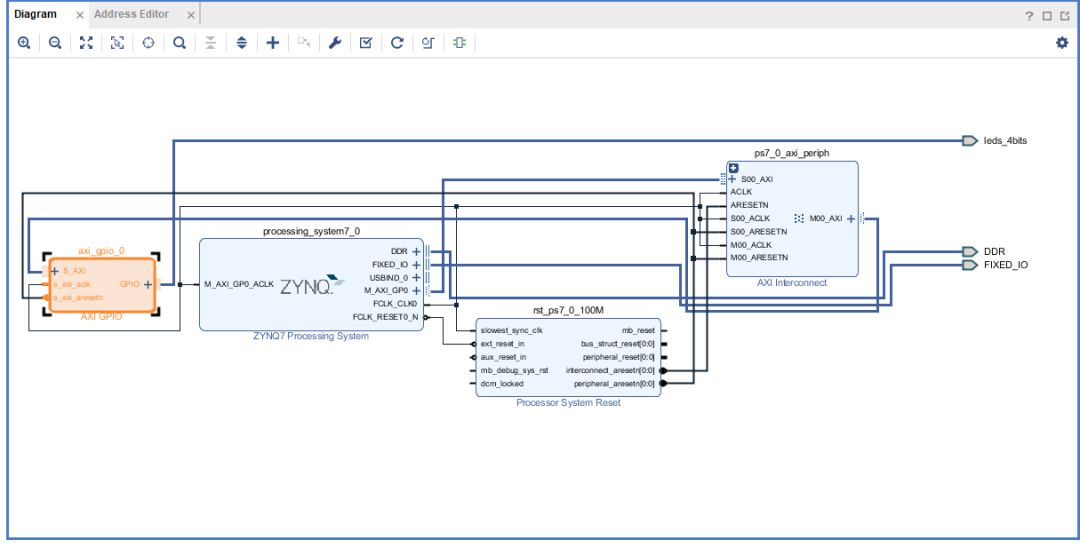

14. 分別點擊Run Block Automation 和 Run Connection Automation

15. 勾選所有候選,然后點 ok

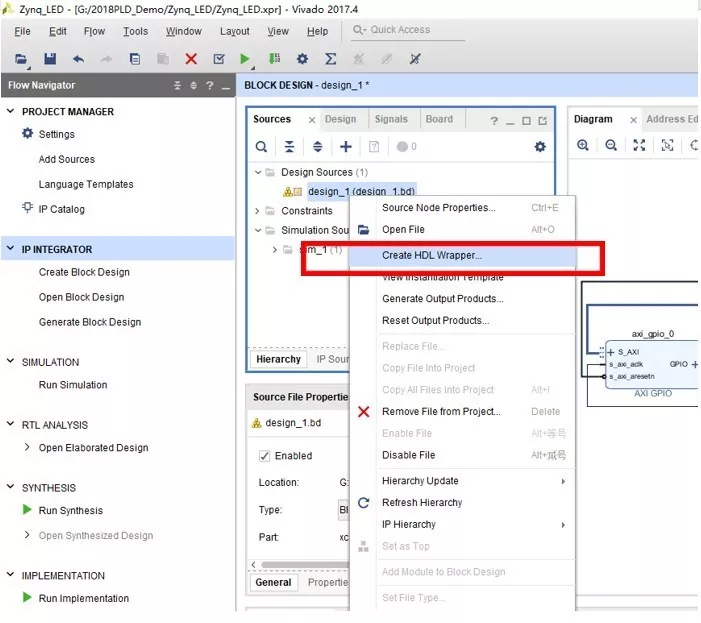

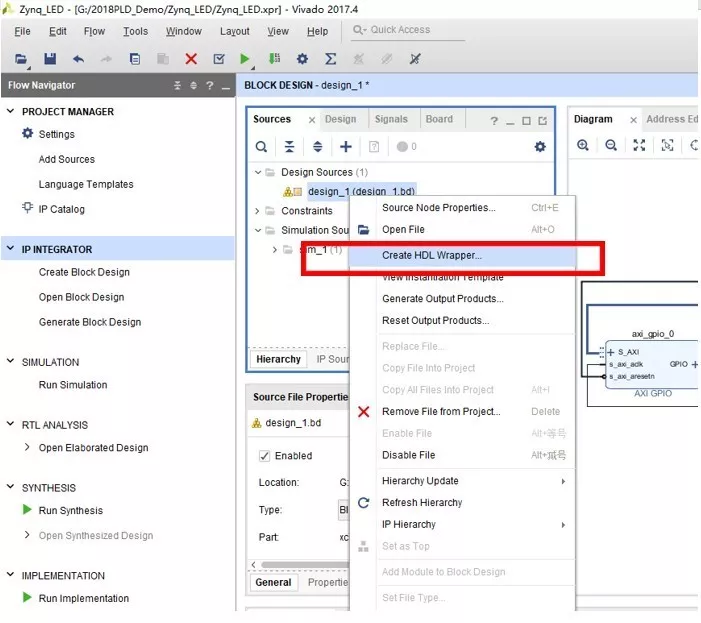

16. 右擊 design_1.bd,create HDL Wrapper

17. 選擇默認第二項,點擊 OK

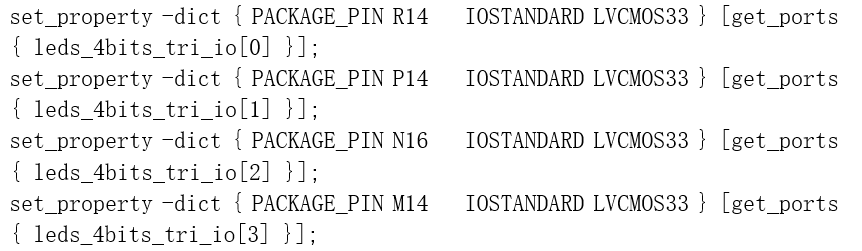

18. 添加引腳約束文件

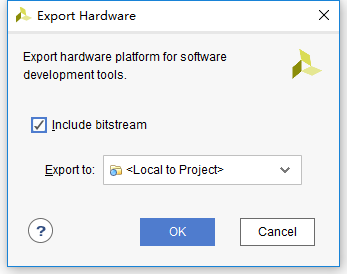

19. 然后直接點擊 Generat Bitstream,等待幾分鐘,編譯完成之后,點擊工具 欄的 File→Export->Export Hardware

20. 勾選 Include bitstream,點擊 OK

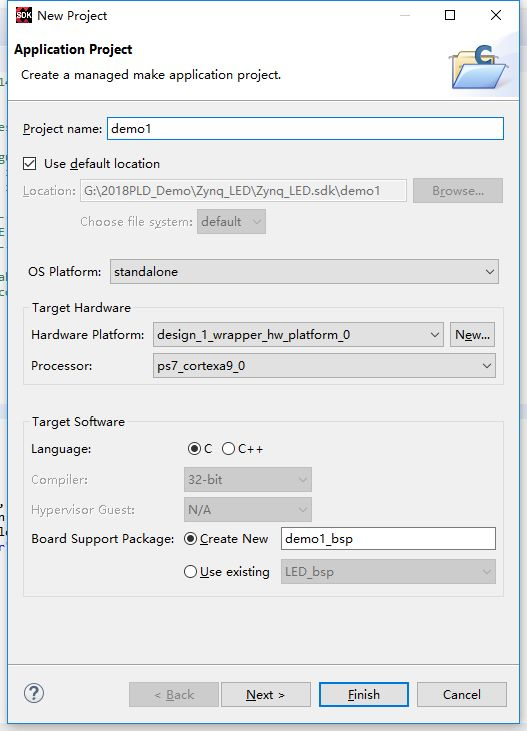

21. 點擊工具欄的 File→lauch SDK,等待 SDK 啟動完成之后,新建工程。

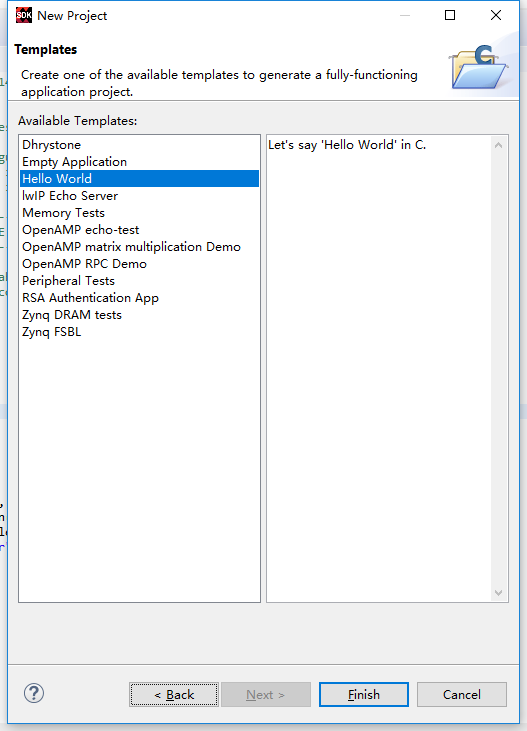

22. 點擊 NEXT,選擇工程類型

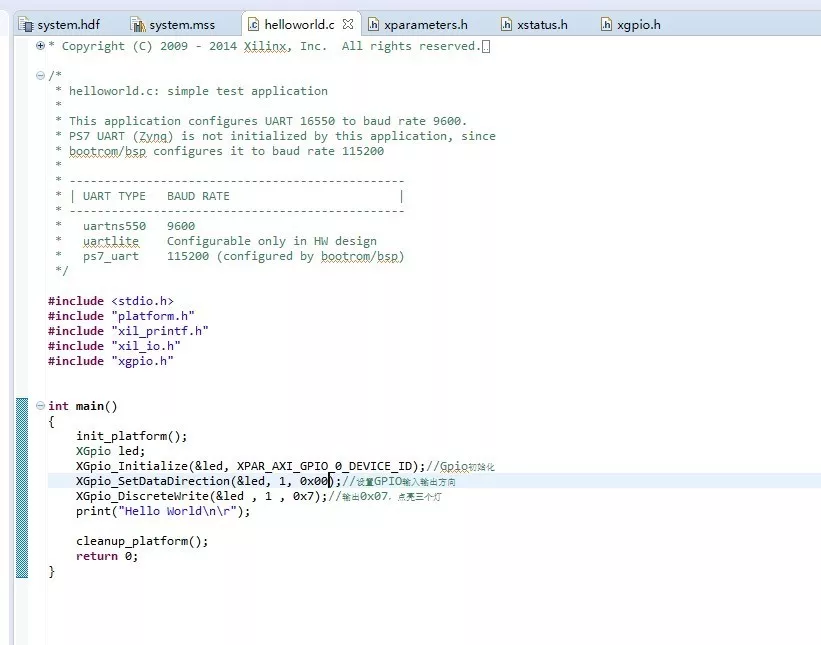

23. 點開 HelloWorld.c,輸入如下代碼:

24. 將開發(fā)板連接到電腦,點擊 program FPGA

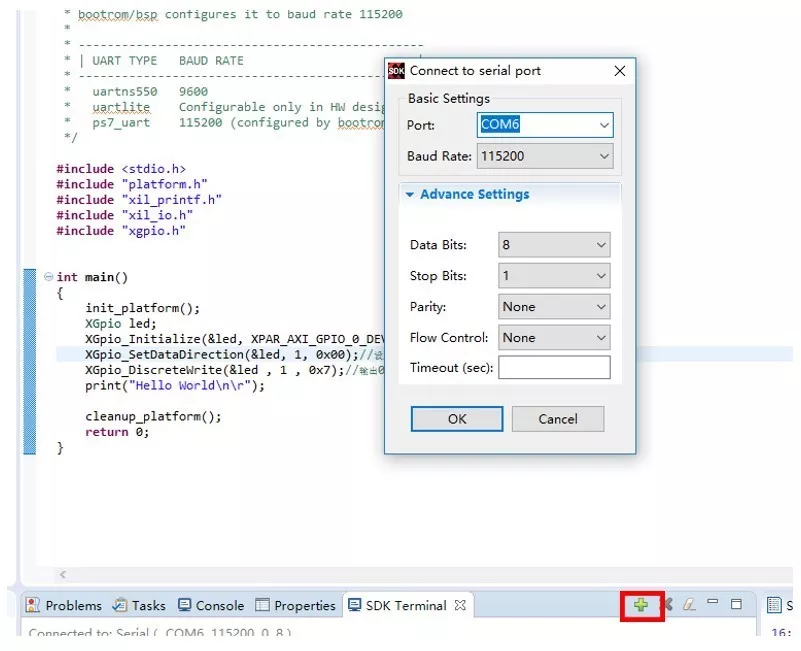

25. 連接串口,com 號在個人電腦的設備管理器中可以查看

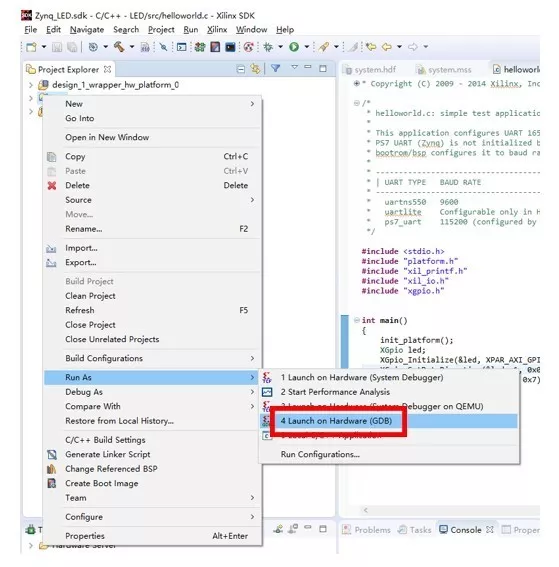

26. 右擊工程目錄,燒寫 C 程序

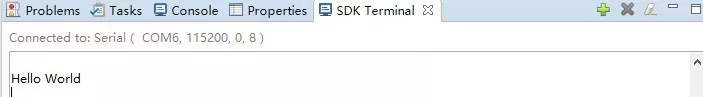

27. 開發(fā)板右下角三個燈點亮,輸出如下:

編輯:hfy

-

FPGA

+關注

關注

1643文章

21965瀏覽量

614119 -

ARM

+關注

關注

134文章

9309瀏覽量

375046 -

Zynq

+關注

關注

10文章

614瀏覽量

48025 -

Vivado

+關注

關注

19文章

829瀏覽量

68229

發(fā)布評論請先 登錄

單片機軟硬件聯(lián)合仿真解決方案

基于FPGA的以太網(wǎng)系統(tǒng)軟硬件實現(xiàn)方案

基于FPGA的以太網(wǎng)系統(tǒng)軟硬件實現(xiàn)方案

基于Altera FPGA的軟硬件協(xié)同仿真方法介紹

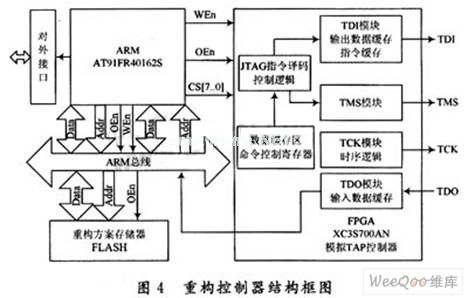

基于ARM+FPGA的重構控制器設計

利用FPGA軟硬件協(xié)同系統(tǒng)驗證SoC系統(tǒng)的過程和方法

基于FPGA的軟硬件協(xié)同測試設計影響因素分析與設計實現(xiàn)

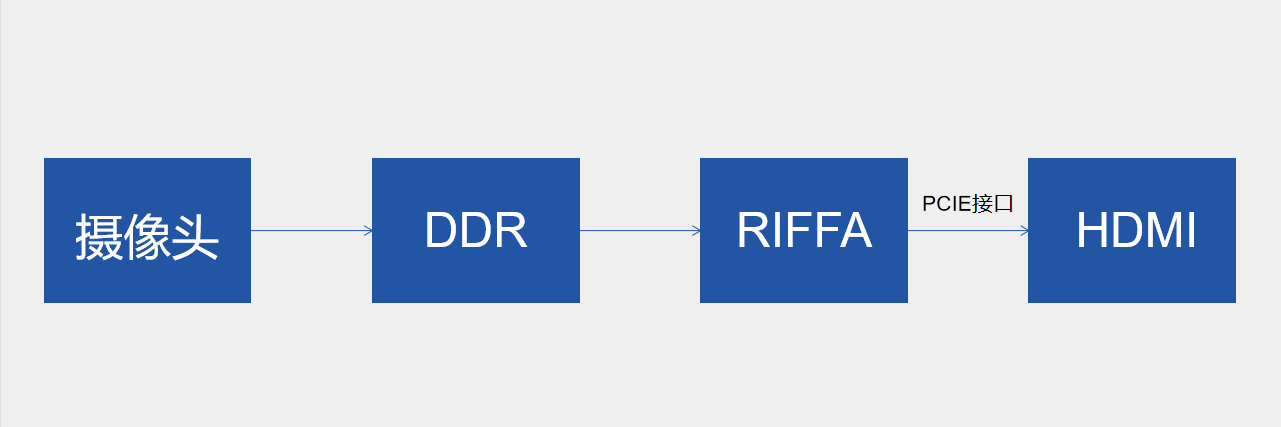

Demo演示:ARM+FPGA主流嵌入式架構板卡-HDMI顯示攝像畫面

米爾ARM+FPGA架構開發(fā)板PCIE2SCREEN示例分析與測試

基于VIVADO搭建ARM+FPGA系統(tǒng)架構實現(xiàn)軟硬件聯(lián)合開發(fā)

基于VIVADO搭建ARM+FPGA系統(tǒng)架構實現(xiàn)軟硬件聯(lián)合開發(fā)

評論