隨著技術的飛速發展,商業、工業及汽車等領域對耐高溫集成電路(IC)的需求持續攀升?。高溫環境會嚴重制約集成電路的性能、可靠性和安全性,亟需通過創新技術手段攻克相關技術難題?。

這份白皮書致力于探討高溫對集成電路的影響,并提供適用于高功率的設計技術以應對這些挑戰。第一篇文章介紹了工作溫度,包括環境溫度和結溫等。第二篇文章介紹了高結溫帶來的挑戰。本文將繼續介紹IC的高溫設計原則。

IC 的高溫設計

?IC 技術

使用適當的元件和設計技術,體硅(Bulk silicon)工藝承受的溫度可達約 200℃至 250℃,而絕緣體上硅 (SOI) 技術的溫度可達 250℃至 300℃。采用特殊技術甚至可以承受更高的溫度,例如砷化鎵(GaAs)可達約 500°C,碳化硅(SiC)可達約 700°C,金剛石可達約 1000°C。

針對高溫應用的 SOI 技術受到了研究和工業界的極大關注。在傳統的 MOS 晶體管中,主要的結泄漏來源是漏極到襯底的漏極結面積導致的。通過采用 SOI CMOS 技術,這種泄漏被有效地消除了。SOI 技術還不會出現閂鎖現象,因為它消除了在傳統 bulk CMOS 工藝中造成閂鎖的寄生雙極。

SOI 技術有很多優點,但也有一些明顯的缺點。主要缺點是制造成本高于傳統硅晶片。這是由于制造絕緣層需要額外的步驟,以及工藝的整體復雜性。絕緣層會增加熱阻(高壓技術需要更厚的埋氧層),這在電氣上隔離了元件,但同時也增加了這些元件向襯底的熱阻。其他影響包括應力差、閾值電壓變化和電荷積累。

基于 65 納米 BCD 技術的安森美(onsemi)Treo 平臺(采用結隔離用于低壓和中壓,深槽隔離用于高壓)提供了一種具有成本效益的解決方案,具備良好的熱管理能力,經驗證可在至少 175°C 結溫下可靠運行,甚至在短時間內可以承受高達200°C的結溫Tj。該平臺基于65納米低壓CMOS構建,可選配中壓和高壓 BCD 模塊。它還針對高溫工作進行了優化。所有器件的認證均已完成,包括評估高溫工作條件下,損耗效應的影響。

?工藝設計包(PDK)

PDK 對 IC 設計至關重要,它提供了一個連接設計和制造的標準化框架。包括制造工藝、器件模型、設計規則和驗證檢查的詳細信息,確保設計符合制造要求及代工廠的規范。為了設計出能夠在高溫下工作的電路,給定技術的 PDK 必須具備高溫下的所有必要數據,包括器件模型、安全工作區、老化模型、電遷移規則和一些附加檢查。

?安全工作區(SOA)

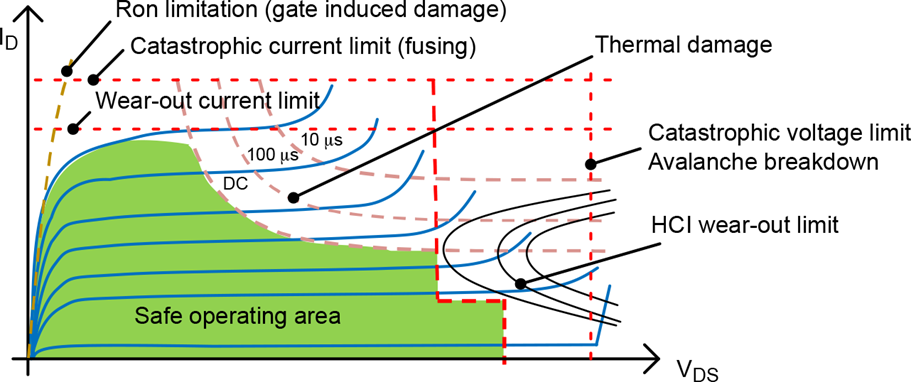

損耗效應的影響在技術器件認證過程中需要被量化,并轉化為電路設計人員可以使用的規則。這些規則包括安全工作區(SOA)。SOA 是指半導體器件在不導致性能下降或損壞的情況下,可以正常工作的電壓和電流范圍。SOA 通常在元器件數據手冊中以圖表形式展示,其中 x 軸表示電壓,y 軸表示電流,曲線下的區域代表安全工作條件。SOA 區域由各種限制條件確定,包括最大電壓、電流、功率耗散、熱載流子退化、柵極氧化物擊穿、二次擊穿和其他機制。

實際驗證一個設計中,所有元器件是否都在安全工作區內工作,需要在器件模型中添加 SOA 條件。在 SPICE 仿真過程中,仿真工具會驗證器件是否超出允許的工作條件。

圖 1. NMOS 晶體管的安全工作區

?老化模型

老化仿真通過模擬單個元器件在高溫、電壓和電流等應力因素作用下隨時間發生的退化,來預測長期可靠性和性能。使用新模型的基線仿真可先確定初始性能。然后利用老化過程仿真來預測退化情況,這可以通過各種應力因素,包括熱載流子退化、負偏置溫度不穩定性(NBTI)和正偏置溫度不穩定性(PBTI)等機制的老化模型。最后,使用老化后的模型進行仿真以評估性能和可靠性,通過比較初始結果和老化后的結果來識別性能上的顯著變化、潛在故障點以及需要改進設計的區域。老化模型是根據在溫度、電壓和電流等各種條件下進行的加速壽命測試所獲得的數據創建的。

?金屬互連

電遷移分析需要根據溫度和電流密度等應力條件下的加速壽命測試建立特性良好的模型。電遷移模型通常基于布萊克方程,有助于在設計過程中確定最小金屬互連寬度和通孔數量。對于中壓(20V 至 45V)和高壓(45V 以上),需要采取特殊的預防措施,如保持足夠的間距以防止介電擊穿和 TDDB。根據所使用的技術,可能還需要跳過薄金屬層來增加具有較高電壓差的金屬層間垂直隔離距離,同時加厚介質層。在布局中驗證較高的金屬間距以及可能跳過的金屬層,需要正確識別電壓域并應用相應的設計規則檢查(DRC)。

?器件模型

安森美 Treo 平臺提供的器件模型涵蓋 -40°C 至 200°C 的寬溫度范圍。所有器件模型均基于在?40°C、0°C、25°C、90°C、150°C 和 200°C 溫度下測量的特征數據。安全工作區檢查覆蓋整個溫度范圍,并支持穩態限制以及瞬態 / 絕對最大限制。老化模型和電遷移模型基于詳細的技術特征數據。布局驗證可自動識別電路中各個線網的電壓域,并為互連和隔離應用相應的設計規則。 所有這些使得 Treo 平臺 BCD65 技術工藝設計包足以應對高溫工作。

?設計技術

在高溫條件下,IC 元器件一般仍能正常工作,但結泄漏會顯著增加。MOS 晶體管的性能會隨著閾值電壓和載流子遷移率的降低而下降,導致亞閾值泄漏增加、跨導降低和導通電阻增大。擴散電阻和多晶硅電阻雖然仍能工作,但它們的電阻值可能會發生變化。薄氧化層電容能保持電容值,但使用擴散電極的擴散電阻和電容的漏電會增加。

各種高溫 CMOS 設計技術已被提出,例如零溫度系數 (ZTC) 偏置。然而,ZTC 高度依賴于工藝,并且僅在有限的溫度范圍內有效,限制了其實際應用。

高溫模擬 IC 設計的一個實用方法是,選擇對泄漏不敏感且性能基于穩定參數(如匹配和電容)的拓撲結構,或可以在溫度范圍內保持穩定的參數,如 MOS 跨導。對于開關電阻等參數,MOS 器件的尺寸應根據最壞情況確定。

利用多閾值 CMOS(在同一集成電路中采用不同閾值電壓的晶體管),可以針對高溫優化數字設計。高 Vt 晶體管可降低非關鍵路徑的漏電功率,而低 Vt 晶體管則可提高關鍵路徑的性能。另一種技術是使用不同的溝道長度:在關鍵路徑中使用較短的溝道以加快開關速度,盡管泄漏電流較高;在非關鍵路徑中使用較長的溝道以降低泄漏電流,這里優先考慮的是能效。

?泄漏

高溫下工作電路的設計技巧包括:

使用對泄漏不敏感的拓撲結構和差分設計

識別泄漏敏感節點

減少敏感結區

減少敏感結周圍中性區的體積

補償泄漏電流

使用有源屏蔽

用足夠大的電流偏置電路,以限制漏電流的影響

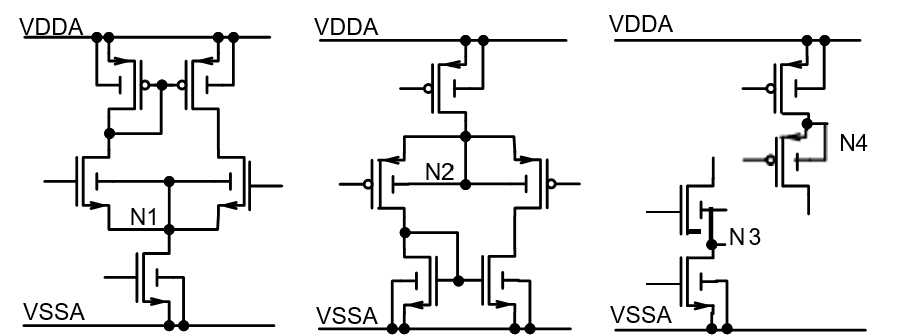

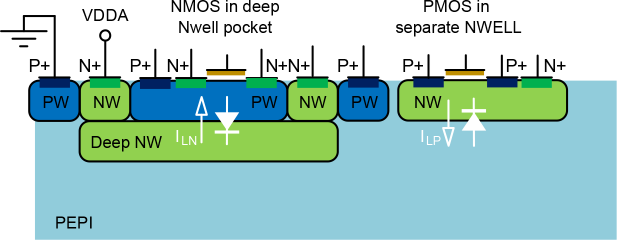

不僅 MOS 晶體管的漏極和源極結會泄漏到體區,還需要考慮阱區泄漏。如果 N 阱區連接到電源,而 P 阱區接地,則這些阱之間的泄漏會影響電路的電流消耗,但不會直接影響功能。另一種情況是 N 阱區或 P 阱區連接到信號節點。這樣的連接示例包括差分對晶體管的偏置,其中體區連接到源極而不是電源或地,如圖 2 所示。在這種情況下,N 阱區或 P 阱區連接到信號,高溫下較高的泄漏會對差分對的偏置產生負面影響。如果共源共柵晶體管的體區連接到源極(例如,為了電壓空間),電流鏡也會出現類似情況,連接阱區的泄漏會在高溫下影響電流鏡的輸出電流。

圖 2. N 阱區(N2 和 N4)或 P 阱區(N1 和 N3)連接到信號網絡的示意圖

圖 3. 顯示阱泄漏路徑的截面圖

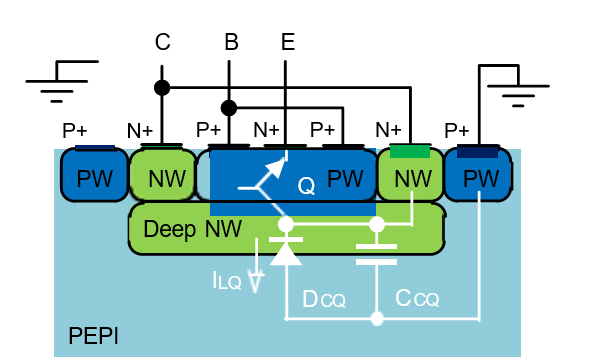

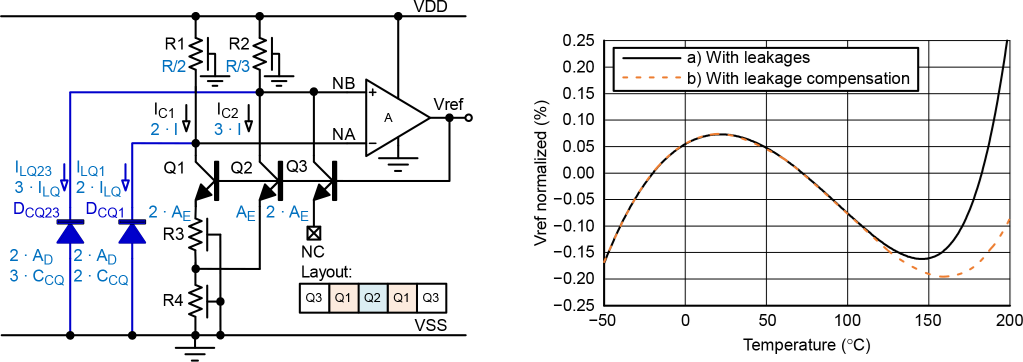

另一個例子是用于禁帶參考電路中的雙極結型晶體管(BJT)的集電極結泄漏。在 CMOS 工藝中,垂直 NPN 型 BJT 可能會使用深 N 阱作為集電結。圖 4 展示了一種采用深 N 阱技術的垂直 NPN 型 BJT 的簡化截面圖。垂直 NPN 晶體管的集電極通過反極化結二極管 DCQ 與接地的 PEPI 隔離。這個二極管的泄漏電流影響輸出電壓的準確性,特別是禁帶核心在高于 150°C,以低偏置電流工作時。

圖 4. 芯片中垂直 NPN 型 BJT 的簡化截面圖

禁帶參考電壓源的原理是在其內核中使用不同偏置的晶體管。一種常見的技術是在核心的兩個分支中使用不同數量的晶體管,這會產生漏電差,在高溫下會對參考的準確性產生負面影響。集電極泄漏補償的思想是使泄漏電流的比例與工作中集電極電流的比例相同。可通過在禁帶核心添加沒有實際功能的填充(dummy)晶體管(如圖 5 所示)來實現。

圖 5. 帶泄漏補償的 Brokaw 禁帶核心及帶與不帶泄漏補償的禁帶輸出電壓的溫度相關性

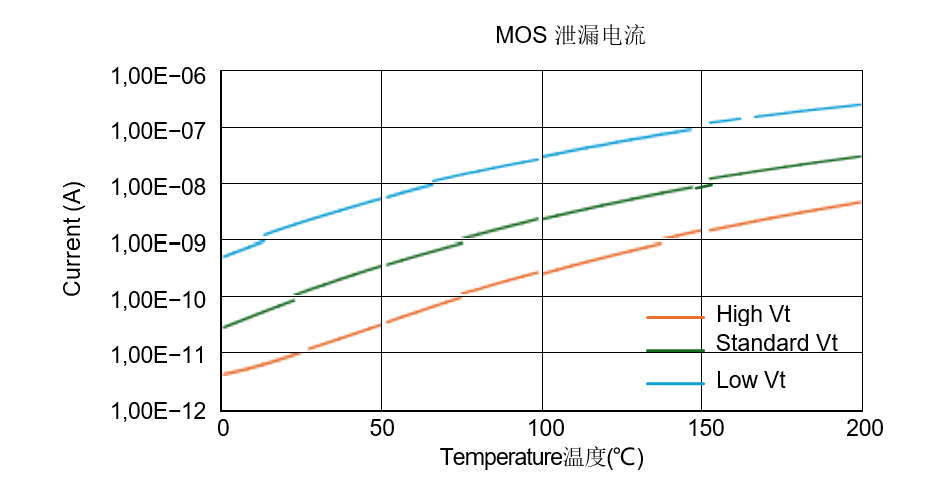

亞閾值溝道泄漏的影響可以通過多種設計技術來減小。如果 IC 技術能夠提供具有不同閾值電壓的多種 MOS 晶體管,選用較高閾值電壓的晶體管可以有效減少泄漏。然而,這種方法可能會犧牲模擬電路所需的電壓空間,并且對于數字電路而言,會導致開關速度變慢。因此,可以在非關鍵路徑中使用高閾值晶體管以減少泄漏,同時在關鍵路徑中采用低閾值晶體管以保持較高的開關速度或保留必要的電壓空間(如圖 6 所示)。

圖 6. 不同類型 NMOS 晶體管的泄漏

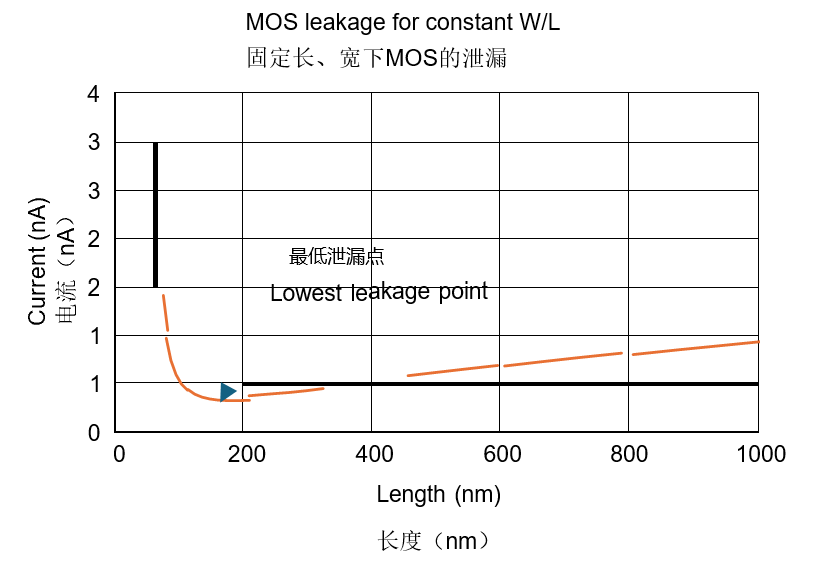

選擇適當尺寸的晶體管有助于平衡亞閾值泄漏、結泄漏和性能之間的關系。增加晶體管的長度 (L) 可以減少亞閾值泄漏,但為了保持相同的導通電阻或跨導,也需要增加寬度 (W),但這也會隨著漏極結面積的增加而增加結泄漏。這種技術既適用于模擬電路也適用于數字電路。

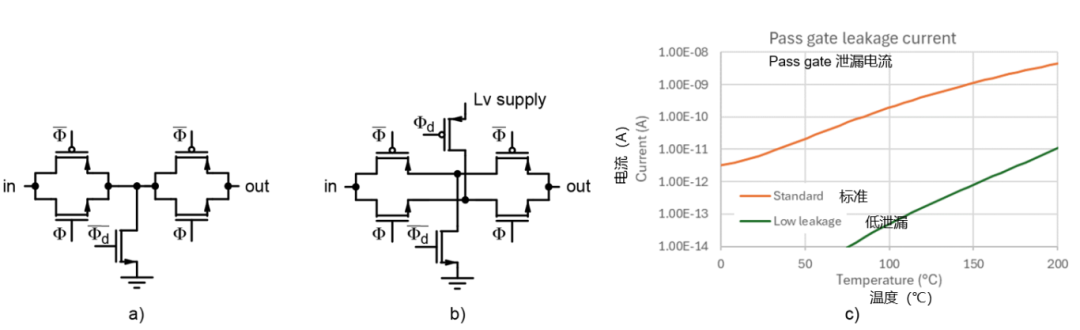

圖 7. 晶體管尺寸對泄漏的影響,以確定最優長度

另一種減少泄漏的技術是體偏置(body biasing)。通過給晶體管的體區(bulk/body)施加反向偏置,可以增加閾值電壓,從而減少泄漏。這種技術的一種改進不需要專門的體區連接、負電壓或特殊偏置,而是一種簡單的技術,即將傳遞門(pass-gate)開關的源極偏置電壓高于柵極電壓。這種方法可應用于工作于電源電壓中值區域的開關電路,例如當 MOS 管的第二端被偏置至更高電位時,此時柵極與體區電壓可顯著低于源極 - 漏極電位。下述電路示例是一個 pass-gate T 型開關。標準配置如圖 8a 所示,中間節點偏置晶體管的配置則如圖 8b 所示。

圖 8. 標準配置下的 T 型開關與減少泄漏的 T 型開關

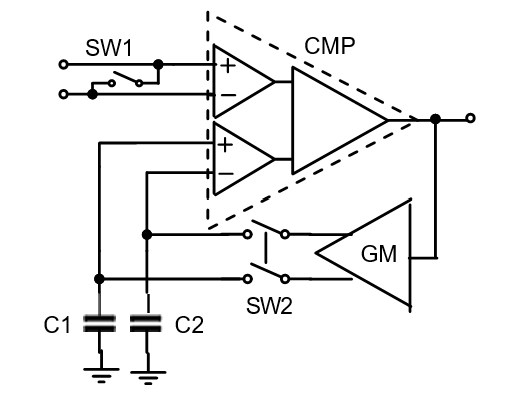

通過使用不同的拓撲結構和技術,替換對泄漏敏感的電路可以緩解泄漏問題。例如,在模擬偏移補償或自動歸零中,會定期測量偏移量并將其存儲在電容器上,以便在工作過程中校正電路的偏移。挑戰在于模擬電壓需要存儲在一個電容器上,而連接到這個電容的開關的泄漏會影響存儲的電壓。如果電路僅在下一次偏移補償周期之前短暫地以補償后的偏移工作,那么存儲偏移的電容器的放電可以忽略不計。然而,隨著溫度升高或存儲時間延長,泄漏變得更加嚴重,導致存儲偏移的電容器放電,產生不必要的偏移。

一種提高性能的技術是使用差分結構,將偏移作為電壓差存儲在兩個電容器上,見圖 7。 這種方法可以補償對稱的放電。 然而,隨著時間的增加,保持電容器上的電壓變得更具挑戰性,這就需要更大的電容器和更小的開關泄漏。 較大的電容器需要更大的電流充電,占用的空間也更大。 此外,可能需要更大的開關來為這些電容器充電,但它們的泄漏電流往往更高。差分結構提高了模擬電路對對稱干擾和高溫的穩健性。可以部分補償對稱耦合泄漏。

圖 7. 帶有差分模擬偏移補償的比較器的框圖

另一種技術是數字偏移補償,即以數字方式存儲偏移信息,從而消除高溫下的泄漏問題。 如有需要,還可采用斬波來消除殘余偏移。

對于某些特殊類型的器件,如雙擴散 MOS(DMOS),其漏極可以連接到深 N 阱或口袋區,這種結構中的泄漏可能會影響電路性能。可以通過設計一種電路來補償這種泄漏,該電路利用一個類似的結構產生匹配的泄漏(可能通過面積比實現)。然后,這種匹配的泄漏會被鏡像并從不需要的泄漏中減去。泄漏補償電路僅在高溫時激活,從而在低溫或中溫條件下節省電流消耗。

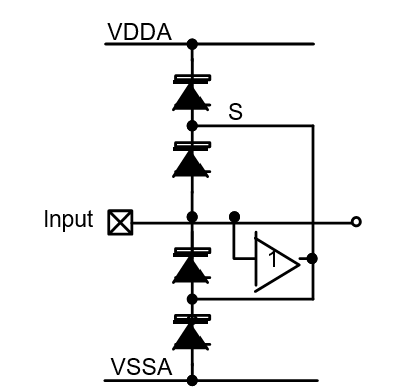

有源屏蔽可以減少或消除泄漏,特別是 IC 輸入引腳,這里在高溫下需要低泄漏。這需要在正負極上串聯兩個 ESD 保護二極管,中間點通過與輸入電壓相同的緩沖器保持激活狀態(圖 10)。 這樣可確保 ESD 二極管兩端的電壓為零,從而使通過二極管的泄漏為零。請注意,這要求 ESD 二極管的結連接到 IC 引腳,并且沒有其他通往下方阱區的泄漏路徑。這一原理也可應用于其他電路,如消除溝道漏電的開關或非常敏感的線網上的天線二極管。

圖 10. 輸入 ESD 保護泄漏的有源屏蔽

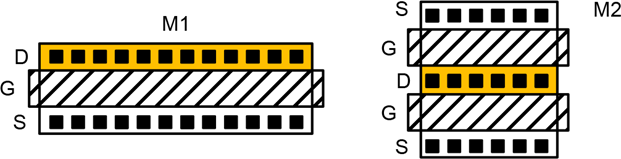

結泄漏取決于結的尺寸,而一些簡單且熟知的布局技術有助于減少泄漏。例如,采用叉指晶體管配置可以將最容易發生泄漏的部分(通常是漏極)放置在結構的中間,從而減少大約50%的泄漏。其他MOS布局類型,如華夫格、圓形或環形布局,也可以最小化泄漏和其他寄生效應。

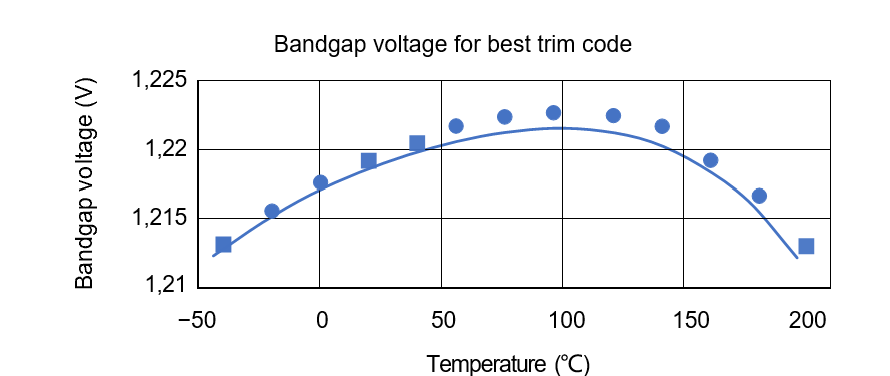

圖 11. 減少漏極面積的 MOS 單指和雙指布局

安森美的 Treo 平臺 IP 采用了上述多種技術,設計適用于較寬的溫度范圍。圖 12 展示了采用 BCD65 技術設計的襯底為 PNP Kuijk 禁帶參考的溫度依賴性示例。禁帶核心的每個分支均以 3.6μA 電流偏置。這證明了該技術的卓越性能,因為禁帶電壓在高溫下沒有出現精度下降,即使沒有特殊的泄漏補償技術也是如此。

圖 12. 測量 BCD65 禁帶電壓在不同溫度下的表現,以確定最佳的修調碼(Trimming Code)

?恒定 gm偏置

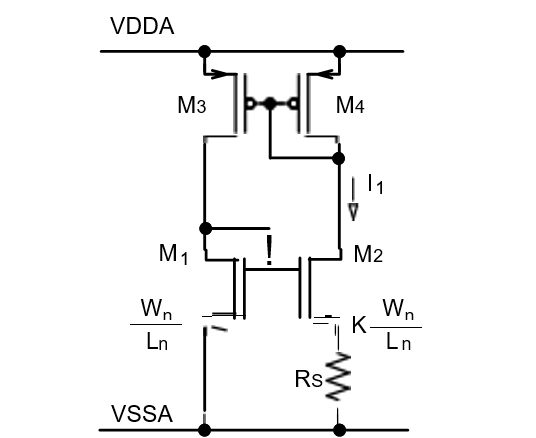

在模擬電路中,MOS 晶體管的跨導可能是該器件最重要的參數,它直接影響諸如放大器增益等性能。無論工藝參數、溫度和電源電壓如何變化,恒定 gm偏置技術都能保持 MOS 的恒定跨導。通過使用與載流子遷移率成反比的偏置電流,可以實現穩定 gm。圖 13 中的電路帶有與溫度無關的電阻 Rs,可以產生一個偏置電流 I1,在溫度、MOS 工藝、電源電壓等條件下保持恒定的跨導。

圖 13. 用于恒定 gm偏置的偏置電路

恒定 gm偏置可用于性能與跨導 gm直接相關的電路。一個典型的例子是 gm/C 濾波器,其性能取決于 gm/C 比值。由于電容 C 在很大程度上與溫度無關,保持 gm恒定確保了電路在溫度變化時的穩定性。這種技術可用于創建溫度穩定的模擬電路,如濾波器、振蕩器、積分器、鎖相環和 ADC。在高溫條件下,恒定 gm偏置會增加偏置電流,這也有助于抵消隨著溫度升高而增加的泄漏電流。

?電源電壓

電源電壓會影響多種損耗機制。其中一種機制是經時擊穿(TDDB),可通過降低電源電壓來緩解。降低電源電壓會減少介電材料上的電場,從而成倍地延長介電材料的使用壽命。對于負偏壓和正偏壓溫度不穩定性,降低電源電壓可減少柵極氧化物上的電場,從而延長器件的使用壽命。電場的降低減緩了老化過程,有助于在更長時間內保持集成電路的性能和可靠性。此外,較低的電源電壓還能減少其他損耗機制,如熱載流子退化和電遷移,從而提高電路的整體穩健性和使用壽命。

Treo 平臺適用于厚柵極氧化層晶體管,這些晶體管能夠在 3.3V 的標稱供電下工作,但在高溫、高可靠性產品中使用了較低或中等的 2.5V 電源電壓。這顯著增強了這些晶體管的壽命和可靠性。降低電源電壓可以減少晶體管上的電場應力,從而緩解諸如 TDDB、負偏置和正偏置溫度不穩定性和熱載流子退化等老化機制。較低的電源電壓有助于降低功耗和發熱量,從而進一步提高 IC 的整體效率和耐用性。

-

集成電路

+關注

關注

5420文章

11954瀏覽量

367175 -

安森美

+關注

關注

32文章

1771瀏覽量

92824 -

IC設計

+關注

關注

38文章

1347瀏覽量

105254 -

晶體管

+關注

關注

77文章

9979瀏覽量

140673 -

BCD

+關注

關注

1文章

91瀏覽量

30478

原文標題:高溫IC設計必看:基于Treo平臺的高溫模擬與混合信號解決方案

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

IC封裝術語解析

高溫IC設計學習筆記之環境溫度和結溫

高溫電路設計的幾條建議

有可以耐高溫的ic型號推薦嗎?

電源IC的選擇基本原則

電子元器件基礎知識大全:IC測試原理解析

高溫系統設計的考慮因素

FPGA設計的十五條原則詳細解析

pcb如何布局?pcb大量元件如何布局?pcb布局原則解析

選擇IC芯片的原則

解析 MEMS 車載與高溫振蕩器 SiT8920 系列 1 to 110 MHz 的卓越特性

電源常用ic腳位解析方法 7腳電源芯片怎么看型號

探索高溫試驗箱:應用與使用解析

高溫IC設計原則解析

高溫IC設計原則解析

評論