隨著技術的飛速發展,商業、工業及汽車等領域對耐高溫集成電路(IC)的需求持續攀升?。高溫環境會嚴重制約集成電路的性能、可靠性和安全性,亟需通過創新技術手段攻克相關技術難題?。

這份白皮書致力于探討高溫對集成電路的影響,并提供適用于高功率的設計技術以應對這些挑戰。第一篇文章介紹了工作溫度,包括環境溫度和結溫等。本文將繼續介紹高結溫帶來的挑戰。

高結溫帶來的挑戰

半導體器件在較高溫度下工作會降低電路性能,縮短使用壽命。對于硅基半導體而言,晶體管參數會隨著溫度的升高而下降,由于本征載流子密度的影響,最高極限會低于 300℃。依靠選擇性摻雜的器件可能會失效或性能不佳。

影響 IC 在高溫下工作的主要技術挑戰包括:

泄漏電流增加

MOS 晶體管閾值電壓降低

載流子遷移率降低

提高閂鎖效應(Latch-Up)敏感性

加速損耗機制

對封裝和接合可靠性的挑戰

要設計出能夠在高溫下工作的 IC,了解高溫下面臨的挑戰至關重要。下文將探討 IC 設計面臨的挑戰。

1.泄漏電流增加

CMOS 電路中泄漏電流的增加主要是由半導體 PN 結泄漏和亞閾值溝道泄漏的增加引起的。

反向偏置 PN 結泄漏

在較高溫度下,半導體中熱能的增加會導致更多電子 - 空穴對的產生,從而產生更高的泄露電流。結泄漏取決于摻雜水平,通常隨溫度呈指數增長。根據廣泛使用的經驗法則,溫度每升高 10℃,結電流大約增加一倍。

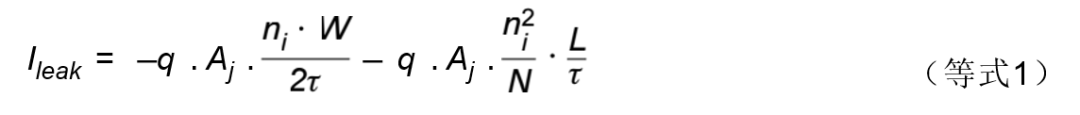

二極管的泄漏電流由漂移電流和擴散電流組成:

其中, q 為電子的基本電荷, Aj為結面積,ni為本征載流子濃度,W 為耗盡區寬度,τ 為有效少數載流子壽命,L 為擴散長度,N 為中性區摻雜密度。

在中等溫度下,泄漏電流主要由耗盡區中電子 - 空穴對產生的熱引起。在高溫下,泄漏電流主要由中性區產生的少數載流子引起。漂移電流與耗盡區寬度成正比,這意味著它與結電壓的平方根成正比(在正常反向電壓下),而擴散電流與結電壓無關,并且與摻雜密度 N 成反比。摻雜水平越高,在溫度高于約 150°C 時擴散泄漏越少。

泄漏電流的指數增加影響了大多數主動器件(如雙極晶體管、MOS 晶體管、二極管)和一些被動器件(如擴散電容、電阻)。然而,由氧化物隔離的器件,例如多晶硅電阻、多晶硅二極管、ploy-poly 電容和 metal-metal 電容,并不受結泄漏的影響。結泄漏被認為是高溫 bulk CMOS 電路中最嚴峻的挑戰。

亞閾值溝道泄漏

MOS 晶體管關閉時,柵極 - 源極電壓 VGS 通常設置為零。由于漏極至源極電壓 VDS 非零,因此漏極和源極之間會有小電流流過。當 Vgs 低于閾值電壓 Vt 時,即在亞閾值或弱反型區,就會發生亞閾值泄漏。該區域的漏極源極電流并不為零,而是與 Vgs 呈指數關系,主要原因是少數載流子的擴散。

該電流在很大程度上取決于溫度、工藝、晶體管尺寸和類型。短溝道晶體管的電流會增大,閾值電壓較高的晶體管的電流會減小。亞閾值斜率因子 S 描述了晶體管從關斷(低電流)切換到導通(高電流)的有效程度,定義為使漏極電流變化十倍所需改變的 VGS 的變化量:

其中,n 是亞閾值斜率系數(通常約為 1.5)。對于 n = 1,斜率因子為 60mV/10 倍,這意味著每低于閾值電壓 Vt 60mV,漏極電流就會減少十倍。典型的 n = 1.5 意味著電流下降速度較慢,為 90mV/10 倍。為了能夠有效地關閉 MOS 晶體管并減少亞閾值泄漏,柵極電壓必須降到足夠低于閾值電壓的水平。

柵極氧化層隧穿泄露

對于極薄的柵極氧化層(厚度低于約 3 納米),必須考慮隧穿泄漏電流的影響。這種電流與溫度有關,由多種機制引發。Fowler-Nordheim 遂穿是在高電場作用下,電子通過氧化層形成的三角形勢壘時產生。隨著有效勢壘高度降低,隧道電流隨溫度升高而增大。較高的溫度也會增強 trap-assisted 隧穿現象,即電子借助氧化層中的中間陷阱態通過。對于超薄氧化層,直接隧穿變得顯著,由于電子熱能的增加,隧穿概率也隨之上升。

2.閾值電壓降低

MOS 晶體管的閾值電壓 Vt 與溫度密切相關,通常隨著溫度的升高而線性降低。這是由于本征載流子濃度增加、半導體禁帶變窄、半導體 - 氧化物界面的表面電位的變化以及載流子遷移率降低等因素造成的。溫度升高導致的閾值電壓降低會引起亞閾值漏電流呈指數增長。

3.載流子遷移率下降

載流子遷移率直接影響 MOS 晶體管的性能,其受晶格散射與雜質散射的影響。溫度升高時,晶格振動(聲子)加劇,導致電荷載流子的散射更加頻繁,遷移率隨之下降。此外,高溫還會增加本征載流子濃度,引發更多的載流子 - 載流子散射,進一步降低遷移率。當溫度從 25°C 升高到 200°C 時,載流子遷移率大約會減半。

載流子遷移率顯著影響多個關鍵的 MOS 參數。載流子遷移率的下降會降低驅動電流,減少晶體管的開關速度和整體性能。更高的導通電阻會增加功率損耗并降低效率。較低的遷移率還會降低跨導,使亞閾值斜率變緩(增加亞閾值泄漏),降低載流子飽和速度(對于短溝道器件至關重要),并間接影響閾值電壓。

4.提高閂鎖效應敏感性

集成電路中各個二極管、晶體管和其他元件之間的隔離是通過反向偏置 P-N 結來實現的。在電路開發過程中,需采取預防措施以確保這些結在預期應用條件下始終可靠阻斷。這些 P-N 結與其他相鄰結形成 N-P-N 和 P-N-P 結構,從而產生寄生 NPN 或 PNP 晶體管,這些晶體管可能會被意外激活。

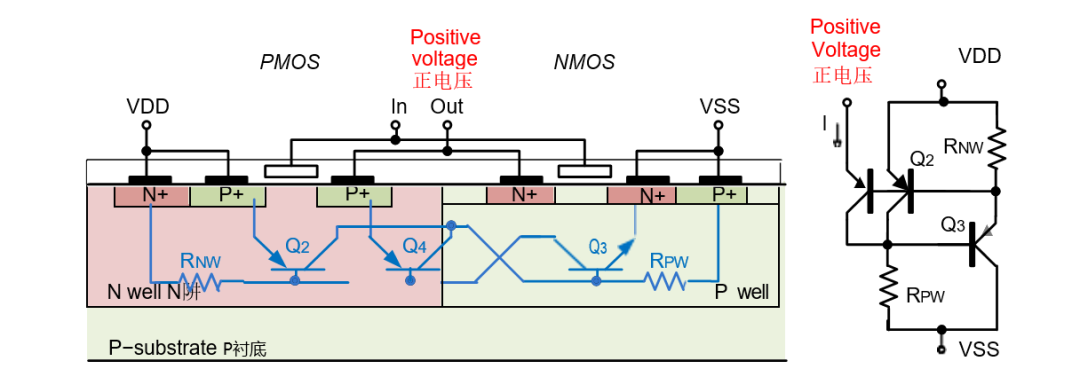

當寄生 PNP 和 NPN 雙極晶體管相互作用,在電源軌和接地之間形成低阻抗路徑時,CMOS IC 中就會出現閂鎖效應(Latch-up)。這會形成一個具有正反饋的可控硅整流器(SCR),導致過大的電流流動,并可能造成永久性器件損壞。圖 1 顯示了標準 CMOS 逆變器的布局截面圖。圖中還包含寄生 NPN 和 PNP 晶體管。正常工作時,所有結均為反向偏置。

圖 1. 帶標記的寄生雙極晶體管逆變器截面圖和寄生雙極晶體管示意圖

閂鎖效應的激活主要取決于寄生 NPN 和 PNP 晶體管的 β 值,以及 N - 阱、P - 阱和襯底電阻。隨著溫度的升高,雙極晶體管的直流電流增益(β)以及阱和襯底的電阻也會增加。

在高溫條件下,閂鎖效應靈敏度的增加也可以視為雙極結型晶體管(BJT)閾值電壓的降低,從而更容易在阱和襯底電阻上產生足以激活寄生雙極晶體管的壓降。基極 - 發射極電壓隨溫度變化降低的幅度約為 -2mV/℃,當溫度從 25℃升至 200℃時,基極 - 發射極電壓降低 350mV。室溫下的典型閾值電壓為 0.7V,這意味著閾值電壓大約減半。

5.加速損耗機制

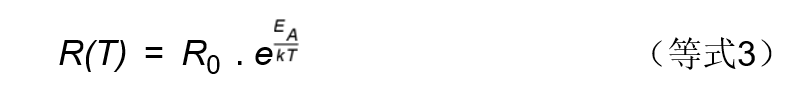

Arrhenius 定律在可靠性工程中被廣泛用于模擬溫度對材料和元器件失效率的影響。

其中,R( T) 是速率常數,Ea 是活化能,k 是玻爾茲曼常數(8.617 · 10?5eV/K),T 為絕對溫度(單位:開爾文)。通常,每升高10°C可靠性就會降低一半。

經時擊穿-TDDB

TDDB 是電子器件中的一種失效機制,其中介電材料(例如 MOS 晶體管中的柵氧化層)由于長時間暴露于電場下而隨時間退化,導致泄漏電流增加。當電壓促使高能電子流動時,在氧化層內部形成導電路徑,同時產生陷阱和缺陷。當這些導電路徑在氧化層中造成短路時,介電層就會失效。失效時間 TF 隨著溫度的升高而呈指數級減少。

負 / 正偏置溫度不穩定性 - NBTI / PBTI

NBTI 影響以負柵極 - 源極電壓工作的 p 溝道 MOS 器件,而 PBTI 則影響處于積累區的 NMOS 晶體管。在柵極偏壓下,缺陷和陷阱會增加,導致閾值電壓升高,漏極電流和跨導減少。這種退化顯示出對數時間依賴性和指數溫度上升,在高于 125°C 時有部分恢復。

電遷移

電遷移是指導體中的金屬原子因電流流動而逐漸移位,形成空隙和小丘。因此,如果金屬線中形成的空隙大到足以切斷金屬線,就會導致開路;如果這些凸起延伸得足夠長以至于在受影響的金屬與相鄰的另一金屬之間形成橋接,則可能導致短路。電遷移會隨著電流密度和溫度的升高而加快,尤其是在空隙形成后,會導致電流擁擠和局部發熱。金屬線發生故障的概率與溫度成指數關系,與電流密度成平方關系,與導線長度成線性關系。銅互連器件可承受的電流密度約為鋁的五倍,同時可靠性相似。

熱載流子退化

當溝道電子在 MOS 晶體管漏極附近的高電場中加速,會發生熱載流子退化。在柵極氧化層中產生界面態、陷阱或空穴。它影響諸如閾值電壓 VT、電流增益 β、導通電阻 RDS_ON 和亞閾值泄漏等參數。在較高溫度下,平均自由程減少,降低了載流子獲得的能量,使得熱載流子退化在低溫條件下更為顯著。

安森美(onsemi)的Treo平臺提供了全面的產品開發生態系統,專為支持高溫運行而設計。這場即將到來的直播,將助您深入了解Treo平臺。

直播介紹 直播時間

2025/05/27 1030

直播主題

Road to BCD65,實現安森美ICD產品與Treo平臺的協同合作

直播簡介

作為業內領先的模擬和混合信號解決方案供應商,安森美基于BCD65納米工藝的Treo平臺專為新一代應用而設計,具備廣泛的電壓范圍、高集成度、卓越的溫度支持以及快速推向市場的能力。

本次研討會將深入探討安森美一系列高性能集成電路產品包括LDO穩壓器,放大器,總線開關等如何在Treo平臺上協同合作,共同推動智能電源管理和傳感技術的發展。并分享在汽車、工業和云計算領域廣泛的實際應用案例,幫助工程師們更好地理解如何利用Treo平臺的優勢,解鎖智能電源管理和傳感技術的新境界。

-

集成電路

+關注

關注

5417文章

11942瀏覽量

367036 -

半導體

+關注

關注

335文章

28569瀏覽量

232346 -

IC設計

+關注

關注

38文章

1346瀏覽量

105225 -

晶體管

+關注

關注

77文章

9977瀏覽量

140620

原文標題:高溫IC設計必懂基礎知識:高結溫帶來的5大挑戰

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高溫IC設計面臨的挑戰

高溫IC設計面臨的挑戰

評論