一。 Sobel簡介

一句話可以概況為,分別求水平與豎直梯度,然后求平方和再開方(近似的話就直接求絕對值之和),最后與設定的閾值進行比較,大于的話就賦值為0,小于的話就賦值為255

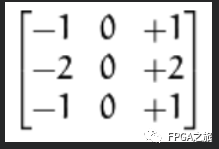

x方向梯度dx的求法:3*3的圖像矩陣與下面的矩陣在對應位置相乘然后相加

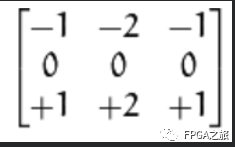

y方向梯度dy的求法:同上

二。 代碼實現

這里采用近似計算G = |dx| + |dy|,正負號分開計算,然后用大的數減去小的數

reg[10:0] Sobel_px ,Sobel_nx;reg[10:0] Sobel_py ,Sobel_ny;

wire[10:0] Sobel_x;wire[10:0] Sobel_y;

wire[7:0] Sobel_data;

//x方向的梯度assign Sobel_x = (Sobel_px 》 Sobel_nx) ? (Sobel_px - Sobel_nx) : (Sobel_nx - Sobel_px);//y方向的梯度assign Sobel_y = (Sobel_py 》 Sobel_ny) ? (Sobel_py - Sobel_ny) : (Sobel_ny - Sobel_py);assign Sobel_data = (Sobel_x + Sobel_y 》 ‘d135) ? ’d0 : ‘d255;

always@(posedge clk_9M or negedge rst)begin if(rst == 1’b0) begin Sobel_px 《= ‘d0; Sobel_nx 《= ’d0; end else if(cur_x 》= ‘d100 && cur_x 《= ’d199 && cur_y 》= ‘d50) begin Sobel_nx 《= data_line_11 + data_line_21 + data_line_21 + data_line_31; Sobel_px 《= data_line_13 + data_line_23 + data_line_23 + data_line_33; end else begin Sobel_nx 《= ’d0; Sobel_px 《= ‘d0; endend

always@(posedge clk_9M or negedge rst)begin if(rst == 1’b0) begin Sobel_py 《= ‘d0; Sobel_ny 《= ’d0; end else if(cur_x 》= ‘d100 && cur_x 《= ’d199 && cur_y 》= ‘d50) begin Sobel_py 《= data_line_11 + data_line_12 + data_line_12 + data_line_13; Sobel_ny 《= data_line_31 + data_line_32 + data_line_32+ data_line_33; end else begin Sobel_ny 《= ’d0; Sobel_py 《= ‘d0; endend

編輯:lyn

-

FPGA

+關注

關注

1643文章

21974瀏覽量

614387 -

sobel

+關注

關注

0文章

12瀏覽量

8022

原文標題:FPGA實現Sobel邊緣檢測

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

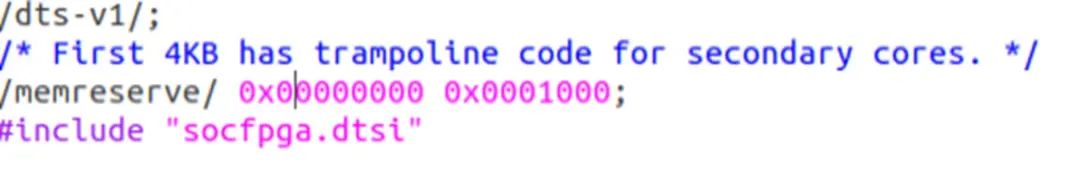

Linux系統中通過預留物理內存實現ARM與FPGA高效通信的方法

基于FPGA實現圖像直方圖設計

FPGA中浮點四則運算的實現過程

關于FPGA中Sobel的簡介與實現

關于FPGA中Sobel的簡介與實現

評論