文章來源:學習那些事

原文作者:前路漫漫

本文介紹了硅晶圓揀選測試需要進行直流特性測試、輸出驅動能力驗證、功能邏輯驗證。

概述

硅晶圓揀選測試作為半導體制造流程中的關鍵質量控制環節,旨在通過系統性電氣檢測篩選出功能異常的芯片。該測試體系主要包含直流特性分析、輸出驅動能力驗證和功能邏輯驗證三大核心模塊,各模塊依據器件物理特性與功能需求設計了差異化的檢測方法與技術路徑。

直流特性測試

直流測試聚焦于芯片基本電學連接性與靜態漏電特性的量化評估,其核心檢測項包括通路連續性、端口間短路 / 開路狀態判定以及泄漏電流閾值監測。在測試執行前,需通過探針卡校準程序完成物理連接性預驗證 —— 利用高精度阻抗測量設備,逐一對探針針尖與芯片壓點(Bond Pad)的接觸電阻進行掃描。對于 28 nm 及以上工藝,接觸阻抗需控制在 100 mΩ 以下;14 nm 及以下先進工藝因壓點尺寸縮小至 50 μm 以下,接觸阻抗要求提升至 10 mΩ 以內,以避免接觸不良導致的測試誤判。

在通斷性檢測環節,采用恒壓源 - 電流表(V-I)測試架構:對被測兩端口施加 1 V 直流偏壓,串聯 1mA 限流電阻形成測試回路。若回路電流大于 1 mA(等效電阻 <1 kΩ),判定為短路;若電流小于 1 μA(等效電阻> 1 MΩ),則判定為開路。針對深亞微米器件的柵極漏電流(IGSS)與襯底漏電流(ISUB),需使用皮安計在器件截止態下進行精準測量:以 28 nm CMOS 反相器為例,施加 VDD=1.8 V、輸入接地時,輸出端漏電流典型合格閾值為 < 10 nA;而 10 nm FinFET 器件因柵氧厚度減薄至 1.2 nm,漏電流控制標準嚴格至 < 100 pA,以滿足低功耗設計要求。

輸出驅動能力驗證

輸出檢查模塊通過模擬實際負載工況,對集成電路的邏輯電平驅動能力進行功能性驗證,不同邏輯族器件遵循差異化的測試標準:

TTL 電平器件:輸出低電平時(VOL 測試),灌入 8 mA 灌電流,要求 VOL≤0.4 V;輸出高電平時(VOH 測試),拉出 2 mA 拉電流,要求 VOH≥2.4 V。

CMOS 電平器件:VOH 典型值≥VDD-0.1 V,VOL 典型值≤GND+0.1 V,驅動能力由輸出級晶體管寬長比(W/L)決定 ——PMOS 管 W/L 影響灌電流能力,NMOS 管 W/L 決定拉電流能力。以 PCIe 5.0 接口芯片為例,為滿足 8 GT/s 數據速率與 50 Ω 負載驅動需求,其輸出級 NMOS 管寬長比通常設計為 1500:1 以上。

通過階梯式電流掃描(電流步長 1 mA)繪制輸出電壓 - 電流特性曲線,可評估器件在過載條件下的穩定性。當負載電流超過額定值 20% 時,需重點監測輸出電壓是否突破規格閾值,確保總線驅動芯片在復雜信號環境下的可靠性。

功能邏輯驗證

功能測試通過構建全場景邏輯激勵 - 響應模型,實現對電路功能完整性與時序正確性的深度驗證。對于含 N 個輸入端口的組合邏輯電路,理論窮舉測試需 2^N 個向量,實際借助 Synopsys TetraMAX 等 ATPG 工具,通過故障優先級排序與冗余向量剔除算法,可將向量集壓縮至 100-500 個,同時實現≥95% 的 Stuck-at 故障覆蓋率,并生成故障字典用于失效定位。

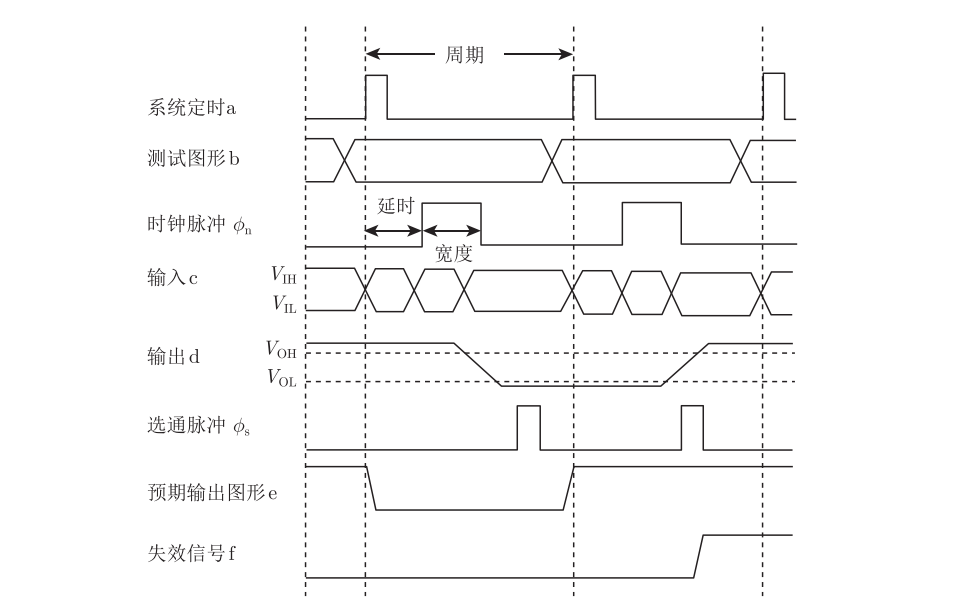

(1)數字電路動態測試

動態功能測試首先要有測試圖形,再經過時鐘脈沖信號φ控制而形成一定格式的輸入測試信號,這些信號通過管腳驅動器送到被測器件的輸入端。與此同時,被測器件的輸出信號受高、低電平(VOE、VoL)比較器的檢驗,判斷是否滿足產品規范的要求;然后受選通脈沖中的控制而與預期輸出圖形比較,判斷邏輯關系是否正確。最后,決定被測器件是否合格。

如果功能測試完全按照參數規范設置的定時信號(時鐘脈沖和選通脈沖)和電平基準,而且在最高極限頻率下進行,則被測器件通過動態測試時它的動態參數必然符合規范要求。

(2)存儲器可靠性測試

存儲器通常由地址譯碼器、存儲陣列、輸入緩沖器、輸出驅動器和讀出放大器等功能模塊構成。其常見故障可歸納為以下六類典型模式:

① 地址多選故障:單個地址信號觸發時,多個存儲單元被同時選中,通常由地址譯碼器晶體管短路或版圖布局缺陷導致;

② 地址失效故障:部分存儲單元無法通過任何地址訪問,多因地址線開路、譯碼器邏輯失效或存儲單元晶體管燒毀引發;

③ 內容固定故障:存儲單元數據寫入后無法更新,表現為無論輸入何種信號,讀出值始終為固定邏輯電平(“0” 或 “1”),根源可能是存儲電容永久性漏電或晶體管柵極氧化層擊穿;

④ 單元串擾故障:某存儲單元的數據翻轉通過寄生電容耦合至相鄰單元,導致非目標單元邏輯狀態異常,尤其在高密度存儲陣列中因單元間距縮小而更易發生;

⑤ 讀后恢復延遲故障:讀出放大器在連續讀取長串相同數據后,無法快速切換至相反邏輯的讀取狀態,通常與放大器動態失調或反饋回路響應速度不足相關;

⑥ 寫后恢復延遲故障:寫周期后立即執行讀操作時,取數時間顯著延長,在讀 / 寫共用數據線的架構中,因總線切換延遲和電荷再平衡過程,該現象更為明顯。

從故障特性可劃分為兩大類別:

硬故障:故障表現與環境溫度、電源電壓波動及輸入信號時序無關,具有永久性和確定性。例如存儲單元固定型故障、地址線短路等,可通過直流測試或基礎功能測試直接定位。

軟故障:僅在溫度極值、電源電壓臨界閾值或輸入時序邊界條件下顯現,常規工作條件下器件功能正常。典型場景包括高溫下的存儲單元漏電加劇、電壓跌落導致的邏輯翻轉閾值偏移等,需結合環境應力測試與動態功能測試進行暴露。

常用的測試圖形

常用測試圖形有以下三種:

1. N1型測試圖形

2. N2型測試圖形

3. N3/2型測試圖形

測試圖形技術體系

一.線性復雜度圖形(O (N)):量產初篩

全 “0”/ 全 “1” 圖形:順序寫入單一數據并讀取比對,快速檢測存儲單元固定型故障。該圖形對晶體管源漏短路、位線金屬橋接等硬故障的檢測覆蓋率達 80%,廣泛應用于嵌入式 SRAM 的內建自測試(BIST)與 NOR Flash 的塊初始化驗證。

測試序列長度:(2N)x2,全“0”和全“1”各一次,共(4N)次操作)。

棋盤格圖形:相鄰單元交替寫入 “0” 和 “1”,利用存儲單元電容(40-60 fF)與位線寄生電容(800 fF-1.2 pF)的分壓效應檢測串擾。當單元電容與位線電容比值 < 1:20 時,相鄰單元數據翻轉會導致目標單元電壓波動超過閾值電壓的 15%,觸發數據錯誤,該圖形可有效識別金屬層間距不足(<0.15 μm)引發的耦合噪聲。但地址故障檢測仍不充分。

測試序列長度:2Nx2, “0-1”和“1-0”交替模式各一次,共( 4N ) 次操作)。

齊步圖形(March C 算法):執行 “全寫 0→逐讀 0 寫 1→全讀 1 寫 0→反向操作” 流程,檢測地址譯碼器偏移故障(如地址 i 誤選 i+1 單元)。該圖形對譯碼器晶體管閾值電壓漂移(ΔVth>100 mV)導致的地址誤判具有 100% 檢測覆蓋率。

測試序列長度:(N+2N+2N)x2=(5N) x 2

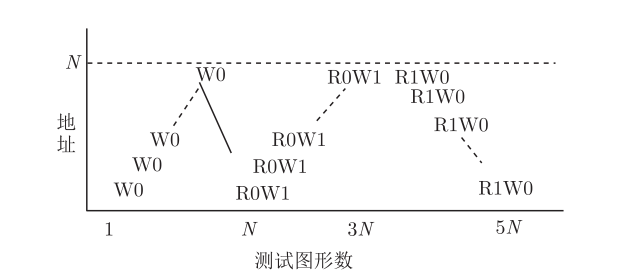

二、平方復雜度圖形(O (N2)):研發級深度檢測

這類測試圖形的長度與存儲單元數 N 的 2 次方成正比。這類圖形能同時檢測地址和數據兩方面的故障,主要用于檢測存儲單元之間的干擾。

走步圖形:全寫 “0” 后,逐次將基準單元寫 “1” 并掃描全陣列,檢測位線粘連故障 —— 若字線驅動晶體管因柵極氧化層厚度不均(偏差 > 15%)導致導通電阻異常,基準單元寫操作會通過寄生電容耦合至相鄰位線,引發整列數據異常。某 1Gb DDR3 存儲器實測中,該圖形定位到字線氧化層厚度從標準 20 nm 減薄至 17 nm 處的跨單元干擾,對應漏電流超標 3 倍。

圖形測試序列長度為:[N+ (1+ N + 1)N] x 2 = (N2+3N) x 2

跳步圖形:在走步圖形基礎上,對非基準單元執行三次讀取(Rj1→Rj2→Rj3),通過一致性驗證識別動態噪聲故障。測試設備需滿足時鐘抖動 < 1 ps、電壓噪聲 < 5 mV 的精度,以捕捉讀出放大器回踢噪聲(典型幅值 10 mV,持續時間 2 ns)對數據穩定性的影響,適用于 DDR4 存儲器的時序邊界測試(如 tAC=8 ns)。

圖形測試序列長度為:{N+[3(N - 1) + 2]N} x 2 = 3N2x2

跳步寫恢復圖形:固定基準單元為 “0”,逐一對其他單元寫 “1” 并實時讀取基準單元,驗證寫操作干擾。在汽車級 eMMC 測試中,結合 125 ℃高溫與 VDD=3.6 V(+20% 過壓)應力,該圖形可加速襯底耦合噪聲導致的基準單元翻轉,漏檢率控制在 0.01% 以下。

圖形測試序列長度:[N +6(N -l)N] x2= (6N2-5N) x2

三、N3/2復雜度圖形:大容量存儲器效率優化

隨著存儲器容量的不斷增大 , N2 型測試圖形的測試時間太長。為了減少測試時間,人們又開發了測試序列長度與存儲單元 N 的 3/2 次方成正比的 N3/2型測試圖形。

正交走步圖形:將 N=R×C 的存儲矩陣分解為行 / 列獨立掃描,利用存儲器頁模式(Page Mode)減少行激活次數。以 16 Gb DDR4(8Bank,<4096Row,1024Column)為例,測試序列長度從 O (N2)=16 GB2 降至 O (N√N)=16 GB×√16 GB=16GB×4096,操作次數減少 99.96%,測試時間從 1.2 秒縮短至 65 ms。

測試序列長度:{3N + [(2N1/2-1) +2]N} x 2 = (2N3 / 2+4N) x 2

對角線走步圖形:聚焦主對角線單元(i=j),該區域因高頻訪問易發生疲勞失效。在 8 層 HBM3 存儲器中,擴展至三維空間測試同地址跨層單元,考慮 TSV 寄生參數(電容 50 fF / 個,電阻 15 Ω/ 個),需在測試向量中加入 200 mV 的驅動電壓補償,以抵消層間耦合導致的信號衰減。

圖形測試序列長度為:[N+(N + 2)N1/2]x 2 = (N3/ 2+ N + 2N1/2) x 2

新興測試技術

三維分層測試技術(成熟度 TRL 8):針對 HBM3 等 3D 堆疊存儲器,開發基于 XYZ 三維地址映射的測試圖形,通過多通道探針卡(通道間距 100 μm,同步精度 ±3 ps)實現 8 層 Die 同步激勵。實測表明,該技術將層間串擾故障檢測效率提升 5 倍,已應用于 12 層堆疊的 HBM2e 器件測試,漏檢率從 0.5% 降至 0.05%。

機器學習優化圖形(TRL 7):利用歷史故障數據訓練神經網絡,動態生成針對特定工藝缺陷的測試向量。例如,針對 7 nm FinFET 工藝的隨機柵極隧穿效應,生成的測試圖形包含高頻翻轉(>1 GHz)與電壓邊沿掃描序列,相比傳統 ATPG 工具,故障檢測時間縮短 40%,覆蓋率提升 3%。

光子輔助測試(TRL 6):采用硅光探針(波長 1310 nm,調制速率 25 Gbps)傳輸并行測試向量,通過光電轉換模塊(損耗 < 2 dB)實現電信號加載。該技術已在 22nm 存儲控制器測試中驗證,相比傳統電子測試,其信號完整性提升 20%,但光探針校準精度(±5 μm)仍需進一步優化。

?

-

芯片

+關注

關注

459文章

52252瀏覽量

436834 -

半導體

+關注

關注

335文章

28666瀏覽量

233219 -

工藝

+關注

關注

4文章

675瀏覽量

29282 -

硅晶圓

+關注

關注

4文章

275瀏覽量

21204

原文標題:晶圓揀選測試類型

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶圓揀選測試類型

晶圓揀選測試類型

評論