????

本文主要介紹功率器件晶圓測(cè)試及封裝成品測(cè)試。??????

晶圓測(cè)試(CP)????

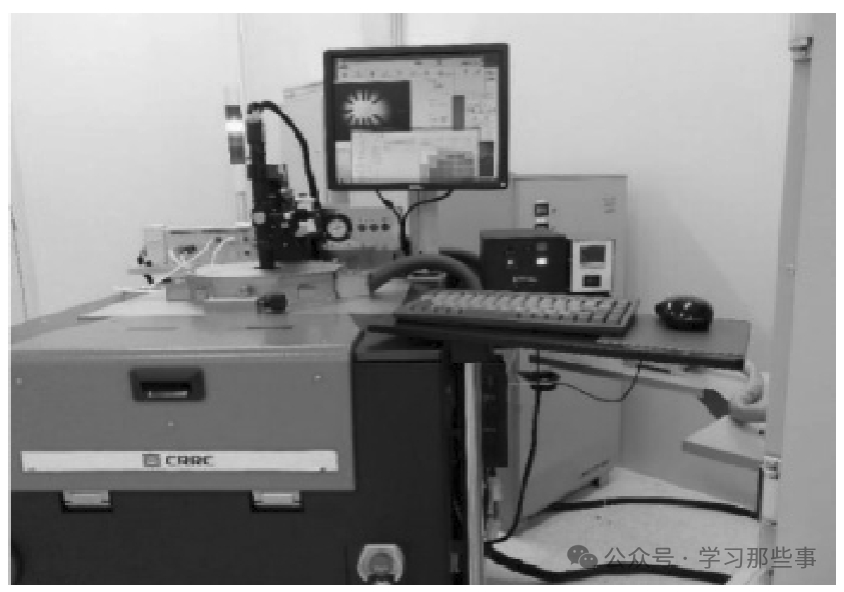

如圖所示為典型的碳化硅晶圓和分立器件電學(xué)測(cè)試的系統(tǒng),主要由三部分組成,左邊為電學(xué)檢測(cè)探針臺(tái)阿波羅AP-200,中間為晶體管檢測(cè)儀IWATSU CS-10105C,右邊為控制用計(jì)算機(jī)。三部分組成了一個(gè)測(cè)試系統(tǒng)。

下圖所示為探針臺(tái),主要對(duì)晶圓進(jìn)行電學(xué)檢測(cè),分為載物臺(tái)、探卡、絕緣氣體供應(yīng)設(shè)備這幾部分,載物臺(tái)用于晶圓的放置,可以兼容4~8寸的晶圓,上面有真空氣孔,將晶圓吸附住,防止在絕緣氣體和探針測(cè)試過程中晶圓發(fā)生移位。絕緣氣體主要是壓縮空氣和兩種,絕緣氣體用于防止在測(cè)高壓過程中發(fā)生“打火”現(xiàn)象(電擊穿空氣)。目前除用氣體做絕緣外,最常用的方法是將晶圓浸泡在氟油中,這種方法的測(cè)試效果要強(qiáng)于壓縮空氣的絕緣,并且氟油在測(cè)試完成后很容易揮發(fā),不會(huì)在晶圓表面造成污染殘留。

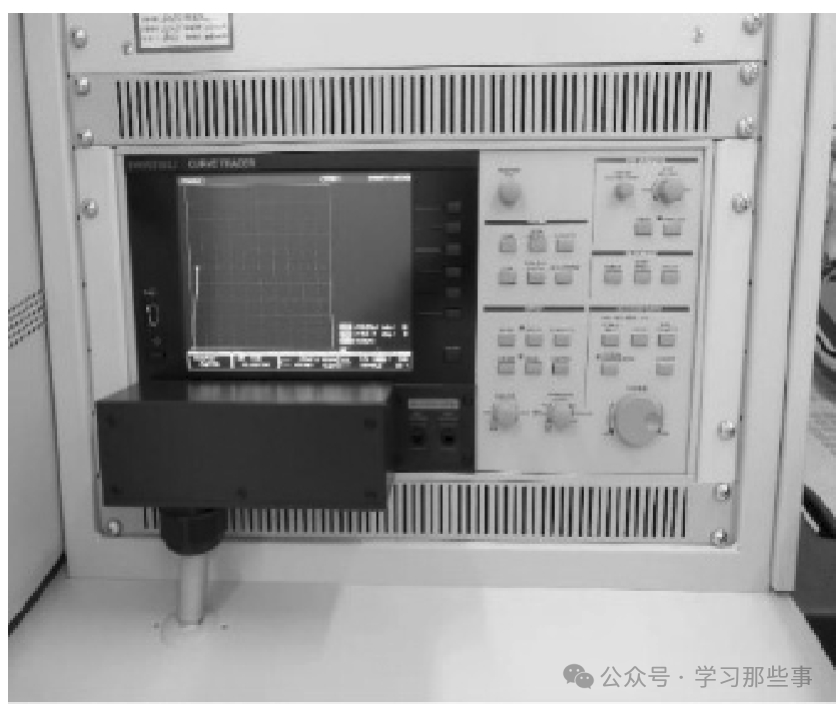

下圖所示為曲線追蹤儀的主界面,該設(shè)備主要用于產(chǎn)生并傳輸高電壓與大電流至探針,采用連線方式實(shí)現(xiàn)傳導(dǎo)。其內(nèi)部結(jié)構(gòu)集成了兩組電源組件:集電極電源與步進(jìn)信號(hào)發(fā)生器,能夠依據(jù)電路布局靈活地將電壓施加到集電極、發(fā)射極及基極,以適應(yīng)多樣化的測(cè)試需求。此外,該設(shè)備預(yù)裝了七種專用測(cè)試電路模塊,旨在覆蓋多種測(cè)試場景。

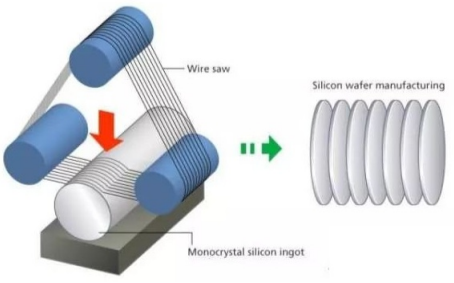

晶圓測(cè)試(Chip Probing,CP)是半導(dǎo)體生產(chǎn)流程中的一個(gè)關(guān)鍵環(huán)節(jié),它介于晶圓制造與封裝作業(yè)之間。當(dāng)晶圓制造完成后,表面密布著數(shù)以千計(jì)的未封裝芯片(DIE)。由于這些芯片尚未切割封裝,其微小的引腳直接暴露,因此需借助精密探針與測(cè)試設(shè)備建立連接。晶圓測(cè)試便是在整片未經(jīng)切割封裝的晶圓上,通過探針卡將這些外露的芯片引腳與測(cè)試系統(tǒng)相連,進(jìn)而實(shí)施全面檢測(cè)的過程。

完成Wafer制造流程后,會(huì)因工藝因素產(chǎn)生一定的制造瑕疵,導(dǎo)致晶圓上的裸DIE中存在一定比例的不良品。晶圓測(cè)試的核心目標(biāo)在于封裝流程前識(shí)別并剔除這些不良品(即進(jìn)行Wafer篩選),以提升最終芯片產(chǎn)品的合格率,并降低后續(xù)封裝與測(cè)試的成本負(fù)擔(dān)。此外,在芯片封裝過程中,部分引腳會(huì)被封裝于內(nèi)部,導(dǎo)致這些引腳所對(duì)應(yīng)的功能無法在封裝后進(jìn)行檢測(cè),只能在晶圓階段完成測(cè)試。部分企業(yè)還會(huì)依據(jù)晶圓測(cè)試的結(jié)果,按照性能差異將芯片劃分為不同等級(jí),以便針對(duì)不同市場投放相應(yīng)品質(zhì)的產(chǎn)品。

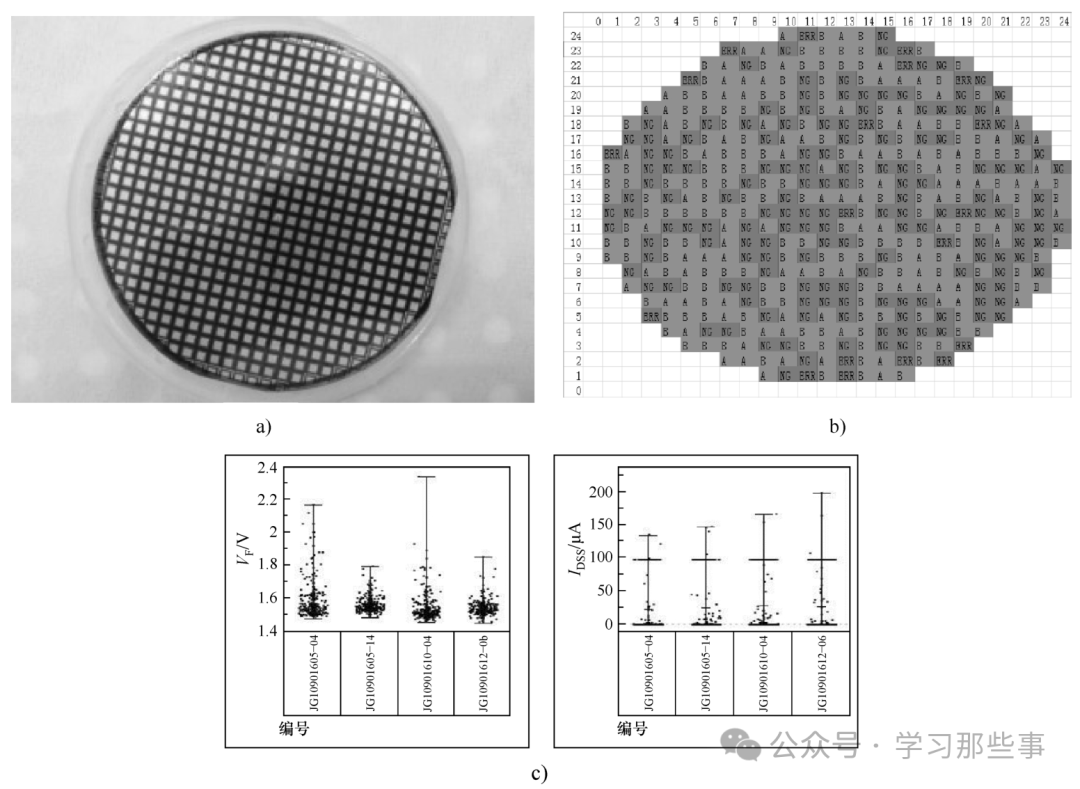

以SiC SBD為例,下圖為1200V 20A SiC SBD晶圓,晶圓正面為陽極,背面為陰極。探針臺(tái)內(nèi)的步進(jìn)式電機(jī)帶動(dòng)載物臺(tái)對(duì)晶圓進(jìn)行點(diǎn)測(cè)。通過對(duì)1200V 20A晶圓裸片的測(cè)試分析,步進(jìn)式掃描后會(huì)得到圖2所示的等級(jí)MAP圖,A、B、NG、ERR分別為相應(yīng)的等級(jí)分類。

對(duì)5塊晶圓的測(cè)試結(jié)果用JMP進(jìn)行匯總可得圖4-20c所示的結(jié)果,從中可以看出,基本都在1.5~1.6V,反向漏電流部分都在10μA以下。晶圓正向分布的一致性良好,但是反向特性有通過提高工藝而進(jìn)一步提升的空間。

封裝成品測(cè)試?

封裝成品測(cè)試(Finel Test,F(xiàn)T)是對(duì)封裝好的芯片進(jìn)行設(shè)備應(yīng)用方面的測(cè)試,把壞的芯片挑出來,F(xiàn)T通過后還會(huì)進(jìn)行工序質(zhì)量測(cè)試和產(chǎn)品質(zhì)量測(cè)試,F(xiàn)T是對(duì)封裝成品進(jìn)行測(cè)試,檢查封裝廠的工藝水平。FT的良率一般都不錯(cuò),但由于FT比CP測(cè)試包含更多的項(xiàng)目,也會(huì)遇到低產(chǎn)量問題,而且這種情況比較復(fù)雜,一般很難找到根本原因。

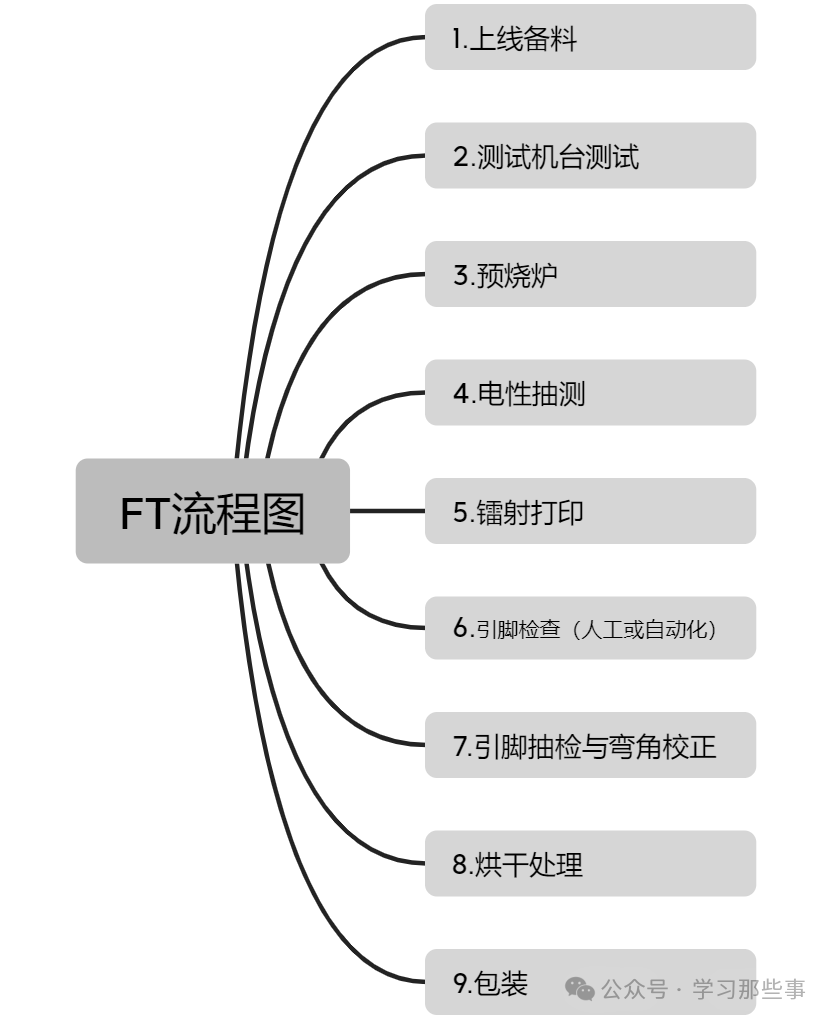

廣義上FT也被視作自動(dòng)測(cè)試設(shè)備(ATE)測(cè)試的一環(huán)。通常,ATE測(cè)試合格后,產(chǎn)品即可交付客戶。然而,針對(duì)高標(biāo)準(zhǔn)企業(yè)或產(chǎn)品,F(xiàn)T之后還需經(jīng)歷系統(tǒng)級(jí)測(cè)試(SLT),也稱試驗(yàn)臺(tái)驗(yàn)證。相較于ATE測(cè)試,SLT更為嚴(yán)苛,側(cè)重于功能層面的深度檢驗(yàn),確保各模塊運(yùn)作正常。鑒于SLT耗時(shí)較長,實(shí)際操作中多采用抽樣檢測(cè)策略。圖為FT的測(cè)試流程。

上線備料:此步驟旨在將即將進(jìn)行線上測(cè)試的待測(cè)產(chǎn)品整理至一個(gè)標(biāo)準(zhǔn)化容器中。這樣做是為了確保在將產(chǎn)品置于分類機(jī)時(shí)能夠準(zhǔn)確定位,進(jìn)而使測(cè)試機(jī)臺(tái)的自動(dòng)化機(jī)械結(jié)構(gòu)能夠順利實(shí)現(xiàn)自動(dòng)上下料操作。

測(cè)試機(jī)臺(tái)測(cè)試:待測(cè)產(chǎn)品經(jīng)過入庫驗(yàn)收及物料準(zhǔn)備后,便進(jìn)入機(jī)臺(tái)檢測(cè)階段。測(cè)試機(jī)臺(tái)的核心功能是向PECard發(fā)送必要的電信號(hào),并接收待測(cè)產(chǎn)品對(duì)這些電信號(hào)的反饋,最終依據(jù)這些反饋來判定產(chǎn)品的電性能測(cè)試結(jié)果。

預(yù)燒爐:在測(cè)試存儲(chǔ)器等高價(jià)值芯片時(shí),通常會(huì)增設(shè)一個(gè)高溫預(yù)處理環(huán)節(jié)。在完成前兩步測(cè)試后,待測(cè)產(chǎn)品會(huì)被送入高溫預(yù)處理爐中進(jìn)行加熱。這一步驟的目的是通過提供一個(gè)高溫、高電壓、大電流的環(huán)境,促使那些生命周期較短的潛在問題產(chǎn)品提前暴露問題,從而降低產(chǎn)品在客戶使用過程中的故障率。

電性抽測(cè):此環(huán)節(jié)旨在從已完成測(cè)試機(jī)臺(tái)檢測(cè)的樣本中抽取部分,重新置于測(cè)試機(jī)臺(tái)上驗(yàn)證其結(jié)果的一致性。若結(jié)果不符,可能歸因于測(cè)試機(jī)臺(tái)故障、測(cè)試程序缺陷、測(cè)試配件損壞或測(cè)試流程中的誤差。

激光打印:利用激光打印機(jī),依客戶的正印規(guī)格,將指定的正印打到芯片上面。?

引腳檢查(人工或自動(dòng)化):此步驟涉及檢查待測(cè)品的正印與引腳的對(duì)稱性、平整度及共面性等情況。這一工作既可通過激光掃描技術(shù)自動(dòng)化完成,也可依賴人工細(xì)致檢驗(yàn)。

引腳抽檢與彎角校正:針對(duì)存在彎角的引腳產(chǎn)品,先進(jìn)行修復(fù)處理,隨后通過人工方式對(duì)其引腳進(jìn)行抽檢。

烘干處理:完成所有測(cè)試與檢驗(yàn)后,產(chǎn)品需進(jìn)入烘烤箱中,以去除附著的水分,確保產(chǎn)品在送達(dá)客戶前不會(huì)因水分侵蝕而損害品質(zhì)。

包裝:按照客戶要求,將原本存放于標(biāo)準(zhǔn)容器中的待測(cè)品重新分類,并裝入客戶指定的包裝容器內(nèi),同時(shí)在包裝容器上貼上必要的商標(biāo)標(biāo)識(shí)。

-

晶圓

+關(guān)注

關(guān)注

52文章

5125瀏覽量

129185 -

封裝

+關(guān)注

關(guān)注

128文章

8526瀏覽量

144827 -

功率器件

+關(guān)注

關(guān)注

42文章

1914瀏覽量

92196

原文標(biāo)題:功率器件晶圓測(cè)試及封裝成品測(cè)試

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

MEMS傳感器晶圓級(jí)測(cè)試與成品級(jí)測(cè)試淺析

什么是晶圓測(cè)試?怎樣進(jìn)行晶圓測(cè)試?

什么是晶圓級(jí)封裝?

晶圓級(jí)芯片封裝有什么優(yōu)點(diǎn)?

晶圓封裝有哪些優(yōu)缺點(diǎn)?

如何測(cè)試從晶圓形狀從圓到不圓的變換

晶圓測(cè)試探針臺(tái)的組成以及晶圓測(cè)試的重要性和要求

晶圓探針測(cè)試工藝以及相關(guān)設(shè)備的簡單介紹

淺談晶圓探針測(cè)試的目的 晶圓探針測(cè)試主要設(shè)備

晶圓封裝測(cè)試什么意思?

封裝后推拉力測(cè)試儀保障成品質(zhì)量穩(wěn)定的關(guān)鍵

功率器件晶圓測(cè)試及封裝成品測(cè)試介紹

功率器件晶圓測(cè)試及封裝成品測(cè)試介紹

評(píng)論