在當(dāng)前的國際國內(nèi)形勢下,中國一直在加大對半導(dǎo)體芯片行業(yè)的支持力度,加強(qiáng)自主創(chuàng)新能力建設(shè),突破關(guān)鍵核心技術(shù)瓶頸,實(shí)現(xiàn)半導(dǎo)體芯片行業(yè)的自主可控和可持續(xù)發(fā)展。這不僅關(guān)乎中國科技和經(jīng)濟(jì)的未來,也將為全球科技產(chǎn)業(yè)的發(fā)展作出重要貢獻(xiàn)。 發(fā)展芯片產(chǎn)業(yè)的重要性在于從受制于人的困境中突圍,保障國家信息安全,促進(jìn)經(jīng)濟(jì)轉(zhuǎn)型和產(chǎn)業(yè)發(fā)展,提升國際競爭力,抓住全球產(chǎn)業(yè)轉(zhuǎn)移機(jī)遇,培養(yǎng)專業(yè)人才并推動(dòng)創(chuàng)新驅(qū)動(dòng)。當(dāng)前,中國面臨國外技術(shù)封鎖的嚴(yán)峻形勢,關(guān)鍵技術(shù)如高端芯片制造設(shè)備和先進(jìn)封裝技術(shù)被限制出口,導(dǎo)致國內(nèi)企業(yè)如華為在芯片供應(yīng)上遭遇斷供危機(jī)。這凸顯了自主研發(fā)芯片的緊迫性,因?yàn)樾酒鳛楝F(xiàn)代科技的核心,廣泛應(yīng)用于通信、金融、能源、軍事等關(guān)鍵領(lǐng)域,一旦依賴進(jìn)口,其潛在的安全漏洞和后門將嚴(yán)重威脅國家信息安全。

如今半導(dǎo)體芯片行業(yè)蓬勃發(fā)展的背景下,芯片封裝測試作為關(guān)鍵環(huán)節(jié),對產(chǎn)品的性能、可靠性和上市時(shí)間有著至關(guān)重要的影響。隨著芯片技術(shù)的不斷進(jìn)步,從裸片制造到最終產(chǎn)品封裝測試的整個(gè)流程都面臨著日益復(fù)雜的挑戰(zhàn)。Altium Designer 軟件以其優(yōu)越的功能和高度集成的設(shè)計(jì)環(huán)境,成為了半導(dǎo)體芯片封裝測試行業(yè)的理想選擇和得力助手,尤其在版本控制、裝配變量、極坐標(biāo)應(yīng)用和 Wire Bonding 等方面,為芯片封裝測試提供了精準(zhǔn)且高效的解決方案。助力企業(yè)提升封測效率、降低迭代風(fēng)險(xiǎn)并加速產(chǎn)品上市。

半導(dǎo)體芯片行業(yè)封裝測試環(huán)節(jié)的挑戰(zhàn)

復(fù)雜的封裝設(shè)計(jì)需求

芯片封裝測試不僅要實(shí)現(xiàn)芯片內(nèi)部電路與外部引腳的精準(zhǔn)電氣連接,還需滿足小型化、高性能、高可靠性的要求。例如,在先進(jìn)封裝技術(shù)如 BGA(球柵陣列封裝)、QFN(四方扁平無引腳封裝)等類型中,內(nèi)部電路布局和引線鍵合的設(shè)計(jì)需要兼顧信號完整性、散熱性能、高可焊性以及機(jī)械穩(wěn)定性。

多版本管理與協(xié)同難題

芯片研發(fā)制造過程中,涉及多個(gè)版本的迭代優(yōu)化。封裝測試設(shè)計(jì)需要與芯片設(shè)計(jì)緊密配合,確保不同版本的封裝設(shè)計(jì)與芯片的電氣特性和工藝要求相匹配。同時(shí),封裝測試團(tuán)隊(duì)內(nèi)部以及與芯片設(shè)計(jì)團(tuán)隊(duì)之間需要高效的協(xié)同設(shè)計(jì)機(jī)制,以避免因信息不對稱導(dǎo)致的實(shí)際錯(cuò)誤和返工。

高精度封裝測試工藝要求

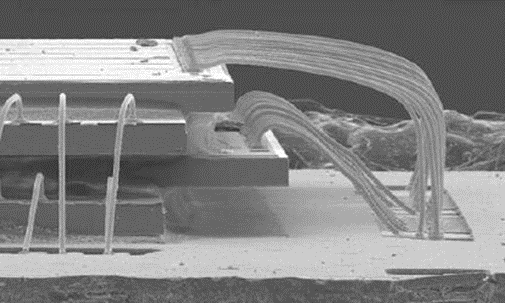

芯片封裝測試中的封測工藝極為復(fù)雜且精度要求高。不同的封裝形式需要精確設(shè)置封測參數(shù),如鍵合線的長度、弧高、拉力等。在 Wire Bonding 環(huán)節(jié),微小的參數(shù)偏差可能導(dǎo)致短路、斷路或接觸不良等質(zhì)量問題,影響芯片封裝的可靠性和性能,從而影響到整個(gè)芯片量產(chǎn)的上市周期。 在 3D IC 中,多個(gè)半導(dǎo)體芯片垂直堆疊,引線鍵合對于連接這些層至關(guān)重要。隨著設(shè)備變得越來越緊湊,對高密度處理能力的需求也日益增長,使得引線鍵合在管理細(xì)間距和高引腳數(shù)方面不可或缺。這項(xiàng)技術(shù)對于高性能計(jì)算、先進(jìn)的移動(dòng)設(shè)備和高密度數(shù)字電子產(chǎn)品至關(guān)重要。如下圖為 X-Ray 拍出來的圖像:采用引線鍵合的 3D 堆疊芯片。

Altium Designer 的關(guān)鍵功能

及其在芯片封裝測試中的應(yīng)用

版本控制

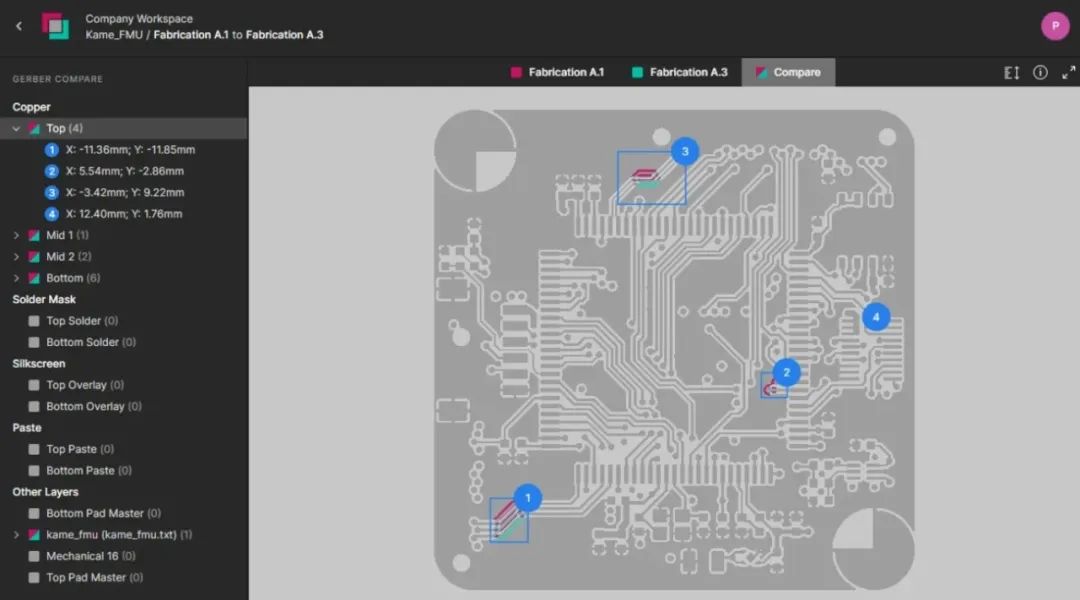

Altium Designer 的版本控制功能為芯片封裝測試環(huán)節(jié)提供了強(qiáng)大的管理工具。在芯片后期的板級測試過程中,以及芯片量產(chǎn)出品后的相關(guān)參考設(shè)計(jì)板的提供階段,每一次的修改都會被詳細(xì)記錄。包括修改時(shí)間、人員及具體內(nèi)容。例如,某芯片封裝測試項(xiàng)目在迭代優(yōu)化過程中,工程師通過版本控制功能,可以清晰追溯不同版本的封裝相對應(yīng)的設(shè)計(jì)文件,快速定位到特定版本進(jìn)行測試驗(yàn)證。當(dāng)發(fā)現(xiàn)新的封裝及設(shè)計(jì)文件存在問題時(shí),能夠方便地回溯到上一穩(wěn)定版本,分析問題根源并進(jìn)行針對性優(yōu)化。這不僅確保了設(shè)計(jì)文件的可追溯性和一致性,還極大地提高了多版本管理的效率,避免了因版本混亂導(dǎo)致的項(xiàng)目延誤。

裝配變量

在芯片封裝測試中,裝配變量功能發(fā)揮著至關(guān)重要的作用。它可以定義多種裝配方案和參數(shù)設(shè)置,以適應(yīng)不同封裝形式和測試要求。例如,在進(jìn)行不同尺寸的芯片封裝時(shí),通過設(shè)置裝配變量,可以快速調(diào)整鍵合線的材質(zhì)、直徑、弧高等參數(shù)。在實(shí)際測試中,工程師可以根據(jù)測試需求快速切換裝配變量,模擬不同的裝配場景,從而提前發(fā)現(xiàn)潛在的裝配問題。例如,某封裝測試企業(yè)在對一款新型芯片進(jìn)行 Wire Bonding 測試時(shí),利用裝配變量功能,快速調(diào)整鍵合線的拉力和弧高參數(shù),成功解決了鍵合不良的問題,提高了封裝測試的一次合格率。

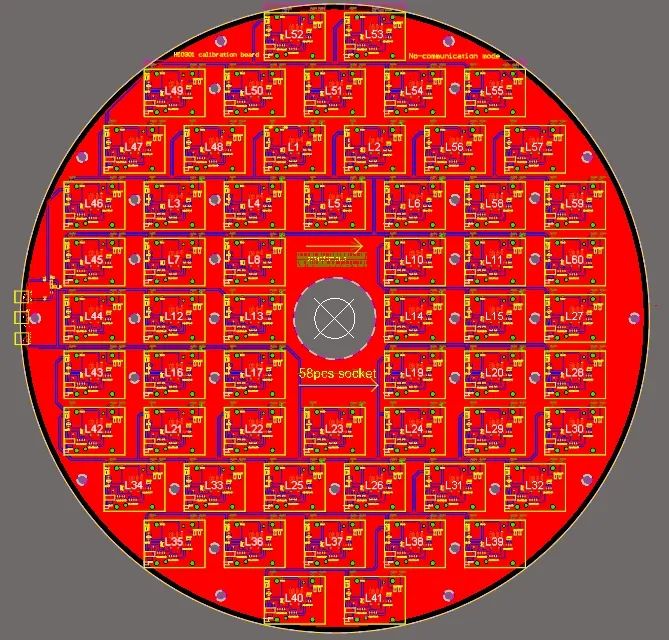

極坐標(biāo)應(yīng)用

極坐標(biāo)應(yīng)用在芯片測試環(huán)節(jié)具有獨(dú)特的優(yōu)勢。有些芯片測試板需要采用圓板布局布線,其電路布局和引線連接往往呈現(xiàn)出一定的對稱性和規(guī)律性。通過極坐標(biāo)系,可以更加直觀地進(jìn)行測試板的布局和布線設(shè)計(jì)。在圓板的布局布線過程中,利用極坐標(biāo)可以更精準(zhǔn)地定位元器件的相應(yīng)位置,確保布線的連接精度。例如,在設(shè)計(jì)一款圓形芯片測試板的方案時(shí),工程師可以使用極坐標(biāo)系,將待測芯片按照角度和半徑進(jìn)行整列式分布,從而實(shí)現(xiàn)高效、精準(zhǔn)的芯片后端測試工藝,并適當(dāng)配置相應(yīng)的參數(shù)。這不僅提高了半導(dǎo)體芯片的測試效率,還降低了因測試板中待測芯片定位不準(zhǔn)確導(dǎo)致的良率影響。

Wire Bonding

Altium Designer 對 Wire Bonding 工藝提供了全面的支持,是芯片封裝測試中不可或缺的工具。它可以幫助工程師進(jìn)行鍵合線的路徑規(guī)劃、長度優(yōu)化以及應(yīng)力分析等。通過精確的模擬和計(jì)算,確保鍵合線在芯片封裝過程中不會出現(xiàn)短路、斷路或接觸不良等問題。例如,某半導(dǎo)體企業(yè)使用 Altium Designer 進(jìn)行 Wire Bonding 設(shè)計(jì)時(shí),通過軟件的優(yōu)化算法,成功設(shè)計(jì)出鍵合線的適當(dāng)長度,線間間距,和綁線方式,提升了芯片的封裝工藝和封裝良率。在實(shí)際封裝測試中,工程師可以根據(jù)軟件的分析結(jié)果,調(diào)整鍵合工藝參數(shù),如鍵合頭的壓強(qiáng)、鍵合時(shí)間等,進(jìn)一步提高鍵合質(zhì)量。這不僅提升了芯片封裝的可靠性,還降低了生產(chǎn)成本。

此外,在半導(dǎo)體芯片封裝領(lǐng)域,裸片COB(Chip on Board)封裝憑借其成本低、散熱好等優(yōu)勢,也被眾多中小企業(yè)廣泛應(yīng)用。Altium Designer 的 Wire Bonding 功能在裸片 COB 封裝中,更是發(fā)揮了重要作用。在裸片COB封裝中,工程師可以利用該功能根據(jù)裸片的尺寸、引腳間距以及基板的布局,優(yōu)化鍵合線的路徑和形狀,確保鍵合線的連接既穩(wěn)定又可靠,避免因鍵合線過長或過短導(dǎo)致的信號傳輸延遲或接觸不良等問題。它能幫助工程師自動(dòng)識別和避開潛在的鍵合區(qū)域障礙物,可以靈活配置,在半導(dǎo)體芯片與其封裝之間,或多芯片模塊內(nèi)的不同芯片之間建立安全、低電阻的電連接。防止引線之間的短路或接觸不良,從而提高鍵合工藝的良品率。如下圖為 Altium Designer 的 Wire Bonding 功能在板上芯片 (COB) 技術(shù)的應(yīng)用。

應(yīng)用案例

案例一:先進(jìn)封裝設(shè)計(jì)優(yōu)化

一家知名半導(dǎo)體芯片封裝測試企業(yè)承接了一款高性能芯片的封裝項(xiàng)目。該芯片采用先進(jìn)的 BGA 封裝技術(shù),內(nèi)部電路復(fù)雜,封裝密度高。在項(xiàng)目初期,封裝測試團(tuán)隊(duì)面臨諸多設(shè)計(jì)難題,如鍵合線布局不合理導(dǎo)致信號干擾嚴(yán)重,封裝散熱性能不佳等。通過引入 Altium Designer 的版本控制、裝配變量、極坐標(biāo)應(yīng)用和 Wire Bonding 功能,工程師們對不同版本的封裝設(shè)計(jì)進(jìn)行了深入分析和比對。快速調(diào)整鍵合線的材質(zhì)、弧高等參數(shù),優(yōu)化鍵合線布局;結(jié)合極坐標(biāo)應(yīng)用,精準(zhǔn)定位鍵合點(diǎn)位置,提高鍵合效率和精度。最終,成功解決了信號干擾和散熱問題,芯片封裝測試合格率大幅提高,產(chǎn)品性能顯著提升,提前完成了項(xiàng)目交付。

案例二:芯片設(shè)計(jì)迭代與封裝測試協(xié)同

在一款芯片的迭代研發(fā)過程中,芯片設(shè)計(jì)團(tuán)隊(duì)和封裝測試團(tuán)隊(duì)緊密合作。芯片設(shè)計(jì)團(tuán)隊(duì)頻繁對芯片內(nèi)部電路進(jìn)行優(yōu)化調(diào)整,導(dǎo)致封裝測試設(shè)計(jì)需要不斷適應(yīng)新的電氣特性和引腳布局。通過 Altium Designer 的版本控制功能,封裝測試團(tuán)隊(duì)能夠及時(shí)追溯以往的版本并及時(shí)更新,確保封裝測試設(shè)計(jì)與芯片設(shè)計(jì)的一致性。在 Wire Bonding 環(huán)節(jié),依靠軟件分析,快速調(diào)整裝配參數(shù),適應(yīng)芯片引腳的變化。同時(shí),通過極坐標(biāo)應(yīng)用進(jìn)行鍵合點(diǎn)的重新定位和優(yōu)化。最終,芯片的迭代研發(fā)周期縮短了 25%,封裝測試的一次合格率提高了 30%,產(chǎn)品性能和可靠性得到了顯著提升。

案例三:板載芯片 (COB) 的應(yīng)用

LED:COB 技術(shù)廣泛應(yīng)用于 LED 設(shè)計(jì),可提供更高的流明密度和更佳的熱管理。引線鍵合技術(shù)可實(shí)現(xiàn)緊湊的 LED 陣列,并具有高效的散熱性能,從而為汽車、工業(yè)和消費(fèi)電子應(yīng)用提供更明亮、更持久的照明解決方案。如下圖所示為 COB LED 陣列。

光電子器件和圖像傳感器:隨著圖像傳感器分辨率的提高,所需的連接數(shù)量也急劇增加,細(xì)線鍵合技術(shù)變得至關(guān)重要。這些高性能、高密度的設(shè)計(jì)對于先進(jìn)的消費(fèi)電子產(chǎn)品、醫(yī)療診斷和安全系統(tǒng)大有裨益。如下圖所示為采用引線鍵合的 CMOS 圖像傳感器 COB。

Altium Designer 助力半導(dǎo)體

芯片封裝測試行業(yè)創(chuàng)新發(fā)展

提升效率

Altium Designer 的高效設(shè)計(jì)工具能夠顯著縮短半導(dǎo)體芯片封裝測試的研發(fā)周期。其版本控制功能方便團(tuán)隊(duì)成員快速定位所需版本,裝配變量功能可以快速調(diào)整芯片測試裝配方案,極坐標(biāo)應(yīng)用和 Wire Bonding 功能則為封裝和測試提供了精準(zhǔn)的解決方案。這些功能的有機(jī)結(jié)合,使得芯片封裝測試設(shè)計(jì)和工藝優(yōu)化過程更加高效、流暢,大大縮短了芯片上市周期。

確保質(zhì)量

通過精確的模擬和分析,Altium Designer 可以幫助工程師在設(shè)計(jì)階段就發(fā)現(xiàn)潛在的問題并進(jìn)行優(yōu)化。例如,在 Wire Bonding 過程中,可以提前預(yù)測鍵合線可能出現(xiàn)的應(yīng)力集中、弧高不足等問題,從而采取相應(yīng)的措施加以解決。這不僅提高了芯片封裝測試的質(zhì)量,還降低了因設(shè)計(jì)缺陷導(dǎo)致的生產(chǎn)成本和產(chǎn)品召回風(fēng)險(xiǎn)。

適應(yīng)行業(yè)發(fā)展趨勢

隨著半導(dǎo)體芯片行業(yè)向更高性能、更小尺寸、更低功耗方向發(fā)展,Altium Designer 也在不斷更新和優(yōu)化其功能。例如,支持更復(fù)雜的芯片封裝的相關(guān)設(shè)計(jì)、更精細(xì)的為半導(dǎo)體芯片應(yīng)用提供相應(yīng)的高速高密度布局布線、以及更高效的進(jìn)行板級信號完整性分析等。它能夠很好地適應(yīng)行業(yè)的發(fā)展趨勢,為芯片封裝測試以及各芯片類型的實(shí)際應(yīng)用提供持續(xù)的技術(shù)支持和創(chuàng)新動(dòng)力。

結(jié)語

Altium Designer 憑借其強(qiáng)大的版本控制、裝配變量、極坐標(biāo)應(yīng)用和 Wire Bonding 等功能,在半導(dǎo)體芯片封裝測試行業(yè)展現(xiàn)出了巨大的應(yīng)用價(jià)值。它不僅能夠應(yīng)對當(dāng)前芯片封裝測試的復(fù)雜性挑戰(zhàn),還能助力工程師們進(jìn)行創(chuàng)新設(shè)計(jì),推動(dòng)半導(dǎo)體芯片封裝測試技術(shù)以及芯片實(shí)際應(yīng)用的發(fā)展。為我國半導(dǎo)體芯片產(chǎn)業(yè)的自主可控和創(chuàng)新發(fā)展提供了強(qiáng)力支持。

關(guān)于Altium

Altium有限公司隸屬于瑞薩集團(tuán),總部位于美國加利福尼亞州圣迭戈,是一家致力于加速電子創(chuàng)新的全球軟件公司。Altium提供數(shù)字解決方案,以最大限度提高電子設(shè)計(jì)的生產(chǎn)力,連接整個(gè)設(shè)計(jì)過程中的所有利益相關(guān)者,提供對元器件資源和信息的無縫訪問,并管理整個(gè)電子產(chǎn)品生命周期。Altium生態(tài)系統(tǒng)加速了各行業(yè)及各規(guī)模企業(yè)的電子產(chǎn)品實(shí)現(xiàn)進(jìn)程。

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28625瀏覽量

232852 -

altium

+關(guān)注

關(guān)注

47文章

971瀏覽量

119641 -

封裝測試

+關(guān)注

關(guān)注

9文章

153瀏覽量

24218

原文標(biāo)題:【行業(yè)解決方案】Altium 助力半導(dǎo)體芯片行業(yè)創(chuàng)新發(fā)展

文章出處:【微信號:AltiumChina,微信公眾號:Altium】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Altium Designer的關(guān)鍵功能及其在芯片封裝測試中的應(yīng)用

Altium Designer的關(guān)鍵功能及其在芯片封裝測試中的應(yīng)用

評論