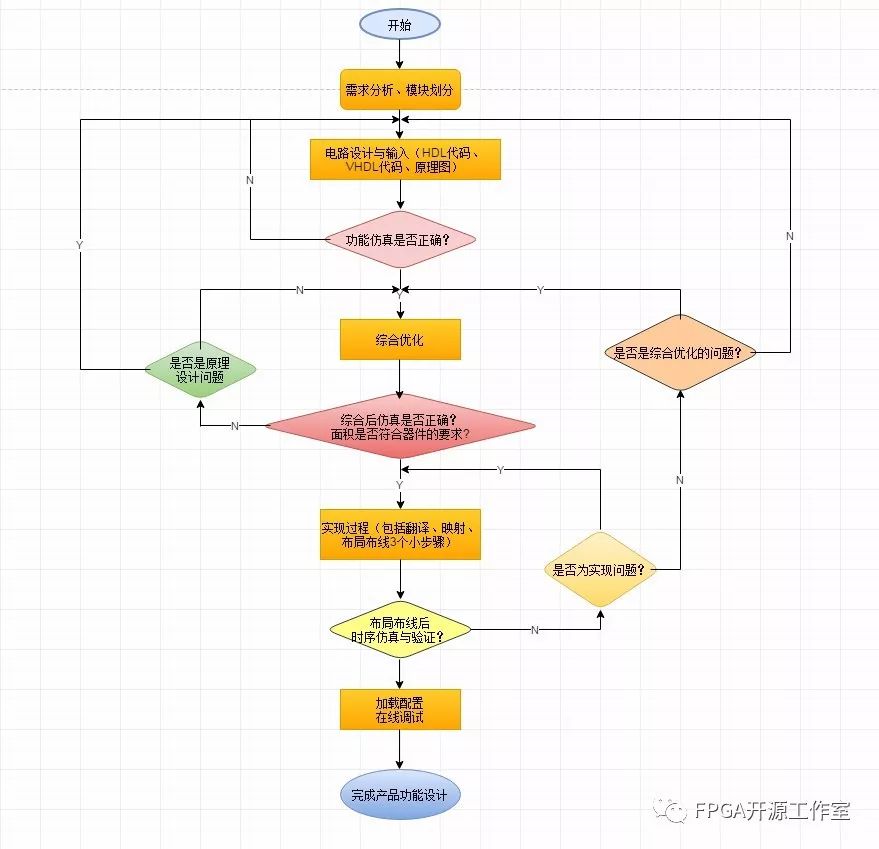

1.XILINXISE傳統(tǒng)FPGA設(shè)計流程

利用Xilinx ISE軟件開發(fā)FPGA的基本流程包括代碼輸入、功能仿真、綜合、綜合后仿真、實現(xiàn)、布線后仿真與驗證和下班調(diào)試等步驟。如下圖所示。

1)電路設(shè)計或代碼輸入

FPGA的設(shè)計可以直接畫原理圖,但是這種方法在比較復(fù)雜的系統(tǒng)的情況下,原理圖相當(dāng)復(fù)雜,所以慢慢被淘汰,ISE保留這一功能。

現(xiàn)在FPGA的設(shè)計輸入主要是Verilog和VHDL硬件語言。Verilog語言語法簡單,在亞洲區(qū)域使用比較廣泛;

VHDL被IEEE和美國國防部確認(rèn)為標(biāo)準(zhǔn)硬件描述語言,在歐洲區(qū)域比較常見。

2)功能仿真

在基本的FPGA模塊編寫完成后,要使用仿真工具對設(shè)計的模塊進(jìn)行仿真,驗證模塊的基本功能是否符合設(shè)計。功能仿真也被稱為前仿真。常用的仿真工具有

Model Tech公司的Modelsim, Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL。功能仿真可以加快FPGA的設(shè)計,減少設(shè)計過程中的錯誤。

3)綜合

綜合優(yōu)化(Synthesize)是將硬件語言或原理圖等設(shè)計輸入翻譯成由與,或,非門、RAM、觸發(fā)器等基本邏輯單元組成的邏輯連接(網(wǎng)表),并根據(jù)約束條件優(yōu)化生成的邏輯連接,輸出edf和edn等文件。

4)實現(xiàn)

實現(xiàn)可理解為利用實現(xiàn)工具把邏輯映射到目標(biāo)器件結(jié)構(gòu)的資源中,決定邏輯的最佳布局,選擇邏輯與輸入輸出功能連接的布線通道進(jìn)行連線,并產(chǎn)生相應(yīng)文件(如配置文件與相關(guān)報告)。通常可分為如下五個步驟。(1)轉(zhuǎn)換:將多個設(shè)計文件進(jìn)行轉(zhuǎn)換并合并到一個設(shè)計庫文件中。(2)映射:將網(wǎng)表中邏輯門映射成物理元素,即把邏輯設(shè)計分割到構(gòu)成可編程邏輯陣列內(nèi)的可配置邏輯塊與輸入輸出塊及其它資源中的過程。(3)布局與布線:布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內(nèi)部的物理位置,通常基于某種先進(jìn)的算法,如最小分割、模擬退火和一般的受力方向張弛等來完成;布線是指利用自動布線軟件使用布線資源選擇路徑試著完成所有的邏輯連接。因最新的設(shè)計實現(xiàn)工具是時序驅(qū)動的,即在器件的布局布線期間對整個信號通道執(zhí)行時序分析,因此可以使用約束條件操作布線軟件,完成設(shè)計規(guī)定的性能要求。在布局布線過程中,可同時提取時序信息形成報靠。(4)時序提取:產(chǎn)生一反標(biāo)文件,供給后續(xù)的時序仿真使用。(5)配置:產(chǎn)生FPGA配置時的需要的位流文件。在實現(xiàn)過程中可以進(jìn)行選項設(shè)置。因其支持增量設(shè)計,可以使其重復(fù)多次布線,且每次布線利用上一次布線信息以使布線更優(yōu)或達(dá)到設(shè)計目標(biāo)。在實現(xiàn)過程中應(yīng)設(shè)置默認(rèn)配置的下載形式,以使后續(xù)位流下載正常。

5)時序分析在設(shè)計實現(xiàn)過程中,在映射后需要對一個設(shè)計的實際功能塊的延時和估計的布線延時進(jìn)行時序分析;而在布局布線后,也要對實際布局布線的功能塊延時和實際布線延時進(jìn)行靜態(tài)時序分析。從某種程序來講,靜態(tài)時序分析可以說是整個FPGA設(shè)計中最重要的步驟,它允許設(shè)計者詳盡地分析所有關(guān)鍵路徑并得出一個有次序的報告,而且報告中含有其它調(diào)試信息,比如每個網(wǎng)絡(luò)節(jié)點的扇出或容性負(fù)載等。靜態(tài)時序分析器可以用來檢查設(shè)計的邏輯和時序,以便計算各通中性能,識別可靠的蹤跡,檢測建立和保持時間的配合,時序分析器不要求用戶產(chǎn)生輸入激勵或測試矢量。雖然Xilinx與Altera在FPGA開發(fā)套件上擁有時序分析工具,但在擁有第三方專門時序分析工具的情況下,僅利用FPGA廠家設(shè)計工具進(jìn)行布局布線,而使用第三方的專門時序分析工具進(jìn)行時序分析,一般FPGA廠商在其設(shè)計環(huán)境下皆有與第三方時序分析工具的接口。Synopsys公司的PrimeTime是一個很好的時序分析工具,利用它可以達(dá)到更好的效果。將綜合后的網(wǎng)表文件保存為db格式,可在PrimeTime環(huán)境下打開。利用此軟件查看關(guān)鍵路徑或設(shè)計者感興趣的通路的時序,并對其進(jìn)行分析,再次對原來的設(shè)計進(jìn)行時序結(jié)束,可以提高工作主頻或減少關(guān)鍵路徑的躚時。與綜合過程相似,靜態(tài)時序分析也是一個重復(fù)的過程,它與布局布線步驟緊密相連,這個操作通常要進(jìn)行多次直到時序約束得到很好的滿足。

在綜合與時序仿真過程中交互使用PrimeTime進(jìn)行時序分析,滿足設(shè)計要求后即可進(jìn)行FPGA芯片投片前的最終物理驗證。

6)調(diào)試與加載配置

設(shè)計開發(fā)的最后步驟就是在線調(diào)試或者將生成的配置文件寫入芯片中進(jìn)行測試。在ISE中使用iMPACT。

2.XILINXVIVADO傳統(tǒng)FPGA設(shè)計流程

Xilinx針對7系列FPGA、Zynq-7000 SOC FPGA和UltraScale芯片,為提升設(shè)計、集成和實現(xiàn)的效率,推出了全新的開發(fā)工具Vivado。

使用Vivado設(shè)計FPGA的基本流程如下圖

在設(shè)計輸入階段,除傳統(tǒng)的HDL代碼,Vivado還可以接受Vivado HLS生成的HDL代碼、System Generator模型輸出文件、IP Integrator模型以及IP。

在Vivado下,約束(時序約束和物理約束)采用XDC(xilinx Design Constraints)。

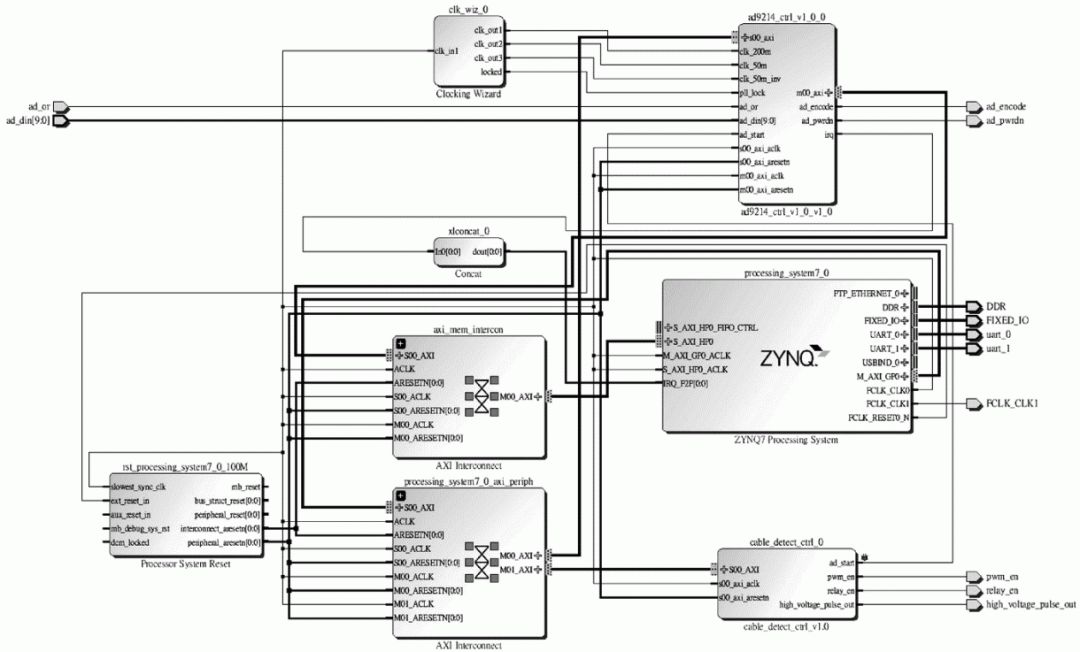

3.SOCFPGA設(shè)計流程

針對SOC FPGA的開發(fā),xilinx在Vivado中專門設(shè)置了一個工具IP Integrator。

IP Integrator作為IP集成工具,以圖形化、模塊化的方式在設(shè)計中添加IP、連接端口。

Zynq芯片由兩部分組成,分別是PS和PL兩部分,相應(yīng)地需要硬件編程和軟件編程。硬件編程使用Vivado,軟件編程使用SDK,具體流程見下圖。

借助Matlab完成Zynq開發(fā),如下圖。在Matlab下即可完成算法建模到C代碼和RTL代碼的生成。

責(zé)任編輯:lq

-

FPGA

+關(guān)注

關(guān)注

1643文章

21964瀏覽量

614110 -

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132126 -

Verilog

+關(guān)注

關(guān)注

28文章

1366瀏覽量

111821

原文標(biāo)題:從賽靈思FPGA設(shè)計流程看懂FPGA設(shè)計

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應(yīng)SoC設(shè)計

Vivado HLS設(shè)計流程

FPGA設(shè)計調(diào)試流程

【國產(chǎn)FPGA入學(xué)必備】國產(chǎn)FPGA權(quán)威設(shè)計指南+配套FPGA圖像視頻教程

DeepSeek在FPGA/IC領(lǐng)域的創(chuàng)新應(yīng)用及未來展望

FPC設(shè)計與制造流程 FPC與傳統(tǒng)PCB的區(qū)別

FPGA 實時信號處理應(yīng)用 FPGA在圖像處理中的優(yōu)勢

FPGA基礎(chǔ)知識及設(shè)計和執(zhí)行FPGA應(yīng)用所需的工具

XILINXISE傳統(tǒng)FPGA設(shè)計流程

XILINXISE傳統(tǒng)FPGA設(shè)計流程

評論