隨著人工智能技術的飛速發展,以DeepSeek為代表的大語言模型(LLM)正在逐步滲透到傳統硬件開發領域。在FPGA(現場可編程門陣列)和IC(集成電路)開發這一技術密集型行業中,DeepSeek憑借其強大的自然語言處理、代碼生成和邏輯推理能力,展現出顛覆傳統開發流程的潛力。本文將深入探討DeepSeek在這一領域的應用場景、技術優勢及未來發展方向。(以上由DeepSeek生成,這語言邏輯還是很強)

目前FPGA/IC開發的核心痛點

1、復雜的設計流程:從RTL設計到物理實現的數十個環節,涉及Verilog/VHDL編碼、驗證、綜合優化等專業操作。

2、知識門檻高:開發者需同時掌握硬件架構、時序分析、低功耗設計等跨學科知識。

3、驗證成本占比大:芯片開發中70%以上的時間用于功能驗證和調試。

4、工具鏈依賴性強:高度依賴Cadence/Synopsys等EDA工具,二次開發靈活性不足。

DeepSeek的技術突破與應用場景

1. 智能輔助設計

RTL代碼生成

基于自然語言描述自動生成優化代碼:

讓DeepSeek:生成一個16位循環移位寄存器,帶使能端

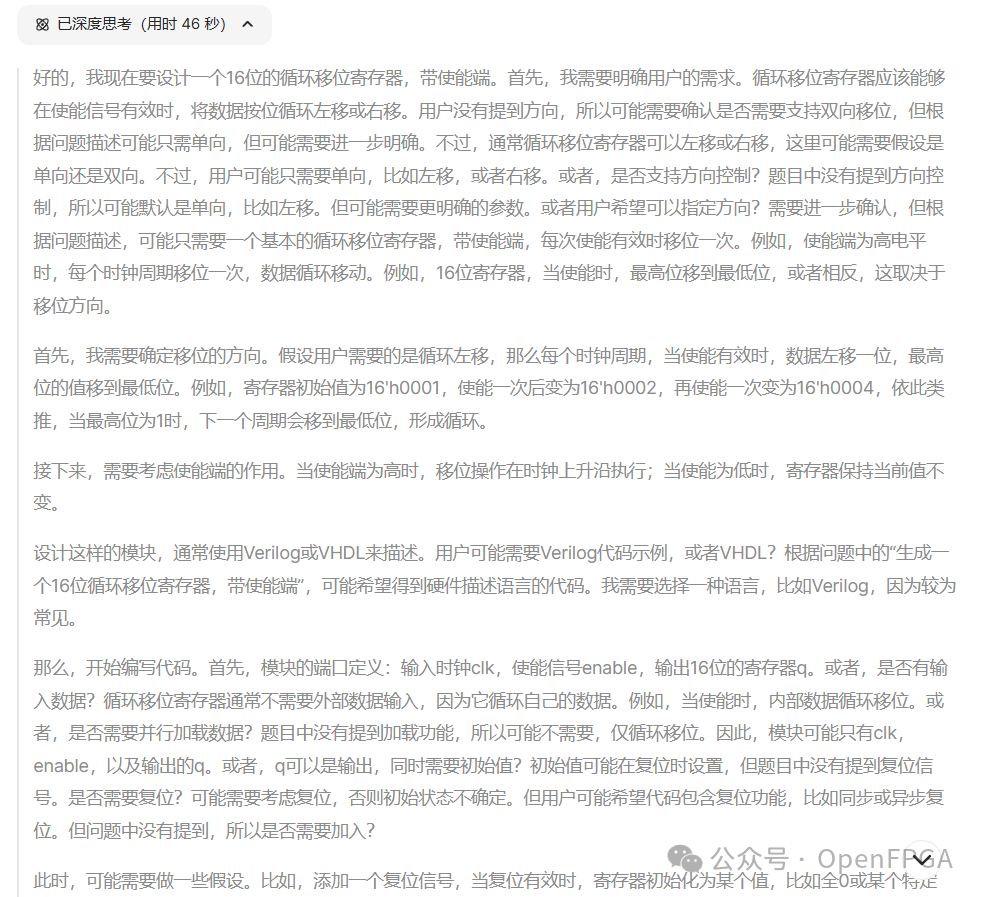

首先會進行思考,將相關思路描述出來:

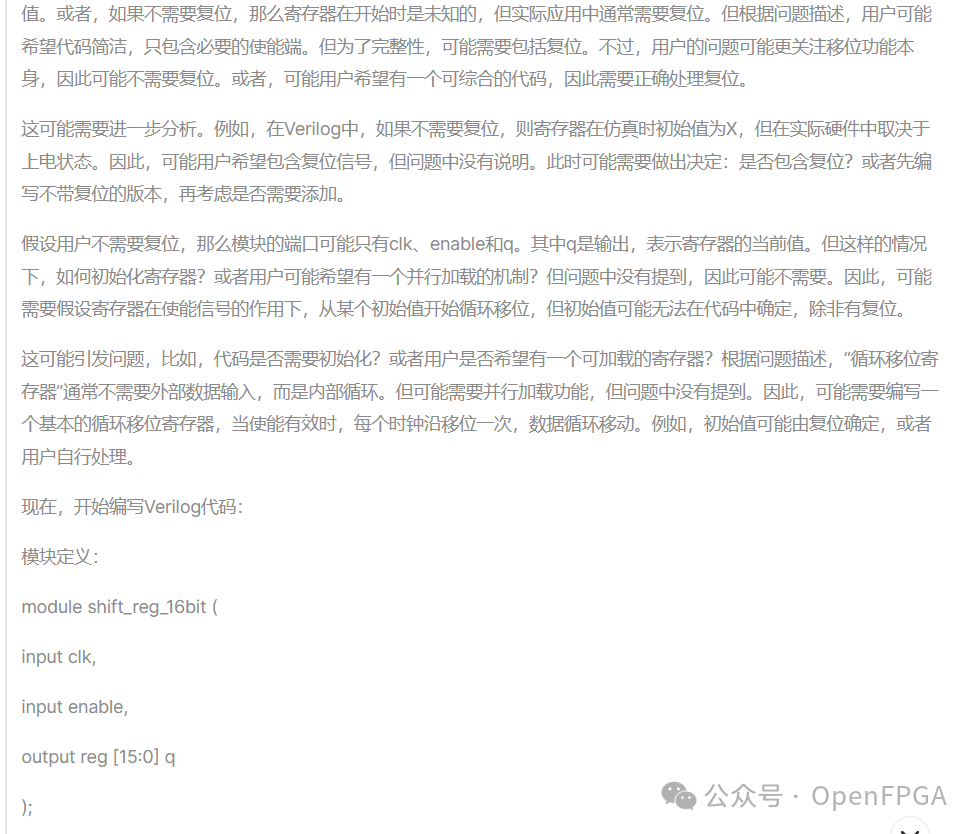

然后給出代碼和思路:

moduleshift_reg_16bit( inputclk,//時鐘信號 inputenable,//使能信號(高電平有效) outputreg[15:0]q//16位寄存器輸出 ); //循環左移邏輯 always@(posedgeclk)begin if(enable)begin //將最高位移動到最低位,其余位左移 q<=?{q[14:0],?q[15]}; ????end ????//?enable為低時自動保持當前值 end endmodule

上面的代碼還很粗糙,我們需要進行更精細的“打磨”。

這個代碼基本10S就可以生成,前提是給DeepSeek輸入的描述要盡可能的詳細。此類基礎模塊的開發效率可提升3-5倍。

約束文件優化

通過分析設計意圖自動生成SDC時序約束,減少時序違例風險:

#定義時鐘周期(假設時鐘頻率為100MHz,周期為10ns) create_clock-nameclk-period10[get_portsclk] #定義時鐘不確定性(jitter) set_clock_uncertainty0.2[get_clocksclk]

2. 驗證流程革新

智能Testbench生成

根據設計規范自動生成UVM驗證框架,覆蓋率達到行業標準的95%以上(DeepSeek自己說的):

classmy_testextendsuvm_test;

virtualtaskrun_phase(uvm_phasephase);

repeat(100)begin

`uvm_do_with(req,{datainside{[0:255]};})

end

endtask

endclass

故障原因分析

結合波形數據和錯誤日志,快速定位時序違例源頭:

檢測到setup違例在路徑regA -> regB

建議方案:

插入兩級流水寄存器

優化組合邏輯層級(當前為7級)

物理設計優化

布局預測模型

基于歷史設計數據訓練布局熱點預測網絡,提前規避布線擁塞。

功耗優化建議

分析網表結構提出低功耗方案:

檢測到時鐘域crossing未同步 推薦方案:添加clock gating單元 預計動態功耗降低18%

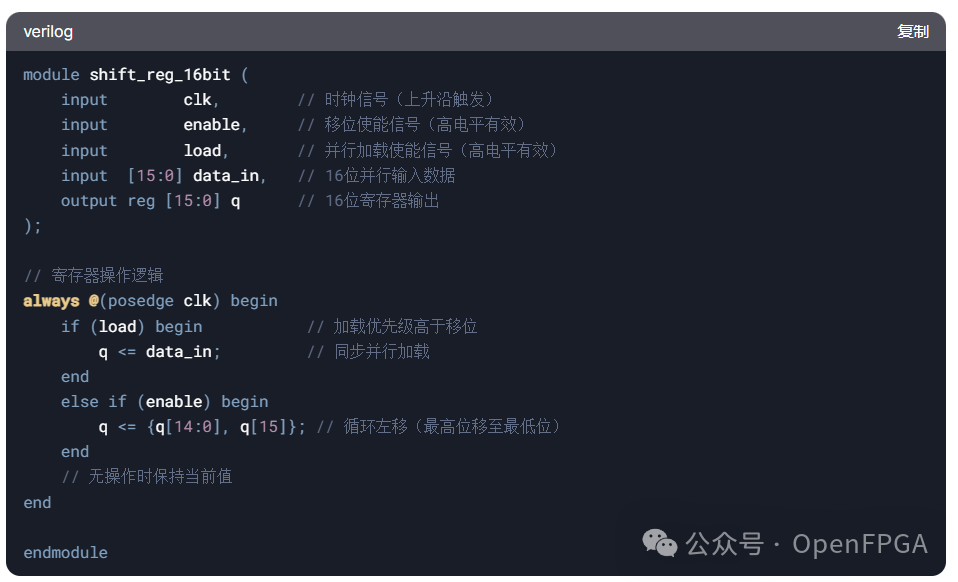

腳本設計

FPGA設計腳本設計技術樹很多都沒點,可以借助DeepSeek進行腳本設計,包括Tcl腳本設計等:

三、技術實現路徑

1. 領域知識增強

構建硬件專用知識庫:

Knowledge Base = {IEEE標準文檔 + EDA工具手冊 + 開源IP核 + 歷史項目數據}

2. 工具鏈集成

將DeepSeek接入到VSCode等代碼編寫軟件內實現提詞及代碼助寫等功能(這部分我們下一篇文章演示)。

總結

未來定制化從架構設計到GDSII交付的數據庫,配合人工進行高效率的開發,尤其DeepSeek的低硬件成本。

DeepSeek在FPGA/IC領域的應用已超越簡單的工具替代,正在重塑硬件開發范式。隨著模型持續進化,未來的芯片設計可能呈現"自然語言描述→自動生成硅片"的全新形態。這場變革不僅帶來效率躍升,更將釋放硬件創新的無限可能。對于從業者而言,掌握AI輔助設計能力將成為核心競爭力,人機協同的新時代已然到來。

大家平時用AI輔助設計嗎?用AI都希望在哪方面提供幫助?

-

FPGA

+關注

關注

1643文章

21956瀏覽量

614004 -

IC

+關注

關注

36文章

6093瀏覽量

178378 -

DeepSeek

+關注

關注

1文章

772瀏覽量

1324

原文標題:DeepSeek在FPGA/IC開發中的創新應用與未來潛力

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測

砥礪創新 芯耀未來——武漢芯源半導體榮膺21ic電子網2024年度“創新驅動獎”

激光應用未來市場在哪,DeepSeek這樣說

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

RK3588開發板上部署DeepSeek-R1大模型的完整指南

鴻蒙原生應用開發也可以使用DeepSeek了

了解DeepSeek-V3 和 DeepSeek-R1兩個大模型的不同定位和應用選擇

庫克談DeepSeek:推動效率的創新

DeepSeek-v3 在電子工程領域的應用價值

risc-v芯片在電機領域的應用展望

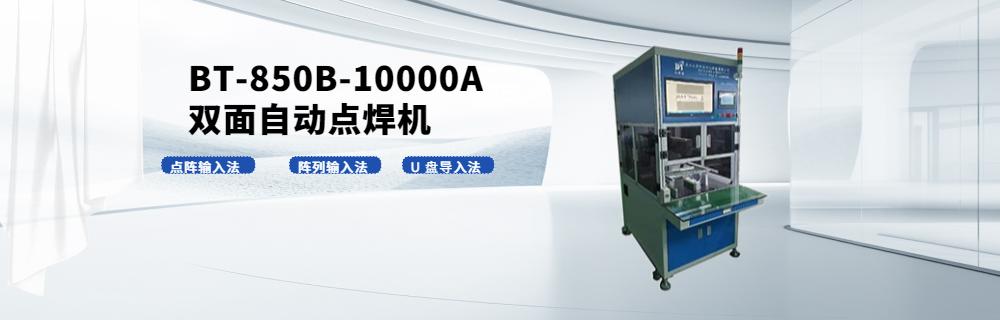

點焊技術的未來:市場動向與創新展望

DeepSeek在FPGA/IC領域的創新應用及未來展望

DeepSeek在FPGA/IC領域的創新應用及未來展望

評論