文章來(lái)源:學(xué)習(xí)那些事

原文作者:小陳婆婆

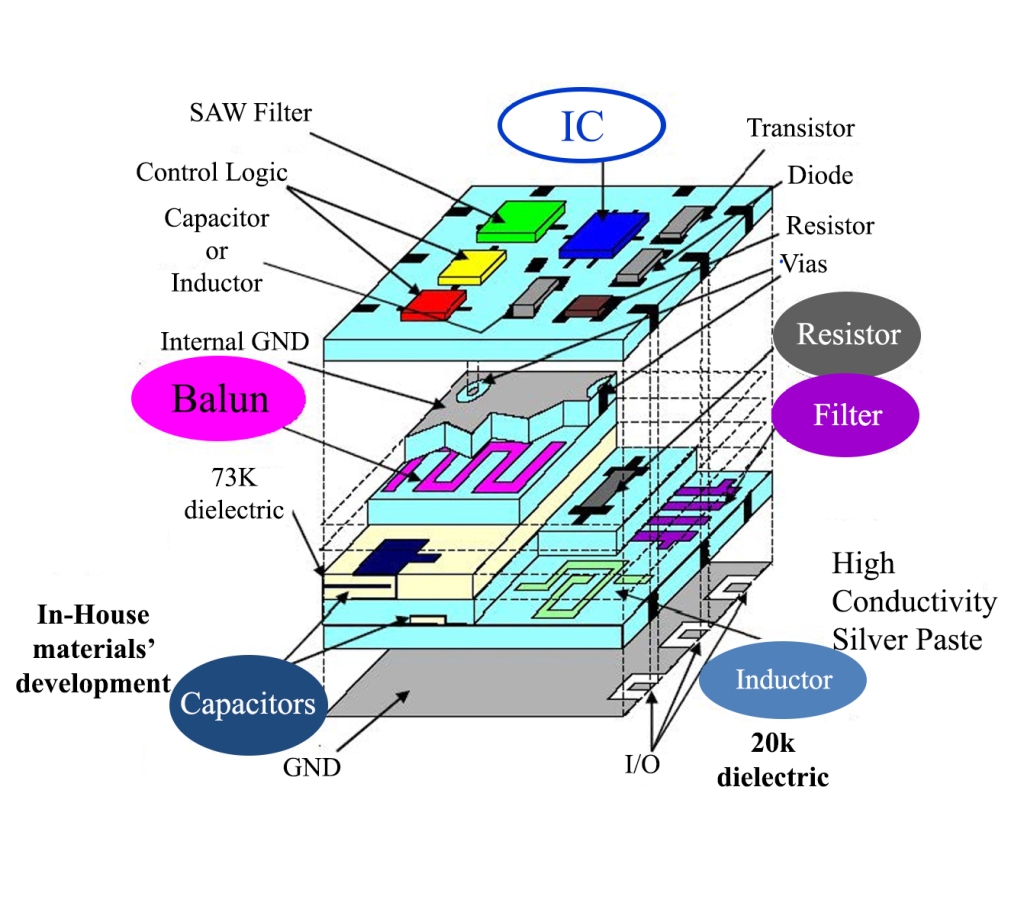

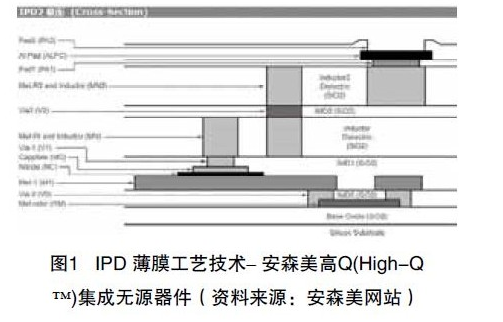

本文介紹了在射頻前端模塊(RF-FEM)中使用的集成無(wú)源元件(IPD)技術(shù)。

集成無(wú)源元件(IPD)通過(guò)將電感、電容、天線等無(wú)源器件嵌入封裝基板,顯著提升了射頻前端模塊(RF-FEM)的性能與集成度,本文分述如下:

高Q值三維螺線圈電感技術(shù)

天線集成封裝(AiP)技術(shù)

毫米波系統(tǒng)級(jí)無(wú)源元件集成

扇出式WLSI封裝技術(shù)對(duì)比

晶圓級(jí)工藝驅(qū)動(dòng)規(guī)模化降本

高Q值三維螺線圈電感技術(shù)

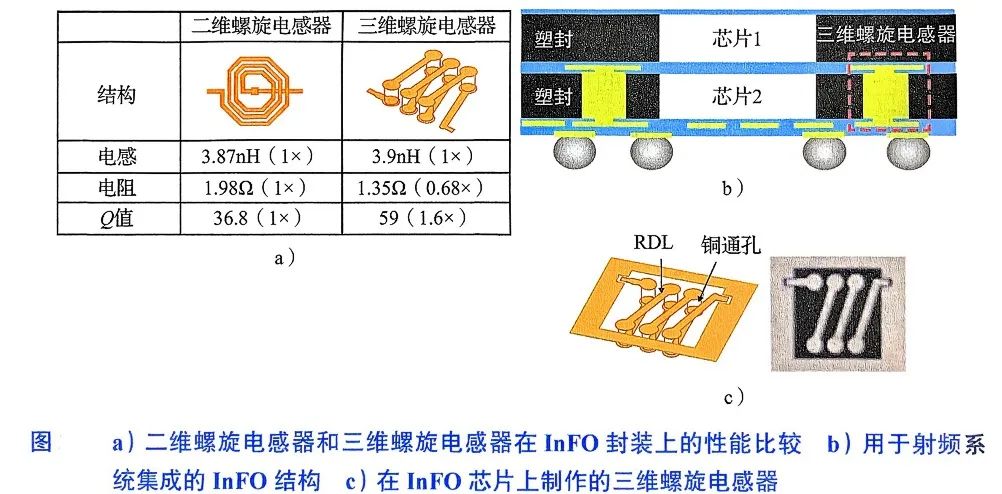

傳統(tǒng)二維螺旋電感受限于趨膚效應(yīng)與鄰近效應(yīng),在毫米波頻段Q值急劇下降。扇出封裝通過(guò)以下創(chuàng)新實(shí)現(xiàn)性能提升:

立體結(jié)構(gòu)優(yōu)化

采用RDL層構(gòu)建三維螺旋電感,線寬/間距(L/S)達(dá)2μm/2μm,層間通孔(VIA)間距5μm,形成緊湊型三匝線圈。與使用薄金屬的二維螺旋電感器相比, 在低損耗塑封料中使用厚金屬三維電感器可以獲得更高的Q值。

相較二維電感,3GHz頻點(diǎn)Q值提升1.6倍(達(dá)59),串聯(lián)電阻降低68%。

材料與工藝協(xié)同

使用低損耗環(huán)氧樹脂模塑料,將介質(zhì)損耗降至0.1dB/mm以下;

通過(guò)電化學(xué)鍍(ECP)實(shí)現(xiàn)20μm厚銅布線,較薄金屬電感Q值提升40%。

電磁耦合抑制

正交布局雙電感耦合度較平行布局降低12dB,滿足多通道射頻前端隔離度要求(>30dB)。

天線集成封裝(AiP)技術(shù)

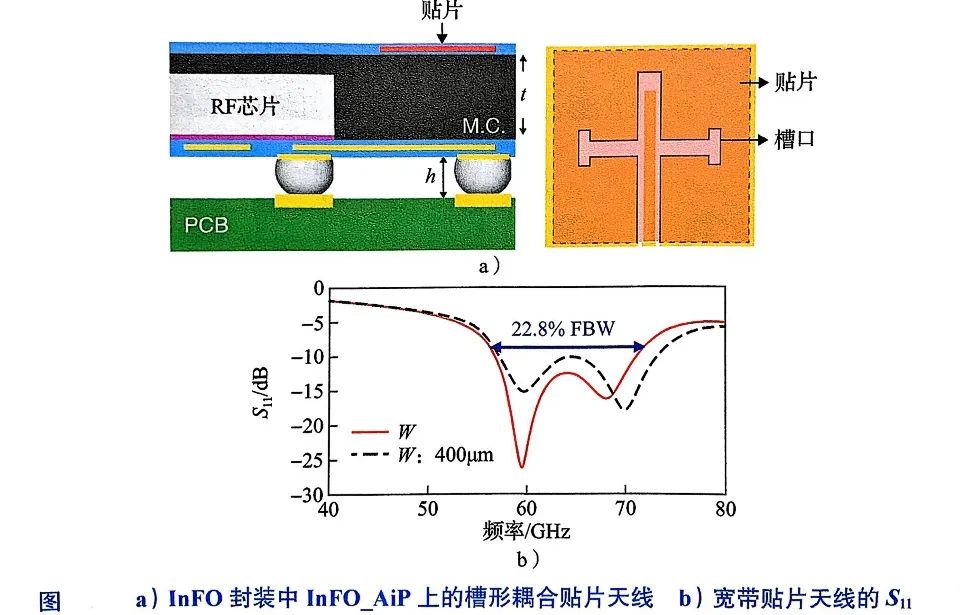

5G毫米波頻段(24-86GHz)對(duì)天線封裝提出嚴(yán)苛挑戰(zhàn),InFO技術(shù)通過(guò)三大創(chuàng)新實(shí)現(xiàn)突破:

低損耗互連通道

采用超光滑RDL表面處理(Ra<5nm),將傳輸損耗控制在0.3dB,較有機(jī)基板降低35%;

通過(guò)激光誘導(dǎo)前向轉(zhuǎn)移(LIFT)技術(shù)實(shí)現(xiàn)芯片-天線垂直互連,過(guò)渡損耗僅0.2dB。

寬帶天線設(shè)計(jì)

開發(fā)槽型耦合貼片天線,通過(guò)RDL層構(gòu)建饋電網(wǎng)絡(luò),實(shí)現(xiàn)22.8%相對(duì)帶寬(56.6-71.2GHz)。

天線效率達(dá)65%,輻射實(shí)現(xiàn)大幅度增益,滿足5G NR FR2頻段覆蓋需求。

熱機(jī)械可靠性提升

通過(guò)EMC配方優(yōu)化(CTE=8ppm/K),將熱循環(huán)壽命提升至1000次以上,滿足車載毫米波雷達(dá)可靠性要求。

毫米波系統(tǒng)級(jí)無(wú)源元件集成

InFO技術(shù)實(shí)現(xiàn)從電感到濾波器的全無(wú)源元件集成,典型應(yīng)用包括:

高性能電感陣列

構(gòu)建開口尺寸100μm的單匝線圈電感,5-49GHz頻段Q值>20,自諧振頻率(SRF)達(dá)75GHz;

通過(guò)多層RDL堆疊,實(shí)現(xiàn)300pH/460pH/600pH多值電感集成,滿足不同頻段匹配需求。

濾波器與功率分配網(wǎng)絡(luò)

采用環(huán)形諧振器實(shí)現(xiàn)32GHz/64GHz雙頻點(diǎn)濾波,插入損耗<1.5dB;

功率合成器損耗3.5dB,較片上器件降低34%,支持16通道相控陣波束成形。

傳輸線與阻抗匹配

共面波導(dǎo)(CPW)傳輸線損耗0.35dB,較CMOS后道工藝(BEOL)降低30%;

通過(guò)漸變線寬設(shè)計(jì)實(shí)現(xiàn)50Ω阻抗匹配,回波損耗>15dB。

隨著5G-Advanced與6G技術(shù)演進(jìn),IPD技術(shù)正從單一元件集成向全頻段覆蓋、多功能融合方向發(fā)展,推動(dòng)射頻前端模塊尺寸縮小50%以上,功耗降低40%。

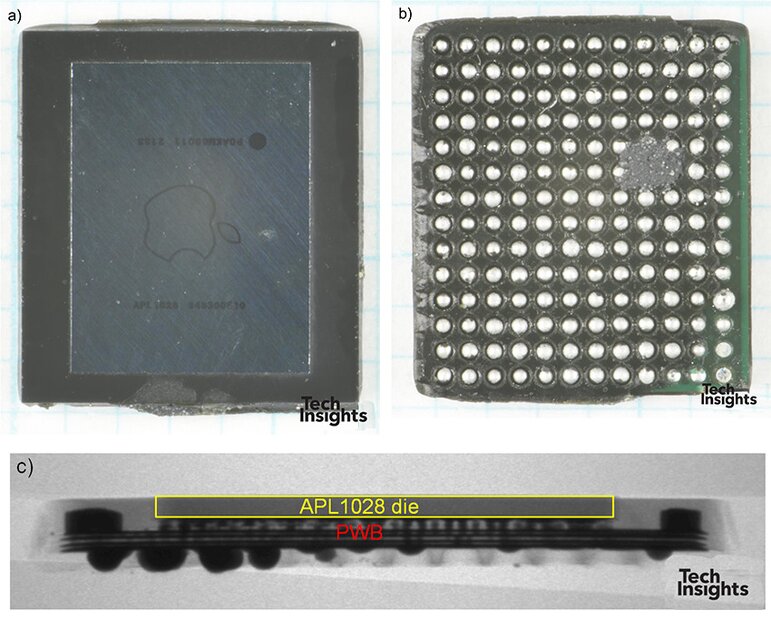

扇出式WLSI封裝技術(shù)對(duì)比

為全面評(píng)估扇出式晶圓級(jí)系統(tǒng)集成(WLSI)封裝的競(jìng)爭(zhēng)力,本研究對(duì)比了InFO PoP與倒裝芯片PoP(FC_PoP)、高帶寬存儲(chǔ)器FC-HMB PoP及硅通孔(TSV)3D IC在信號(hào)/電源完整性、熱管理、外形尺寸及成本等關(guān)鍵指標(biāo)。

InFO PoP通過(guò)以下技術(shù)實(shí)現(xiàn)信號(hào)完整性提升

超細(xì)線寬布線:采用1μm/1μm L/S RDL,較FC PoP(5μm/5μm)信號(hào)路徑縮短30%,串?dāng)_降低15dB;

陣列化BGA設(shè)計(jì):將傳統(tǒng)外圍引腳轉(zhuǎn)換為12×12陣列布局,使電源/地網(wǎng)絡(luò)覆蓋面積提升40%,同步開關(guān)噪聲(SSN)降低40%;

嵌入式去耦電容:在RDL層間集成MIM電容(容值密度0.5nF/mm2),將電源噪聲抑制至20mV以下。

相較之下,F(xiàn)C-HMB PoP雖通過(guò)額外基板實(shí)現(xiàn)BGA陣列,但受限于有機(jī)基板介電損耗(Dk≈3.8),60GHz頻段插入損耗達(dá)1.2dB,較InFO PoP高出0.7dB。

熱管理:直接散熱通道實(shí)現(xiàn)低溫升

InFO PoP的熱優(yōu)勢(shì)源于:

低熱阻路徑:邏輯芯片直接貼裝于PCB,結(jié)-環(huán)境熱阻僅45℃/W,較FC PoP(Ψja=65℃/W)降低30%;

漏電流抑制:在1.2V工作電壓下,結(jié)漏電流(Ioff)僅0.8nA,較3D IC(Ioff=3.2nA)減少75%;

功率上限提升:允許SoC功耗達(dá)8W,較FC PoP提升23%,支持高性能計(jì)算(HPC)核心頻率突破3.5GHz。

FC-HMB PoP雖通過(guò)多層基板實(shí)現(xiàn)熱擴(kuò)散,但總熱容增加導(dǎo)致瞬態(tài)熱時(shí)間常數(shù)(τ)延長(zhǎng)至120ms,較InFO PoP(τ=85ms)響應(yīng)速度降低29%。

外形尺寸:無(wú)基板設(shè)計(jì)突破厚度極限

無(wú)基板架構(gòu):總厚度僅0.8mm,較FC PoP(1.0mm)減薄20%,較3D IC(0.9mm)減薄11%;

垂直互連優(yōu)化:采用銅柱通孔(Cu TIV)替代微凸點(diǎn),z軸互連高度壓縮至50μm,較FC PoP(100μm)降低50%;

模塑料減薄技術(shù):通過(guò)激光解鍵合(Laser Debonding)實(shí)現(xiàn)EMC厚度30μm,滿足可折疊設(shè)備鉸鏈區(qū)封裝需求。

晶圓級(jí)工藝驅(qū)動(dòng)規(guī)模化降本

InFO PoP的成本優(yōu)勢(shì)

工藝整合:利用WLSI平臺(tái)共享RDL、TIV及IPD工藝,較FC PoP減少30%工藝步驟;

良率提升:通過(guò)芯片先置(Die-First)方案與預(yù)補(bǔ)償算法,使12英寸晶圓級(jí)封裝良率達(dá)96%,較3D IC(82%)提升顯著;

材料復(fù)用:采用與CMOS后道工藝兼容的低損耗EMC(Dk=3.2),較FC-HMB PoP專用基板材料成本降低40%。

市場(chǎng)周期分析顯示,InFO PoP從設(shè)計(jì)到量產(chǎn)僅需16周,較FC PoP縮短40%,滿足5G終端快速迭代需求。

綜上所述,InFO PoP通過(guò)超細(xì)RDL、直接散熱通道及晶圓級(jí)工藝整合,在性能、功耗、尺寸及成本四維指標(biāo)上形成綜合優(yōu)勢(shì),確立了其在移動(dòng)計(jì)算與邊緣AI領(lǐng)域的標(biāo)桿地位。

-

封裝

+關(guān)注

關(guān)注

128文章

8509瀏覽量

144798 -

射頻前端

+關(guān)注

關(guān)注

5文章

257瀏覽量

24675 -

無(wú)源元件

+關(guān)注

關(guān)注

1文章

1289瀏覽量

17171

原文標(biāo)題:集成無(wú)源元件(IPD)技術(shù)——扇出封裝的性能倍增器

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

集成無(wú)源元件技術(shù)對(duì)PCB技術(shù)的影響

無(wú)源元件與RF有源元件集成的策略介紹

什么是集成無(wú)源元件?對(duì)PCB技術(shù)發(fā)展產(chǎn)生了什么影響?

手機(jī)射頻技術(shù)和射頻模塊有什么關(guān)鍵元件?

手機(jī)射頻技術(shù)有什么關(guān)鍵元件?

什么是理想無(wú)源元件

無(wú)源元件介紹

cdma射頻前端的智能集成

集成無(wú)源元件對(duì)PCB技術(shù)發(fā)展的影響分析

射頻工藝和手機(jī)射頻元件的集成

集成無(wú)源元件對(duì)PCB技術(shù)發(fā)展有什么樣的影響

集成無(wú)源元件(IPC)簡(jiǎn)化了封裝中的信號(hào)調(diào)節(jié)

集成無(wú)源元件的制備工藝

集成無(wú)源元件對(duì)PCB技術(shù)發(fā)展的影響

射頻前端模塊中使用的集成無(wú)源元件技術(shù)

射頻前端模塊中使用的集成無(wú)源元件技術(shù)

評(píng)論