葉淳懿 鄔學(xué)賢 張志彬 丁萍 駱靜利 符顯珠

(深圳大學(xué)材料學(xué)院)

摘要

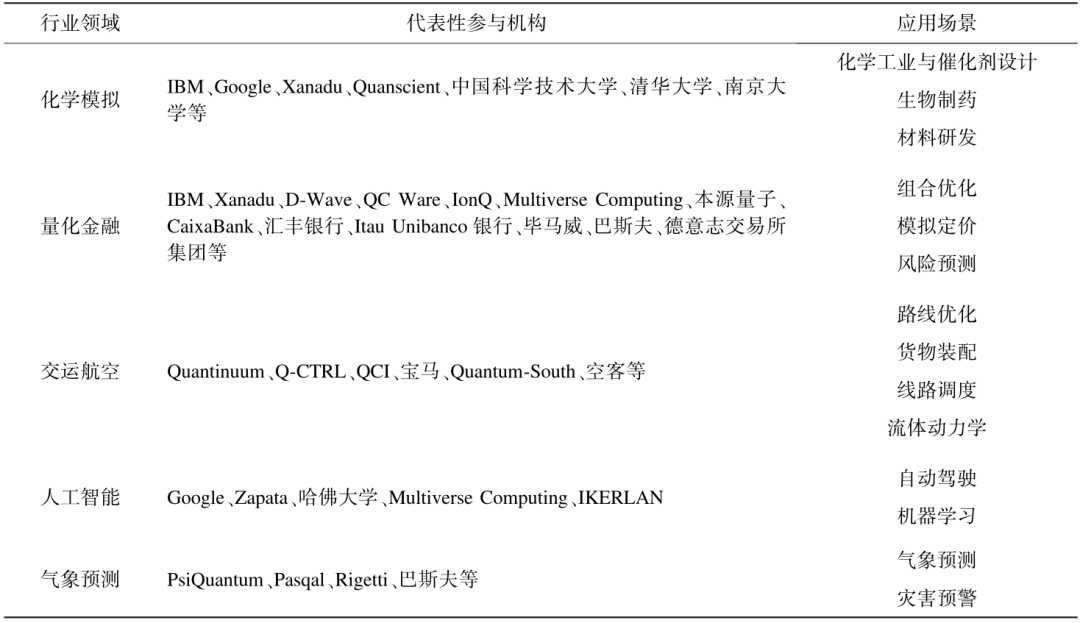

芯片制造中大量使用物理氣相沉積、化學(xué)氣相沉積、電鍍、熱壓鍵合等技術(shù)來實(shí)現(xiàn)芯片導(dǎo)電互連.與這些技術(shù)相比,化學(xué)鍍因具有均鍍保形能力強(qiáng)、工藝條件溫和、設(shè)備成本低、操作簡(jiǎn)單等優(yōu)點(diǎn),被人們期望應(yīng)用于芯片制造中,從而在近年來得到大量的研究.本綜述首先簡(jiǎn)介了芯片制造中導(dǎo)電互連包括芯片內(nèi)互連、芯片3D封裝硅通孔(TSV)、重布線層、凸點(diǎn)、鍵合、封裝載板孔金屬化等制程中傳統(tǒng)制造技術(shù)與化學(xué)鍍技術(shù)的對(duì)比,說明了化學(xué)鍍用于芯片制造中的優(yōu)勢(shì);然后總結(jié)了芯片化學(xué)鍍的原理與種類、接枝與活化前處理方法和關(guān)鍵材料;并詳細(xì)介紹了芯片內(nèi)互連和TSV互連化學(xué)鍍阻擋層、種子層、互連孔填充、化學(xué)鍍凸點(diǎn)、再布線層、封裝載板孔互連種子層以及凸點(diǎn)間鍵合的研究進(jìn)展;且討論了化學(xué)鍍液組成及作用,超級(jí)化學(xué)鍍填孔添加劑及機(jī)理等.最后對(duì)化學(xué)鍍技術(shù)未來應(yīng)用于新一代芯片制造中進(jìn)行了展望.

1引言

芯片指內(nèi)含集成電路而體積很小的硅片,是電子設(shè)備的“大腦”.在信息時(shí)代,芯片是各行業(yè)的核心基石,電腦、手機(jī)、家電、汽車、高鐵、電網(wǎng)、醫(yī)療儀器、機(jī)器人、工業(yè)控制等各種電子產(chǎn)品和系統(tǒng)都離不開芯片[1].芯片產(chǎn)業(yè)是一個(gè)國(guó)家高端制造能力的綜合體現(xiàn),是全球高科技國(guó)力競(jìng)爭(zhēng)的戰(zhàn)略必爭(zhēng)制高點(diǎn).目前我國(guó)已有華為、龍芯、歐加、阿里巴巴、寒武紀(jì)等公司能夠設(shè)計(jì)出先進(jìn)芯片,但在高端芯片制造領(lǐng)域還薄弱,芯片為我國(guó)第一大宗進(jìn)口商品.在三星、臺(tái)積電已能量產(chǎn)5 nm制程芯片的當(dāng)下,我國(guó)大陸也僅有中芯國(guó)際能夠量產(chǎn)14 nm制程的芯片.倘若西方國(guó)家進(jìn)行技術(shù)封鎖,我國(guó)有可能面臨無(wú)芯可用的窘境.因此,對(duì)芯片制造技術(shù)的研究就顯得尤為重要.

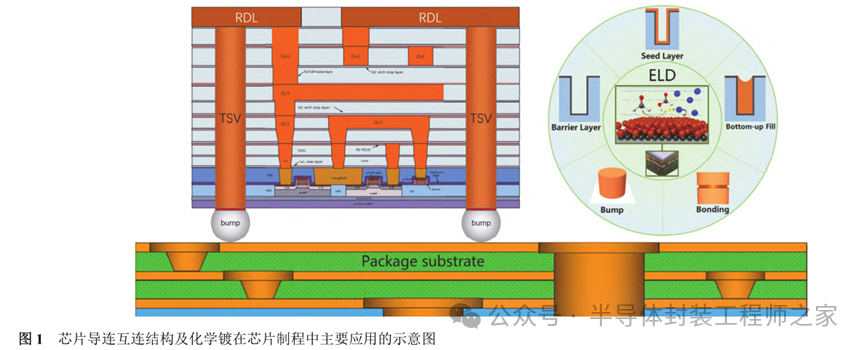

如圖1所示,芯片的制造可分為前段工藝(FEOL,Front End of Line)、后段工藝(BEOL, Back End of Line)及后繼的芯片封裝等.前段工藝就是在單晶硅片上制造出晶體管.而后段工藝則是在一層層的絕緣材料上進(jìn)行穿孔(Via)和金屬布線,將前段工藝中的晶體管進(jìn)行導(dǎo)電互連[2].此外,后續(xù)封裝中將會(huì)涉及TSV、芯片封裝載板盲孔與通孔、重布線層(RDL)、凸點(diǎn)(bump)、凸點(diǎn)下金屬過渡層(UBM)及凸點(diǎn)間的鍵合等關(guān)鍵工藝,主要目的也是實(shí)現(xiàn)高效導(dǎo)電互連.目前, BEOL及TSV中的阻擋層、種子層主要使用物理氣相沉積(PVD)或化學(xué)氣相沉積(CVD)方法制造,金屬的填充使用電鍍銅制備[3-5].芯片級(jí)細(xì)凸點(diǎn)通常使用電沉積技術(shù)制造,凸點(diǎn)間的鍵合則可通過熱壓實(shí)現(xiàn)[6].但是隨著芯片線寬的不斷縮小,上述技術(shù)會(huì)面臨著一些難以克服的缺點(diǎn).且不談PVD、CVD技術(shù)所要求的昂貴設(shè)備,使用它們制造的阻擋層和種子層,在面對(duì)高縱橫比的通孔時(shí)難以保證完美覆蓋率,最終可能導(dǎo)致金屬填充的失敗.對(duì)于銅柱凸點(diǎn)間的鍵合,如果使用熱壓方式則需要較高的溫度和較大的壓力,這對(duì)于芯片導(dǎo)電互連長(zhǎng)效服役是不利的[7].

化學(xué)鍍作為一種金屬沉積工藝,它可以不需高成本設(shè)備、不需要電流及導(dǎo)電基體就能夠在復(fù)雜形狀的基體包括含有細(xì)孔徑的深孔基體上均勻沉積金屬層,并且工藝成本低、實(shí)施簡(jiǎn)單方便,已被廣泛應(yīng)用于印制線路板[8]、芯片封裝載板、UBM中阻擋層、柔性電路[9-14]、集流體[15]、傳感器[16]、電磁屏蔽[17]、導(dǎo)熱散熱[18]、防腐裝飾及多種功能性涂層等制造上.化學(xué)鍍被許多研究者積極研究用于芯片制造中的阻擋層、種子層、孔填充金屬互連、銅柱凸點(diǎn)之間的金屬低溫濕制程鍵合等.本綜述將對(duì)比傳統(tǒng)芯片制造導(dǎo)電互連工藝技術(shù)與化學(xué)鍍技術(shù),介紹用于芯片制造中的化學(xué)鍍技術(shù)研究進(jìn)展,并對(duì)它們進(jìn)行總結(jié)與展望,為今后芯片制造領(lǐng)域中的化學(xué)鍍應(yīng)用提供參考.

2芯片化學(xué)鍍?cè)砼c制程

2.1芯片化學(xué)鍍?cè)砑俺S缅兎N

化學(xué)鍍就是溶液中的金屬離子在還原劑的催化還原作用下只在需要進(jìn)行鍍覆的基體上形成金屬鍍層的一種技術(shù)[19].化學(xué)鍍總反應(yīng)式如式(1):

其中, Ox是還原劑Red的氧化產(chǎn)物.該反應(yīng)又可分為陰極部分和陽(yáng)極部分:

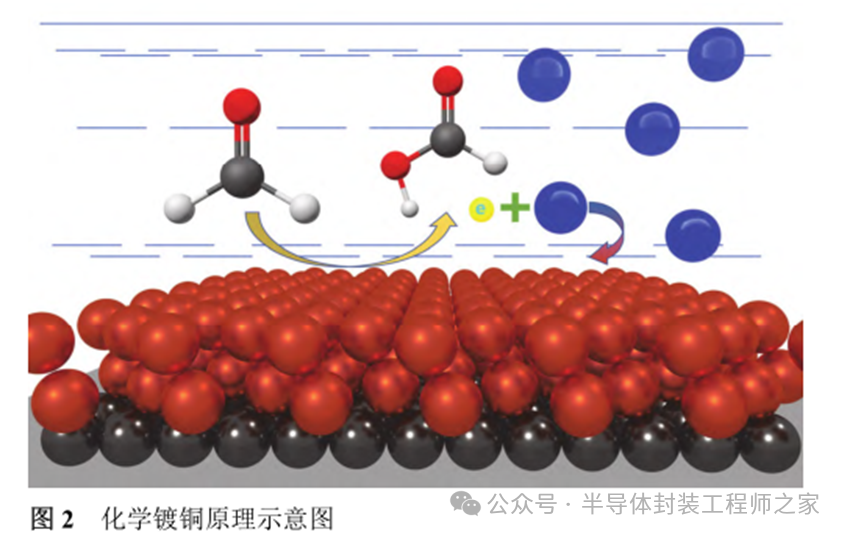

式(2)、(3)中z和m表示電子數(shù).上述反應(yīng)發(fā)生在同一電極、同一溶液金屬界面上,因此需要讓還原劑的平衡電位比金屬電極的平衡電位更負(fù)才能保證反應(yīng)的持續(xù)發(fā)生.以芯片化學(xué)鍍工藝中常見的甲醛還原銅離子的化學(xué)鍍銅工藝為例,討論其機(jī)理(圖2).以甲醛作為化學(xué)鍍銅的還原劑時(shí),其總反應(yīng)如式(4):

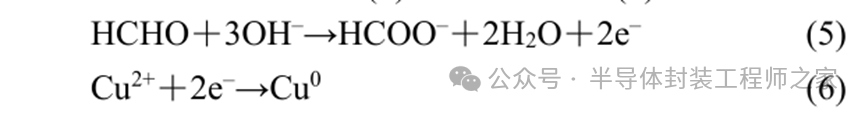

可分為陽(yáng)極反應(yīng)式(5)與陰極反應(yīng)式(6):

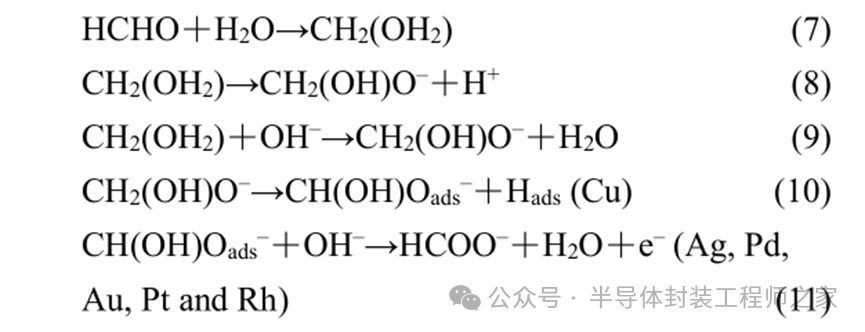

上述反應(yīng)可細(xì)分為幾個(gè)步驟:甲醛在水合后解離(式(7)、式(8)),與氫氧化物離子反應(yīng)生成亞甲二醇陰離子(式(9)).亞甲二醇陰離子隨后繼續(xù)在催化劑金屬表面反應(yīng)(式(10)、式(11)).

最后在催化劑金屬表面發(fā)生析氫反應(yīng):

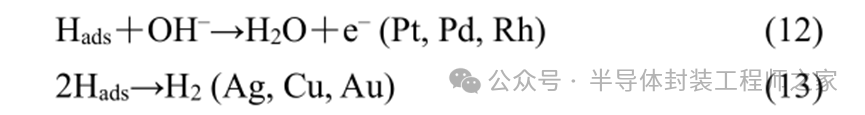

上述反應(yīng)機(jī)理表明化學(xué)鍍反應(yīng)離不開催化劑的存在.芯片化學(xué)鍍工藝中,催化劑緊密地吸附在基體上,化學(xué)鍍反應(yīng)在催化劑表面進(jìn)行,保證了工藝的選擇性和保形性,同時(shí)也是化學(xué)鍍工藝應(yīng)用于芯片制造的優(yōu)勢(shì).表1列出了芯片制造中常見單金屬化學(xué)鍍種類,在此基礎(chǔ)上可以添加錸鹽酸、鉬酸鹽、鎢酸鹽等金屬鹽以及次磷酸鹽、二甲胺硼烷(DMAB)等非金屬鹽來實(shí)現(xiàn)NiP、CoB、NiReP、CoWP等二元、多元合金的沉積.

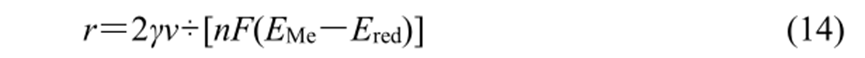

提升反應(yīng)溫度可以促進(jìn)化學(xué)鍍的進(jìn)行,但溫度太高也可能導(dǎo)致鍍液分解.鍍液的自發(fā)分解取決于以下因素:溶液中成核的概率和速率,以及核生長(zhǎng)與溶解的關(guān)系.臨界核半徑的方程式為:

其中 γ 為金屬溶液界面的表面張力,ν 為金屬的摩爾體積, EMe和ERed是金屬和還原劑在溶液中的電動(dòng)勢(shì).當(dāng)r的實(shí)際值大于理論值時(shí),發(fā)生自發(fā)分解.通過使用添加劑和絡(luò)合劑,同時(shí)調(diào)節(jié)溶液的pH值,可以使沉積過程的(EMe-ERed)值盡可能地小.添加劑還可以通過吸附在晶核上并阻止晶核生長(zhǎng)來毒化催化劑表面,從而導(dǎo)致晶核溶解.此外,使用表面活性劑可以降低鍍液的表面張力,有利于去除鍍層表面產(chǎn)生的氫氣泡[20].

2.2芯片化學(xué)鍍前接枝與接枝劑

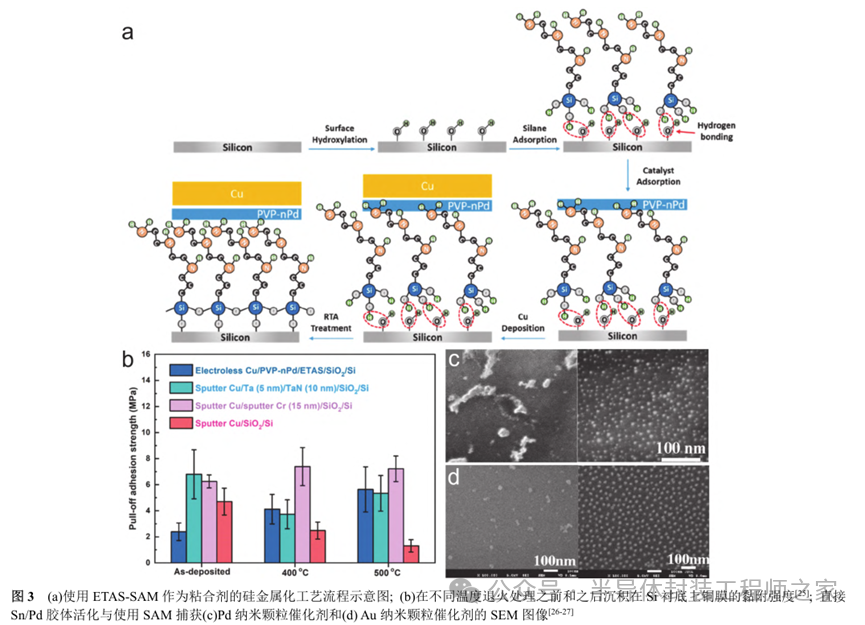

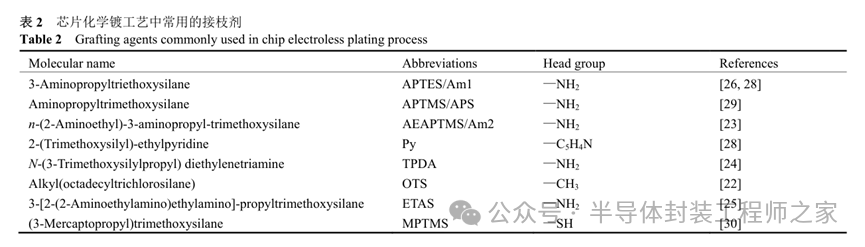

化學(xué)鍍金屬層要在芯片基體上高效催化沉積并與基體具有良好的結(jié)合力,這主要通過對(duì)化學(xué)鍍前基體的處理來保障[21].由于芯片化學(xué)鍍工藝的特殊性,常用的前處理關(guān)鍵步驟為接枝改性和活化.自組裝單分子層(SAM)已被證明可在微電子和生物醫(yī)學(xué)工程等各種應(yīng)用領(lǐng)域中用作偶聯(lián)劑、催化劑捕獲層、擴(kuò)散屏障、腐蝕抑制劑和黏附促進(jìn)劑等[22].在芯片化學(xué)鍍工藝中,接枝處理后可以在基底表面形成SAM,用于捕獲催化劑離子或催化劑顆粒.使用SAM的一個(gè)關(guān)鍵理由在于它能起到增強(qiáng)基底對(duì)鍍層黏附強(qiáng)度的作用,以支持鍍層經(jīng)過后續(xù)化學(xué)機(jī)械拋光(CMP)而不脫落.常見的接枝步驟如下: (1)使用清潔溶液(通常包含過氧化氫、硫酸或氨水)清洗基底并干燥,實(shí)現(xiàn)基底表面的羥基化; (2)在一定溫度下,將基底浸入含有接枝劑的甲苯或乙醇溶液一定時(shí)間后取出清洗并干燥,在基底上得到SAM; (3)用標(biāo)準(zhǔn)清洗液(SC-1,包含過氧化氫及氨水)對(duì)SAM進(jìn)行功能化或是對(duì)樣品進(jìn)行烘烤使SAM致密化(可選)[22-24].以Si為基底, 3-[2-(2-氨基乙基氨基)乙基氨基]丙基-三甲氧基硅烷(ETAS)為接枝劑為例,如圖3a所示,使用微蝕刻溶液對(duì)基底表面處理后會(huì)帶上羥基基團(tuán). ETAS的分子結(jié)構(gòu)以Si原子為中心,連接著三個(gè)含甲氧基(-OCH3)的頭部基團(tuán)和一個(gè)烷基鏈,烷基鏈尾部有一個(gè)游離氨基(-NH2).由于頭部基團(tuán)與基底表面羥基之間氫鍵的作用力, ETAS在基底上組裝成SAM, ETAS尾部的氨基會(huì)捕獲Pd催化劑從而起到活化的作用.此外,經(jīng)過退火處理, ETAS分子與Si襯底之間、兩個(gè)相鄰ETAS分子之間均會(huì)發(fā)生脫水反應(yīng),從而大幅提高黏附強(qiáng)度,黏附強(qiáng)度與退火溫度之間的關(guān)系如圖3b所示[25].使用SAM捕獲催化劑,相比于直接活化,可以獲得粒徑更小、密度更高的催化劑.如圖3c、3d所示,由SAM捕獲的不論是Pd還是Au催化劑,其催化劑粒徑及密度都要比直接使用Sn/Pd膠體活化更加優(yōu)秀[26-27].表2列舉了芯片化學(xué)鍍工藝中常用的接枝劑.

2.3芯片化學(xué)鍍前活化及活化劑

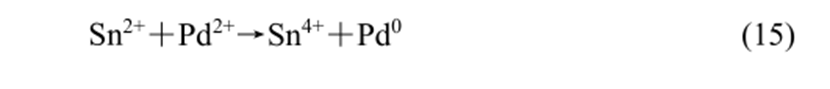

活化的目的在于讓基材表面附著上具有催化活性的Pd、Ag、Au、Ru等催化劑促使金屬離子還原的化學(xué)鍍反應(yīng)能夠進(jìn)行,活性顆粒自身的催化活性以及在基材表面上的分布形態(tài)等均會(huì)影響后續(xù)化學(xué)鍍性能.化學(xué)鍍中最為常用的活化方式為Sn/Pd膠體活化. Pd是貴金屬,成本高.作者所在課題組為降低化學(xué)鍍活化劑成本,開發(fā)了空心多孔Pd納米球[31]、多孔空心PdCu納米框[32-34]、納米Sn棒載Ag[9]、納米Cu、Ag膠水[15]、銀離子油墨[35]等多種催化劑,能夠?qū)崿F(xiàn)良好的化學(xué)鍍銅導(dǎo)電互連.相比于直接吸附催化劑納米顆粒的一步活化法,敏化-活化法先使用二氯化錫(SnCl2)對(duì)基材進(jìn)行敏化,吸附在基底上的Sn離子可以有效降低樣品表面張力并改善潤(rùn)濕性能,降低表面能,并為金屬催化劑離子還原提供了均勻分布的位點(diǎn),從而增加催化劑納米顆粒的覆蓋率.此外,敏化后吸附在基底上的Sn離子會(huì)與Pd離子發(fā)生如下反應(yīng):

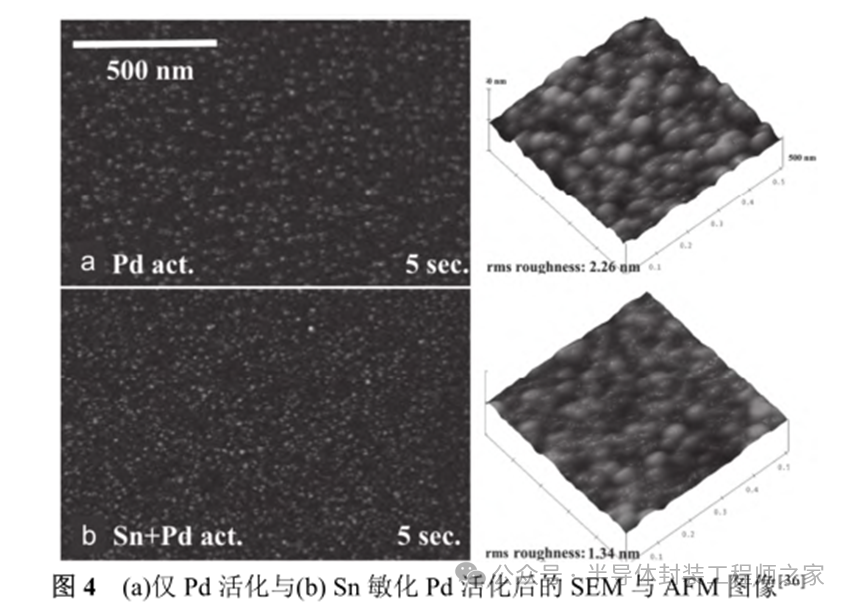

將Pd離子還原為Pd納米顆粒[36-37].如圖4所示,經(jīng)過敏化處理的基底吸附的Pd納米顆粒密度更高,粒徑更小.原子力顯微鏡(AFM)測(cè)試結(jié)果表明,敏化活化法相比起直接活化,表面粗糙度降低了約40%,說明吸附的Pd納米顆粒更傾向于平面覆蓋.

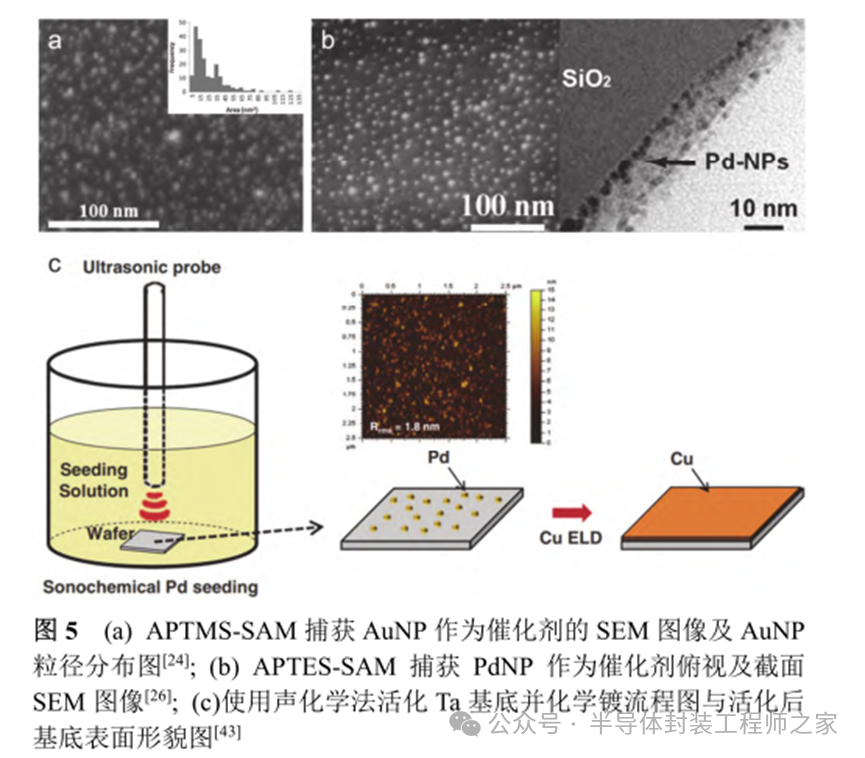

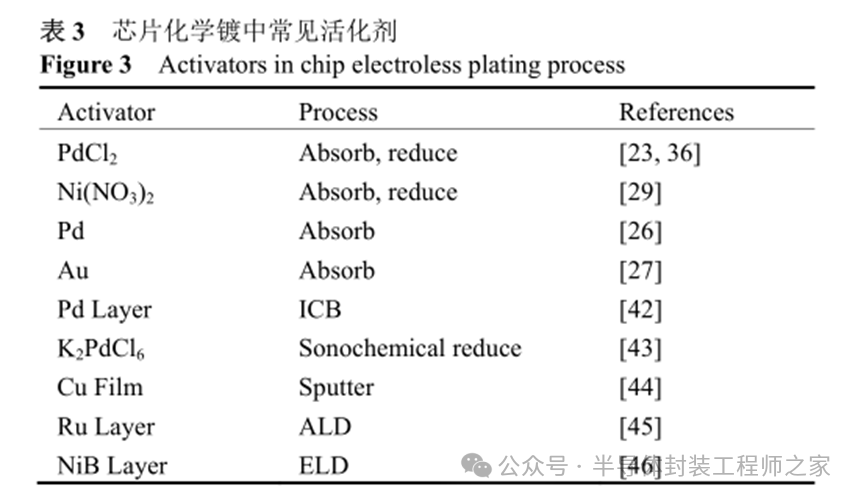

SAM可以捕獲金屬離子,直接將帶有SAM的基底浸入含鹽酸的氯化鈀溶液中,基底便會(huì)吸附Pd離子.在后續(xù)化學(xué)鍍時(shí),鍍液中的還原劑會(huì)將Pd離子還原成有催化活性的Pd納米顆粒[38],從而催化化學(xué)鍍金屬層沉積[23,39].將氯化鈀溶液換成硝酸鎳溶液, SAM同樣可以吸附Ni離子.與Pd不同的是, Ni離子較不容易被還原,因此在化學(xué)鍍前需要將基底先浸入強(qiáng)還原劑硼氫化鈉溶液中將Ni離子還原為Ni納米顆粒,之后再進(jìn)行化學(xué)鍍[29].如圖5a、5b所示,除金屬離子外, SAM也能直接從鈀納米顆粒(PdNP)、金納米顆粒(AuNP)活化劑中捕獲Pd、Au等納米顆粒用于活化[24,26-27,40-41]. Inoue等[27,40]認(rèn)為AuNP所帶的電荷使它們之間存在靜電斥力,在活化時(shí)可以保證高密度吸附而不團(tuán)聚,但在硅工藝中使用Au可能帶來嚴(yán)重的金屬污染,因此后續(xù)的實(shí)驗(yàn)中棄用了AuNP轉(zhuǎn)而使用PdNP. Shingubara等[42]用電離簇束(ICB)沉積1 nm超薄Pd作為化學(xué)鍍催化層. Lim等[43]將Ta基底浸入六氯鈀酸鉀溶液中,超聲使水聲解產(chǎn)生H?自由基還原Pd(IV),從而實(shí)現(xiàn)Ta基底的活化(圖5c). Lin等[44]使用濺射沉積的銅膜代替鋅作為化學(xué)鍍UBM的活化層. Inoue等[45]在原子層沉積(ALD)的10 nm厚釕層上化學(xué)鍍Cu種子層,納米金屬釕層起到了催化作用.因?yàn)橹苯釉赑d活化的SAM上化學(xué)鍍CoWP會(huì)成長(zhǎng)為不連續(xù)的島狀, Osaka等[46]先化學(xué)鍍NiB層,將其作為催化層再化學(xué)鍍連續(xù)的CoWP阻擋層.化學(xué)鍍中的活化劑可謂是多種多樣,表3列舉了一些芯片化學(xué)鍍制程中的常見活化劑.

3芯片導(dǎo)電互連制程

3.1芯片內(nèi)互連制程

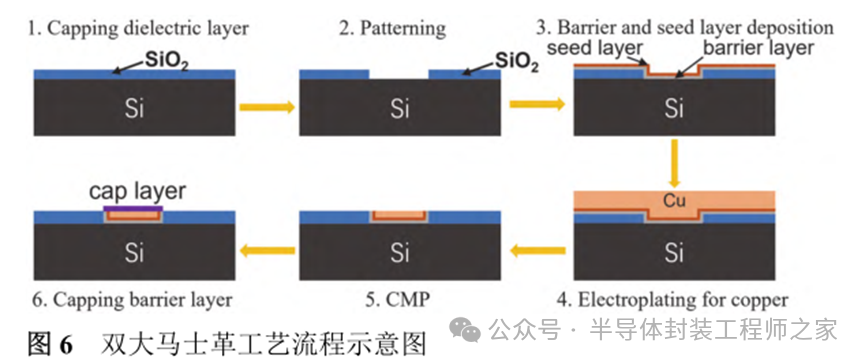

早期,在芯片制造的后段工藝中人們使用鋁(Al)作為導(dǎo)電互連金屬.但隨著芯片中晶體管數(shù)量增加和線寬縮小, RC延遲(R為芯片中互連線的電阻, C為基板的電容)成為影響芯片速率的重要因素[47].為了解決這個(gè)問題, IBM于1997年提出用導(dǎo)電性更好的Cu代替Al作為芯片的互連材料.與Al相比, Cu的電阻率更低,可以有效降低延遲.但是Cu易腐蝕,且容易向二氧化硅(SiO2)或硅(Si)基材擴(kuò)散,從而影響絕緣體或半導(dǎo)體的特性.應(yīng)用于Al的工藝技術(shù)無(wú)法直接應(yīng)用于Cu,因此雙大馬士革互連線工藝應(yīng)運(yùn)而生[48].如圖6所示,先在Si基材表面形成一層SiO2介電層,然后在介電層上刻蝕出溝槽(trench)和穿孔.緊接著使用PVD或CVD沉積一層擴(kuò)散阻擋層,用于防止填充的Cu金屬向介電層擴(kuò)散.隨著晶圓尺寸的增大,傳統(tǒng)阻擋層過大的電阻導(dǎo)致的IR壓降會(huì)讓后續(xù)使用大馬士革工藝電鍍填充Cu時(shí)出現(xiàn)Cu沉積不均勻的情況,因此必須在填充Cu之前使用PVD或CVD沉積一層導(dǎo)電的種子層.隨后在各種添加劑的作用下,實(shí)現(xiàn)自下而上的電鍍Cu填充[49].電鍍完成后還需要進(jìn)行CMP去除多余的Cu,實(shí)現(xiàn)平坦化.最后可以覆蓋一層阻擋層,并繼續(xù)進(jìn)行下一層的大馬士革工藝[50].

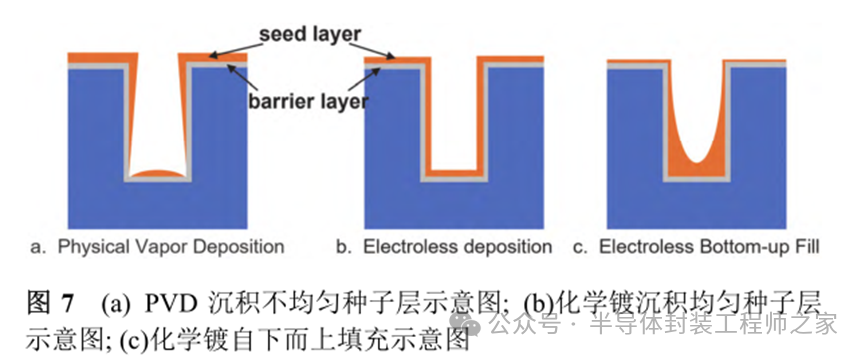

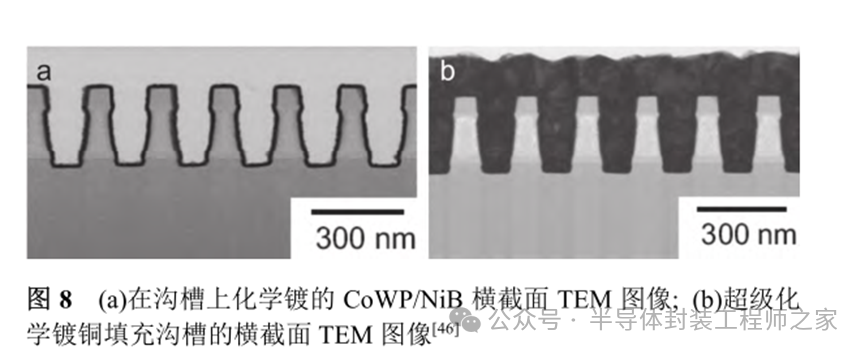

但正如前述, PVD、CVD技術(shù)不僅設(shè)備昂貴,而且面對(duì)線寬逐漸縮小的制程,無(wú)法保證完整覆蓋溝槽和穿孔,或是引起“倒垂”現(xiàn)象(圖7a),導(dǎo)致后續(xù)電鍍填充金屬的步驟失敗.而化學(xué)鍍優(yōu)秀的均勻鍍覆保形能力不僅可用于制作阻擋層或種子層(圖7b),還能在添加劑的配合下直接進(jìn)行孔填充金屬(圖7c). Osaka等[46]使用3-氨基 丙 基 三 乙 氧 基 硅 烷(APTES)對(duì)已 刻 蝕 出 溝 槽 的SiO2/Si晶圓進(jìn)行硅烷化,隨后將其浸入PdCl2溶液中吸附Pd離子.在含有硫酸鎳、檸檬酸和DMAB的溶液中,Pd離子會(huì)被還原成Pd納米顆粒并催化化學(xué)鍍鎳,得到NiB層.在含有硫酸鈷、鎢酸鈉、檸檬酸鈉、次磷酸鈉及硼酸的溶液中, Ni層會(huì)作為化學(xué)鍍CoWP的催化劑,獲得CoWP/NiB阻擋層(圖8a).最后,他們?cè)诰垡叶?PEG)添加劑的配合下,使用乙醛酸還原硫酸銅超級(jí)化學(xué)鍍銅填孔,實(shí)現(xiàn)了溝槽內(nèi)的自下而上填充(圖8b).在500℃下退火30 min,未觀察到Cu的擴(kuò)散,說明該阻擋層能較好地發(fā)揮阻擋作用.使用超級(jí)化學(xué)鍍填孔可以減少種子層沉積和電沉積工序,在不導(dǎo)電的絕緣層或阻擋層上直接一步化學(xué)鍍填充導(dǎo)電互連金屬.

3.2三維封裝TSV制程

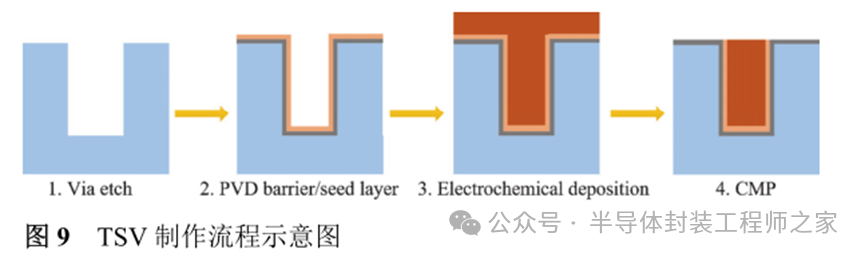

在芯片制程發(fā)展逐漸遇到瓶頸的今天,芯片的3D封裝是人們能夠繼續(xù)追趕摩爾定律的有效手段.將芯片堆疊并用TSV連接是如今最常使用的芯片3D封裝方法. TSV的制造在某種程度上與芯片內(nèi)互連大馬士革工藝非常相近.如圖9所示,對(duì)基材進(jìn)行垂直刻蝕后,用PVD技術(shù)沉積擴(kuò)散阻擋層與種子層,用于防止填充的銅擴(kuò)散至基材中及電鍍填充金屬.在電鍍填充銅后,通過CMP去除多余的金屬[51].

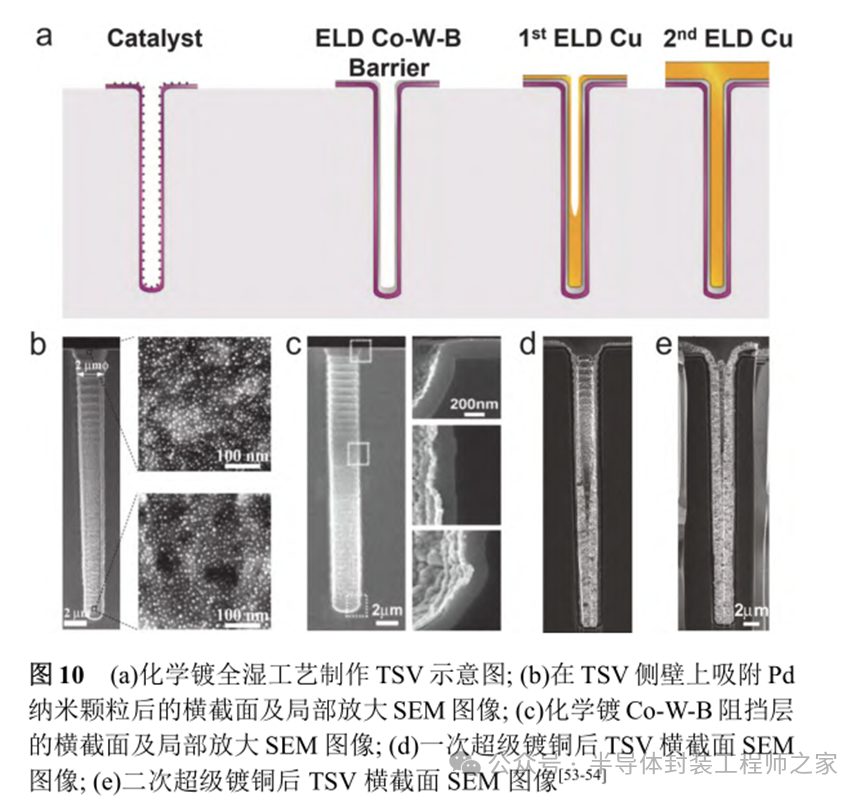

芯片內(nèi)部空間“寸土寸金”, TSV孔徑面積如果過大勢(shì)必會(huì)造成浪費(fèi),因此隨著人們對(duì)芯片要求的提高,TSV所占用的面積不斷縮小.孔徑面積的縮小意味著縱橫比的提高, PVD技術(shù)在面對(duì)較大縱橫比的TSV時(shí),無(wú)法做到完整覆蓋阻擋層或種子層,最終造成金屬填充失敗[52].如圖10a所示, Inoue等[53-54]提出了使用化學(xué)鍍?nèi)珴窆に囍谱鱐SV的方法.使用APTES在TSV內(nèi)形成SAM,用于吸附高密度的Pd納米顆粒作為催化劑(圖10b),化學(xué)鍍Co-W-B阻擋層(圖10c).當(dāng)化學(xué)鍍Co-W-B阻擋層厚度小于40 nm時(shí),黏附強(qiáng)度與濺射制備的Co膜相當(dāng).在該阻擋層上,使用乙醛酸作為還原劑可以在無(wú)需催化劑的情況下通過置換反應(yīng)激活化學(xué)鍍銅.此外,通過在鍍液中添加PEG及聚二硫二丙烷磺酸鈉(SPS),經(jīng)過二次化學(xué)鍍銅,實(shí)現(xiàn)了高縱橫比TSV的超級(jí)化學(xué)鍍銅填充(圖10d、10e).通過化學(xué)鍍工藝制作的TSV,過鍍的銅層較少,節(jié)約了后續(xù)CMP的時(shí)間及成本,而且實(shí)現(xiàn)了阻擋層沉積與TSV填孔的全化學(xué)鍍工藝,不再需電沉積填孔步驟.

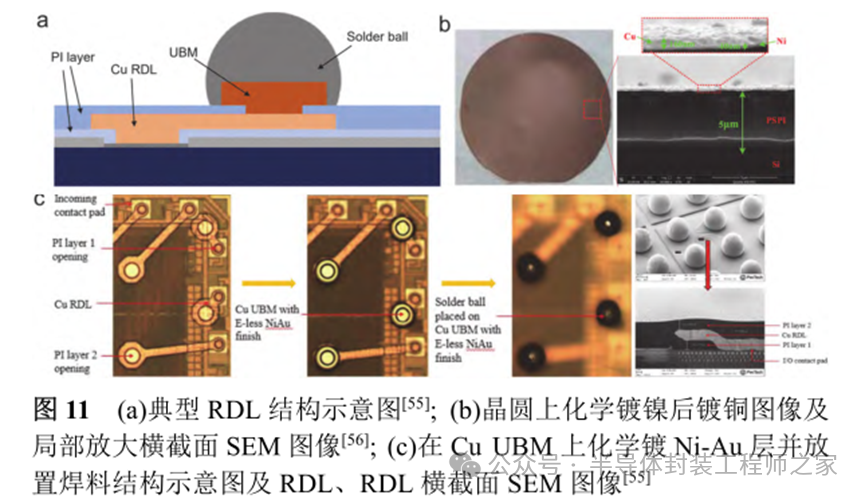

3.3RDL、凸點(diǎn)及鍵合

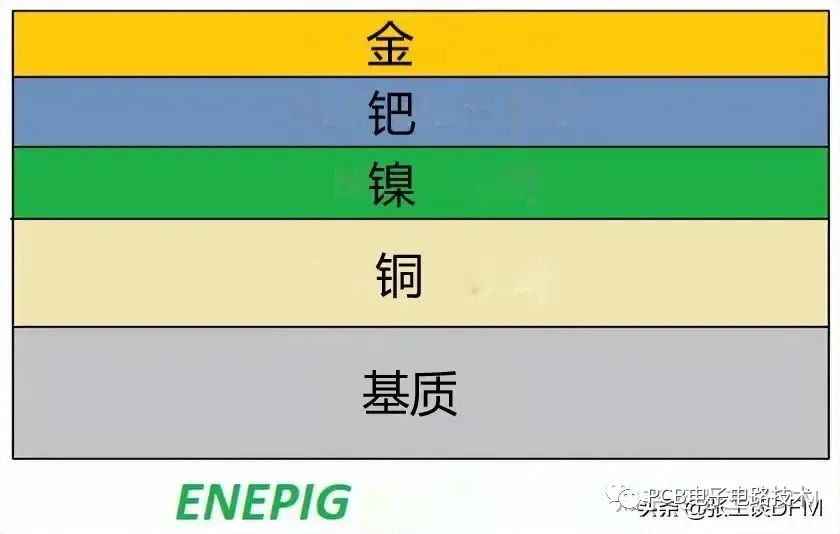

當(dāng)輸入/輸出(I/O)焊盤太小或太密集而導(dǎo)致無(wú)法進(jìn)行可靠的焊料連接時(shí),便需要RDL將I/O焊盤分布到其他位置,降低基板與元件之間的應(yīng)力,提高可靠性.典型的RDL如圖11a所示,制作時(shí)步驟如下: (1)在芯片表面已有的焊盤及鈍化層上覆蓋聚合物介電層,并通過光刻技術(shù)去除焊盤上方的覆蓋使其暴露; (2)覆蓋一層TiW或Cu種子層,并用臨時(shí)抗蝕劑創(chuàng)建“電鍍模板”,進(jìn)行電鍍沉積銅引線,最后去除抗蝕劑和種子層; (3)繼續(xù)覆蓋介電層,用于保護(hù)銅引線并通過光刻技術(shù)使其暴露在新焊盤位; (4)用臨時(shí)抗蝕劑創(chuàng)建“電鍍模板”或“蝕刻模板”,通過電鍍或?yàn)R射沉積來制作UBM層,用于連接焊盤與凸點(diǎn),提供擴(kuò)散阻擋性能; (5)通過電鍍或放置焊球在UBM上制作凸點(diǎn).凸點(diǎn)間的連接通常采用熱壓鍵合.步驟(1)至(4)均需要采用高成本光刻技術(shù),兩次使用臨時(shí)抗蝕劑,兩次覆蓋介電層,如果能夠優(yōu)化其中的步驟,降低成本,即可提高RDL技術(shù)的競(jìng)爭(zhēng)力[55].使用氧等離子處理聚酰亞胺(PI)介電層可使其表面變得粗糙,增大后續(xù)金屬層的黏附強(qiáng)度.選用化學(xué)鍍鎳作為阻擋層,并通過堿性溶液處理PI使酰亞胺環(huán)發(fā)生裂解反應(yīng)來進(jìn)一步增大對(duì)Ni層的粘附力.在化學(xué)鍍鎳后,進(jìn)行化學(xué)鍍銅制備種子層(圖11b).相比濺射等工藝,化學(xué)鍍阻擋層與種子層對(duì)設(shè)備要求低、成本低,且實(shí)現(xiàn)了全濕工藝[56],芯片封裝載板孔金屬化及半加成工藝中銅種子層也是使用化學(xué)鍍工藝制備.臭氧處理具有可擴(kuò)展性,適用于大面板的晶圓工藝,對(duì)化學(xué)鍍銅種子層進(jìn)行處理后可以提升后續(xù)電鍍的質(zhì)量[57].用硝酸溶液對(duì)新的銅焊盤進(jìn)行刻蝕處理,可以使用次磷酸鈉作為還原劑,在酸性硫酸鎳溶液中化學(xué)鍍鎳制作UBM[44]. Yeoh等[55]提出了如圖11c所示的步驟,在銅UBM上沉積Pd活化層進(jìn)行化學(xué)鍍鎳,然后通過置換反應(yīng)在Ni表層覆蓋Au,以此來保護(hù)Cu UBM,并增加對(duì)焊料的潤(rùn)濕性和可焊性.使用經(jīng)過優(yōu)化的無(wú)氰鍍金浴,能夠化學(xué)鍍Au凸點(diǎn)[58],在進(jìn)行凸點(diǎn)間鍵合時(shí)也可以使用化學(xué)鍍工藝[7].

4芯片互連化學(xué)鍍阻擋層

4.1芯片阻擋層作用及材料

目前, Cu已成為使用最為廣泛的芯片導(dǎo)電互連材料.相比于上一代互連材料Al, Cu在Si或SiO2中遷移率高,在加熱條件下會(huì)向Si或SiO2基材中擴(kuò)散,影響它們的電性質(zhì),因此不論是芯片內(nèi)互連的溝槽、穿孔,還是三維封裝的TSV、凸點(diǎn),都需要阻擋層來防止Cu的擴(kuò)散[50,59].阻擋層與Cu的反應(yīng)程度應(yīng)在一個(gè)合理的范圍內(nèi),以保證擁有優(yōu)秀阻擋性能的同時(shí),還有良好的粘附性[60].傳統(tǒng)的阻擋層材料通常是鈦(Ti)、鉭(Ta)、鎢(W)等高熔點(diǎn)金屬或其合金,并通過PVD、CVD等技術(shù)制備阻擋層.近年來成本更低的化學(xué)鍍Co、Ni等金屬及其合金作為阻擋層得到了積極研究[61].

4.2化學(xué)鍍鎳基阻擋層

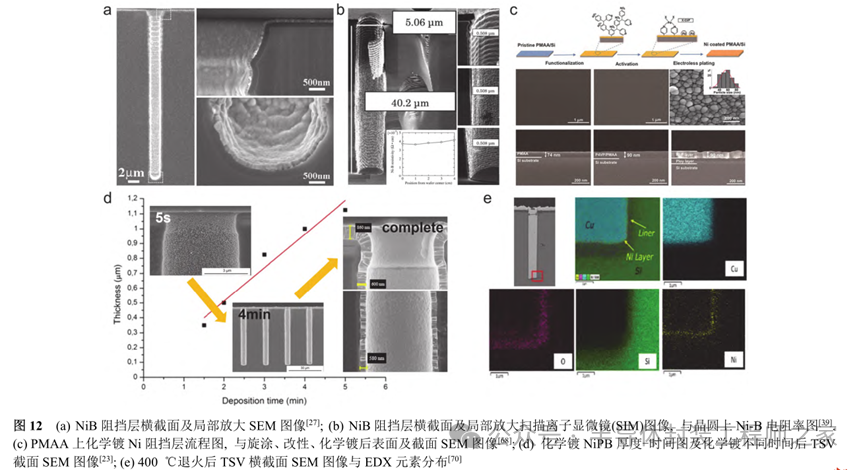

化學(xué)鍍鎳層擁有與基底的結(jié)合力較高、硬度大、耐磨性好等優(yōu)點(diǎn),只需較為廉價(jià)的金屬即可催化沉積的進(jìn)行[62],有利于成本的降低,且因其較好的阻擋性能和較高的電導(dǎo)率,成為芯片互連制程中阻擋層的重要候選材料,得到了研究者們的廣泛關(guān)注[63]. Shingubara與其合作者[27,64-65]使用SAM吸附AuNP或PdNP作為催化劑,在TSV內(nèi)化學(xué)鍍Ni-W-P、NiP和NiB阻擋層.他們制備的NiB阻擋層橫截面SEM圖像如圖12a,電阻率為410μΩ?cm,且能直接作為化學(xué)鍍銅種子層的活化層,但阻擋性能一般,在300℃退火后便已出現(xiàn)Cu的擴(kuò)散.Ikeda等[39]通過氣相沉積APTES形成SAM.氣相沉積可以減少APTES分子聚集,進(jìn)而增加阻擋層的黏附強(qiáng)度.如圖12b所示,他們制得的NiB阻擋層黏附強(qiáng)度為13.07N?cm2,電阻率僅為37~42μΩ?cm,低于傳統(tǒng)Ta或TaN阻擋層,可在400℃退火的條件下阻擋Cu的擴(kuò)散.Zhang等[66]在TSV中使用了特殊的絕緣層,無(wú)需SAM即可直接捕獲Pd離子用于活化,最終得到的化學(xué)鍍NiB阻擋層經(jīng)過500℃退火仍未觀察到Cu的擴(kuò)散.Xiong等[67]提出了一種新型偏心旋涂技術(shù),可大大提高均勻性,并采用該技術(shù)旋涂聚酰亞胺作為絕緣層.在該絕緣層上化學(xué)鍍鎳作為阻擋層,可在400℃下提供阻擋性能. Hu等[68]使用聚合物聚甲基丙烯酸膜(PMAA)作為絕緣層,降低TSV的電容及殘余應(yīng)力.如圖12c所示,通過4-乙烯基吡啶的改性, PMAA能夠吸附Pd離子用于催化化學(xué)鍍NiP阻擋層.對(duì)于116 nm厚的NiP阻擋層,四探針測(cè)定的方阻為26 Ω?sq?1,黏附強(qiáng)度達(dá)到了5B等級(jí),已經(jīng)可用于TSV. Bernasconi等[23]在化學(xué)鍍液中同時(shí)使用DMAB與次磷酸鈉作為還原劑,得到了NiPB阻擋層(圖12d),方阻可低至20 Ω?sq?1. Cai等[69]探究了化學(xué)鍍Ni、Mo、P三元合金的鍍液配方,最終得到的NiMoP阻擋層可在400℃退火后正常發(fā)揮阻擋性能.Lee等[70]制造并評(píng)估了化學(xué)鍍鎳作為阻擋層兼種子層用于高可靠且低成本Cu TSV的效果,相比PVD沉積的阻擋層,化學(xué)鍍鎳阻擋層具有更好的阻擋性能, 400℃下退火后在能量色散X射線光譜(EDX)分析中未觀察到Cu的擴(kuò)散(圖12e).

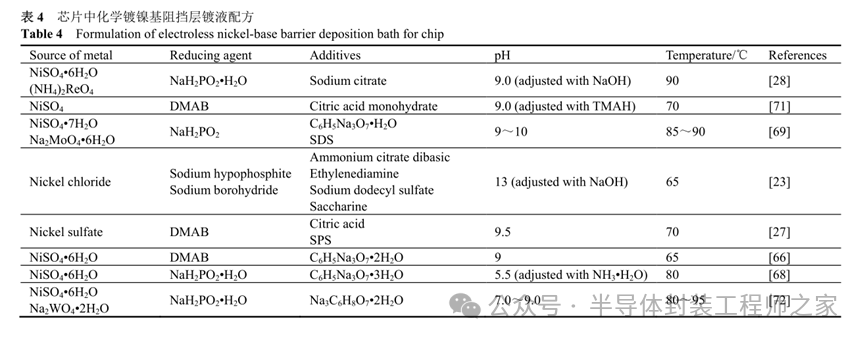

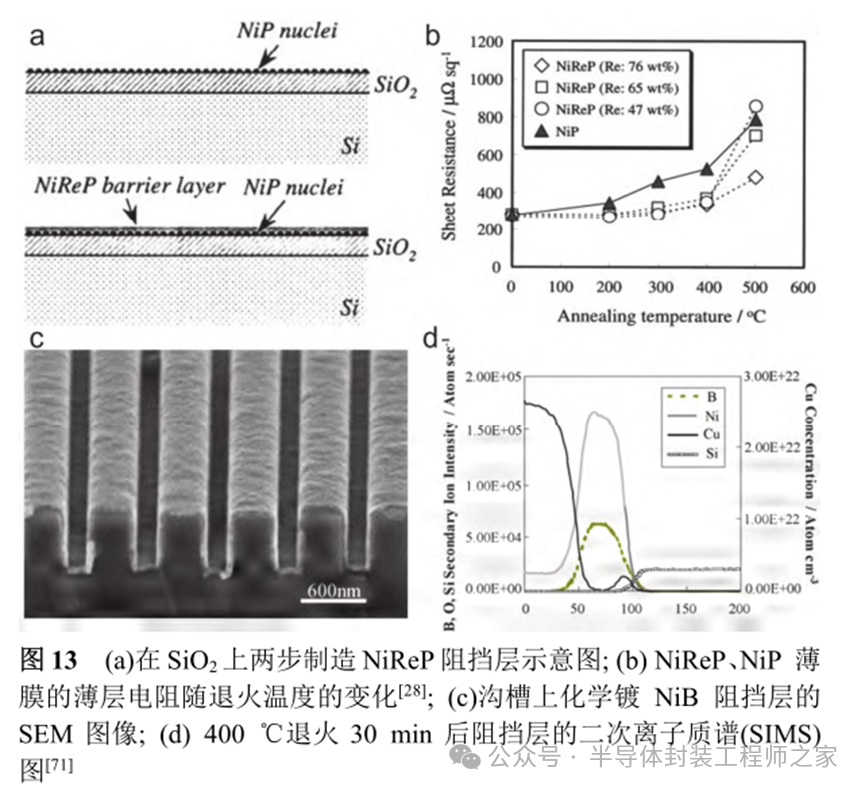

Osaka與其合作者[28,71]為了能夠在堿性條件下化學(xué)鍍芯片內(nèi)互連NiReP阻擋層,先化學(xué)沉積了一層NiP用于保護(hù)SAM免受堿性溶液的危害,此后再沉積NiReP阻擋層(圖13a).在400℃退火后, NiReP/Cu界面區(qū)域仍然完好無(wú)損,阻擋層電阻隨退火溫度變化如圖13b所示.因?yàn)殁c與鉀離子會(huì)影響到金屬氧化物硅晶體管,他們進(jìn)一步探究了無(wú)堿金屬的鍍液,使用氫氧化四甲基銨(TMAH)代替NaOH或KOH作為pH調(diào)節(jié)劑.通過SAM吸附Pd離子進(jìn)行活化,在優(yōu)化后的鍍液中成功化學(xué)鍍NiB阻擋層.與含鈉離子的化學(xué)鍍液相比,使用無(wú)鈉溶液沉積的NiB膜表面更光滑,膜厚更均勻(圖13c).經(jīng)過剖面分析(圖13d), 400℃退火后并未發(fā)現(xiàn)Cu的擴(kuò)散.傳統(tǒng)的化學(xué)鍍NiP UBM阻擋層不足以長(zhǎng)期保護(hù)底層金屬化層免受熔融焊料的侵蝕, Chen等[72]對(duì)鍍液進(jìn)行改良,添加了鎢酸鈉作為鎢源.結(jié)果表明具有較高W含量的NiWP阻擋層的使用壽命比普通NiP層長(zhǎng)得多.表4列舉了芯片中化學(xué)鍍鎳基阻擋層鍍液配方.

4.3化學(xué)鍍鈷基阻擋層

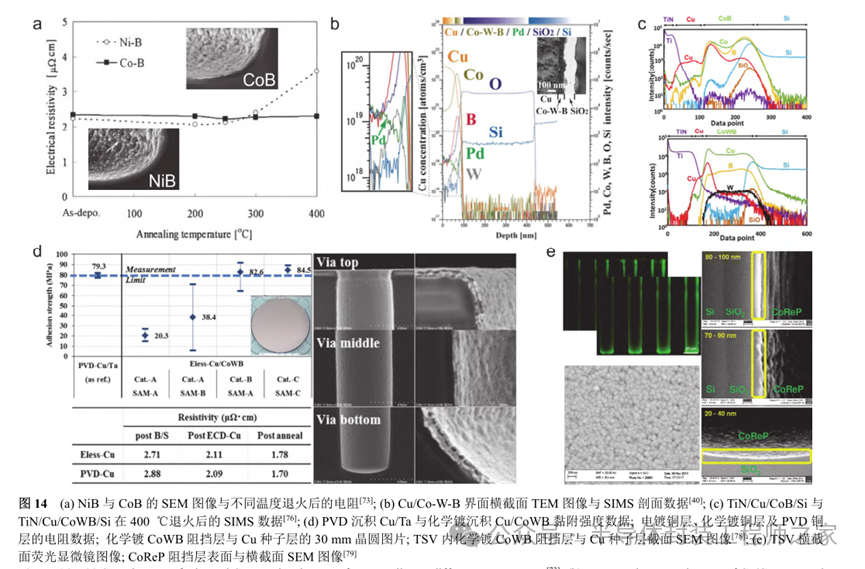

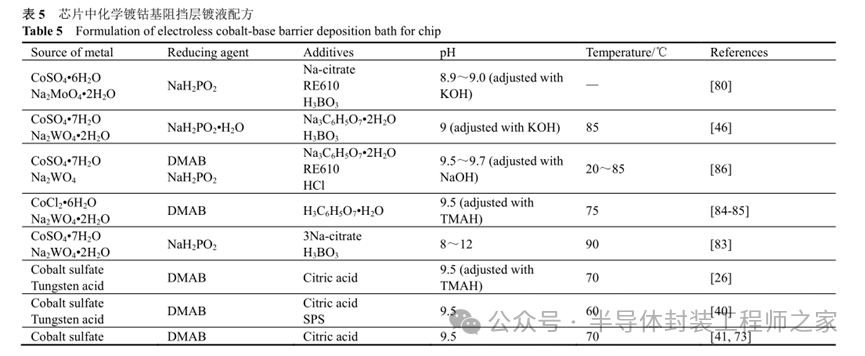

Shingubara與其合作者[41,73]在TSV內(nèi)化學(xué)鍍制備了NiB與CoB阻擋層.通過分析不同阻擋層上銅種子層退火后的電阻變化(圖14a),他們認(rèn)為CoB具有更優(yōu)的熱穩(wěn)定性.在300℃退火后, CoB黏附強(qiáng)度為51.3 MPa.Inoue等[26,40,53-54,74]使用SAM吸附納米顆粒作為催化劑,鍍液中添加鎢酸作為鎢源,在TSV內(nèi)化學(xué)鍍制備了Co的三元合金CoWB阻擋層.表5列舉了芯片中化學(xué)鍍鈷基阻擋層鍍液配方.如圖14b所示,在300℃退火30min后未觀察到Cu的擴(kuò)散.通過控制退火溫度, 60 nm厚的CoWB阻擋層黏附強(qiáng)度高達(dá)70.2 MPa, 40 nm厚的可超過80 MPa. Arima等[75]發(fā)現(xiàn)在鍍液中添加SPS可使CoWB在TSV內(nèi)沉積得更加均勻. Iseri與Matsudaira等[76-77]在上述基礎(chǔ)上進(jìn)一步研究后認(rèn)為Co的三元合金CoWB具有比CoB更好的擴(kuò)散阻擋性能(圖14c).當(dāng)化學(xué)鍍CoWB阻擋層的W質(zhì)量分?jǐn)?shù)大于15%時(shí),在350℃退火后仍可保證阻擋性能;當(dāng)W質(zhì)量分?jǐn)?shù)大于20%, 400℃退火后阻擋層仍具有優(yōu)異的抑制Cu擴(kuò)散的效果. Tanaka等[78]使用化學(xué)鍍工藝在TSV內(nèi)沉積了CoWB阻擋層和Cu種子層, 420℃退火后也未發(fā)生Cu的擴(kuò)散.如圖14d,他們對(duì)比了化學(xué)鍍工藝與PVD工藝制備阻擋層與種子層,化學(xué)鍍CoWB的臺(tái)階覆蓋率可達(dá)85%以上,優(yōu)于PVD制備的Ta阻擋層與Cu種子層,化學(xué)鍍CoWB對(duì)化學(xué)鍍銅種子層的粘附強(qiáng)度與PVD-Ta對(duì)化學(xué)鍍銅相當(dāng),在電鍍填充銅之后也未觀察到空隙或接縫.經(jīng)過粗略的成本計(jì)算,他們認(rèn)為通過對(duì)鍍液進(jìn)行合理的回收利用,化學(xué)鍍工藝的成本對(duì)比PVD可降低40%至50%. Sandjaja等[79]開發(fā)了一種基于熒光的TSV內(nèi)官能團(tuán)可視化技術(shù)用于表征SAM.他們利用此技術(shù)使Pd催化劑在TSV內(nèi)的高密度吸附,實(shí)現(xiàn)了化學(xué)鍍均勻CoReP阻擋層(圖14e).

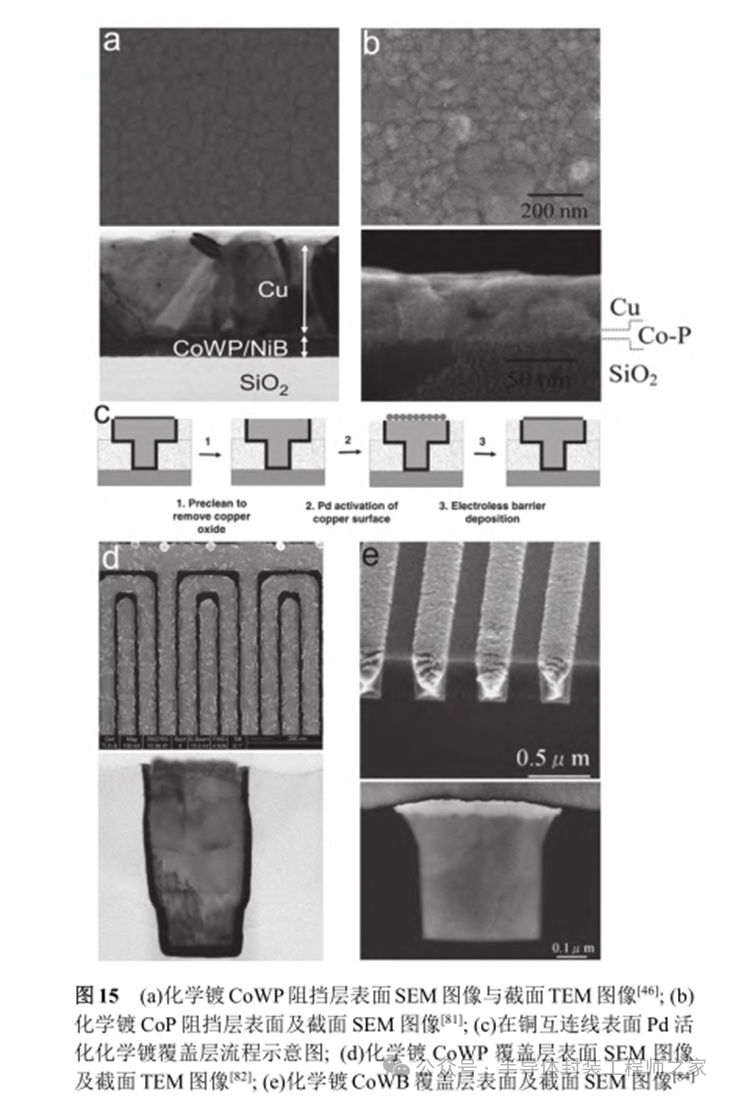

Shacham-Diamand與其合作者[24,46,80]最初選擇在Co二元合金中添加鉬形成化學(xué)鍍CoMoP三元合金用于改善其作為芯片內(nèi)互連阻擋層的性能,可承受350℃退火.后續(xù)更換為CoWP三元合金(圖15a),在500℃退火后未觀察到Cu的擴(kuò)散.兩種Co合金在200℃退火后均可降低電阻.此外,他們認(rèn)為活化時(shí)使用不同的SAM可能會(huì)影響化學(xué)鍍CoWP阻擋層的性質(zhì).不同的SAM對(duì)阻擋層成核、生長(zhǎng)過程中形態(tài)演變有不同程度的影響,最終將導(dǎo)致孵化時(shí)間、覆蓋率及電氣性能的不同.隨著芯片制程的縮小,對(duì)阻擋層厚度提出了更高的要求,為了化學(xué)鍍超薄Co阻擋層, Chen等[81]在使用SC-1對(duì)基底表面進(jìn)行處理后,增加了等離子體處理的步驟,使Co離子可高密度地吸附在表面,進(jìn)而獲得了8 nm的超薄CoP阻擋層(圖15b),能夠在至少550℃的溫度下保持整個(gè)金屬化層的完整性.

覆蓋阻擋層對(duì)于芯片內(nèi)互連也很重要,用于防止下層的銅擴(kuò)散至上層的介電材料中.根據(jù)對(duì)活化的需求,化學(xué)鍍覆蓋阻擋層可分為兩大類,需要額外催化劑活化和無(wú)需額外催化劑活化.需要額外催化劑的化學(xué)鍍覆蓋層流程如圖15c所示, Decorps等[82]使用酸性溶液去除65 nm節(jié)點(diǎn)銅互連導(dǎo)線表面的氧化層,并通過噴霧方式用Pd活化銅表面,最后浸泡在鍍液中得到12 nm厚CoWP覆蓋層(圖15d). Pd催化劑可能會(huì)導(dǎo)致電阻的上升并成為器件雜質(zhì),因此研究者們也在關(guān)注無(wú)額外催化劑化學(xué)鍍覆蓋層.次磷酸鈉作為還原劑時(shí),銅并不能催化Co離子的還原. Aal等[83]將鐵線或鋁線浸入鍍液發(fā)生置換反應(yīng),用于啟動(dòng)化學(xué)鍍.使用DMAB作為還原劑,可直接在銅的催化下還原Co離子. Itabashi與其合作者[84-85]借助DMAB實(shí)現(xiàn)了在銅互連導(dǎo)線表面自對(duì)準(zhǔn)化學(xué)鍍CoWB覆蓋層(圖15e). Almog等[86]將次磷酸鈉與DMAB聯(lián)用,做到了自對(duì)準(zhǔn)化學(xué)鍍CoWPB四元合金覆蓋層,能夠在550℃下阻擋Cu的擴(kuò)散,且電阻僅為1.8Ω?sq?1.

根據(jù)擴(kuò)散阻擋機(jī)理,擴(kuò)散阻擋層分為犧牲型、填充型、被動(dòng)復(fù)合型和非晶型. Pan與Hsieh[87-88]使用敏化-活化法化學(xué)鍍CoWP作為UBM阻擋層,并用固態(tài)時(shí)效與液態(tài)時(shí)效老化探究它們?cè)诿鎸?duì)不同焊料時(shí)的擴(kuò)散阻擋特性.α-CoWP在作為SnAgCu焊料的阻擋層時(shí),會(huì)提供犧牲型、填充型和非晶型的阻擋機(jī)理; poly-CoWP能提供犧牲型和填充型.在面對(duì)SnBi焊料時(shí),無(wú)定形CoWP能作為犧牲型及填充型阻擋層,多晶CoWP表現(xiàn)為犧牲型.

5芯片互連化學(xué)鍍銅種子層

阻擋層電阻一般較大,這對(duì)于芯片內(nèi)及TSV內(nèi)傳統(tǒng)電鍍填充銅互連材料的工藝是不利的.比如,在使用大馬士革工藝電鍍填充銅時(shí),對(duì)于大尺寸的晶圓,阻擋層過大的電阻會(huì)使電鍍接觸點(diǎn)(通常為邊緣)到晶圓中心出現(xiàn)IR壓降,導(dǎo)致銅沉積不均勻,因此必須在填充銅之前覆蓋一層導(dǎo)電的銅種子層.通常采用PVD或CVD的方式制備銅種子層,但正如前述,這兩種工藝不僅成本高,而且可能出現(xiàn)“倒垂”現(xiàn)象,導(dǎo)致后續(xù)電鍍銅填充的失敗[50].化學(xué)鍍優(yōu)秀的保形能力及低成本引起了研究人員的關(guān)注.

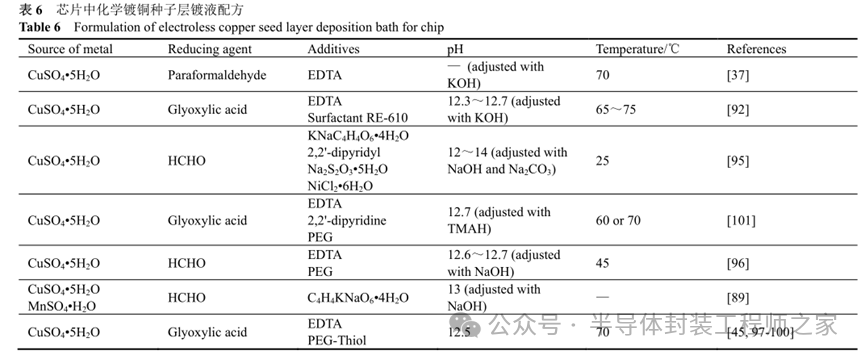

5.1芯片化學(xué)鍍銅鍍液組成及作用

表6列舉了常見的銅種子層鍍液配方.鍍液中通常使用硫酸銅作為銅源,乙二胺四乙酸(EDTA)與酒石酸鉀鈉則被廣泛地用作絡(luò)合劑,可防止銅離子在堿性條件下沉淀[37,89-90].除絡(luò)合劑外,研究者們還會(huì)加入一些添加劑改善鍍銅質(zhì)量[91].例如加入表面活性劑可以增加鍍液的潤(rùn)濕能力,有利于氫氣的排出[92-93]; 5,5-二甲基乙內(nèi)酰脲可避免鍍液中產(chǎn)生銅與氧化亞銅的微小顆粒[94];硫代硫酸鈉可增強(qiáng)鍍液穩(wěn)定性[95]; PEG可以控制鍍銅速率[96]; Inoue等[45,97-100]在鍍液中添加PEG-硫醇體系使銅種子層在大縱橫比的TSV內(nèi)均勻沉積,他們還發(fā)現(xiàn)2,2'-聯(lián)吡啶添加劑能夠發(fā)揮穩(wěn)定劑及光亮劑的作用,可提升沉積的銅膜純度,降低粗糙度.

化學(xué)鍍液大多使用甲醛作為還原劑,但甲醛作為1類致癌物,對(duì)人們的身體健康有重大威脅,為此研究者們開發(fā)了其他一些還原劑作為替代品.在銅種子層鍍液中,乙醛酸得到了廣泛研究.早在1999年, Shacham‐Diamand等[92]就將乙醛酸用于化學(xué)鍍芯片內(nèi)互連銅種子層.但當(dāng)時(shí)的工藝并不成熟, Shacham‐Diamand認(rèn)為此方案只適用于修補(bǔ)PVD沉積的銅種子層. 2003年Wang等[101]配制的乙醛酸鍍液便已可以在TaN或WN阻擋層上沉積銅種子層. Inoue等[97,99]以乙醛酸為還原劑繼續(xù)研究鍍液配方,探究了EDTA、2,2'-聯(lián)吡啶等添加劑的作用.化學(xué)鍍銅液需要在堿性下工作,由于堿金屬離子對(duì)芯片器件不友好,研究者們也開發(fā)了TMAH作為NaOH、KOH等pH調(diào)節(jié)劑的替代品[101].

5.2化學(xué)鍍芯片內(nèi)銅種子層

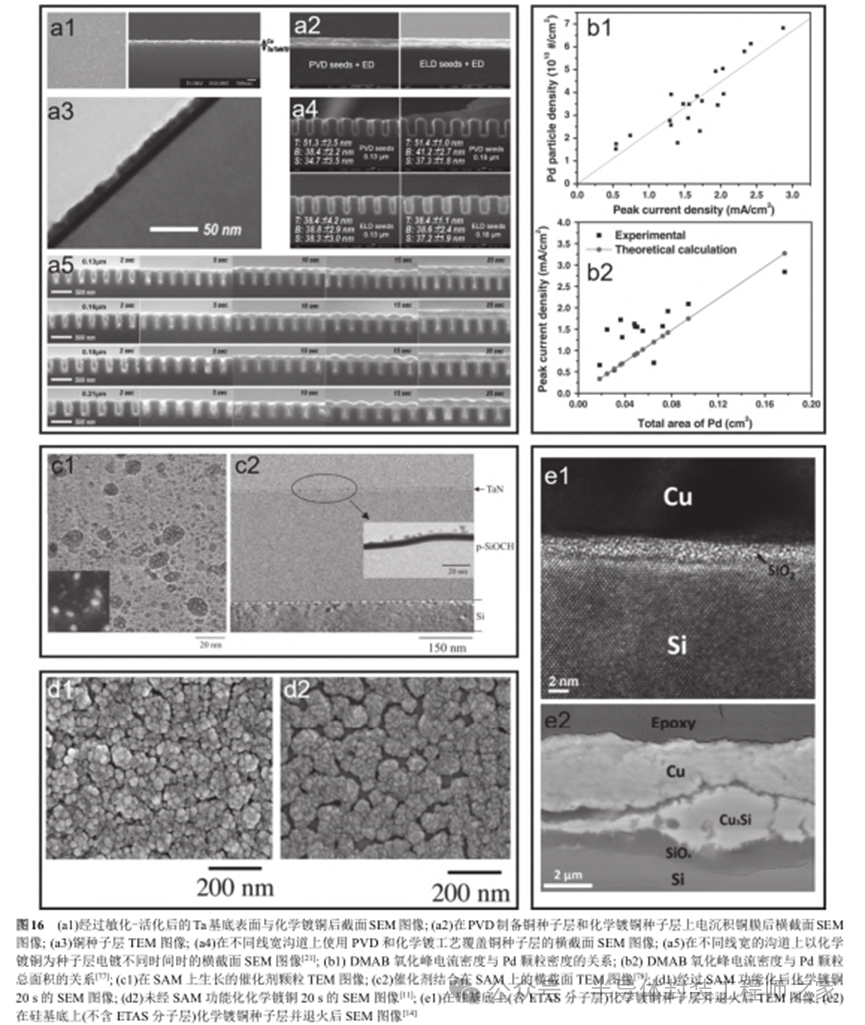

化學(xué)鍍銅種子層既可選用活化工藝,也可以通過置換法引發(fā)化學(xué)鍍. Wang等[101]用濕法刻蝕去除了TaN或WN阻擋層表面的氧化物,在乙醛酸為還原劑的鍍液中,TaN或WN的氧化還原電位低于Cu的氧化還原電位,因此可置換出銅,從而驅(qū)動(dòng)無(wú)需活化的化學(xué)鍍銅種子層.退火后鍍層黏附強(qiáng)度可達(dá)0.11 kgf/cm,足以支持CMP.但應(yīng)用更為廣泛的還是活化鍍銅的制備方式. Lee等[37]使用敏化-活化法制備了銅種子層.經(jīng)過對(duì)比,化學(xué)鍍方式制備的銅種子層無(wú)論是側(cè)壁還是底部臺(tái)階的覆蓋率都要優(yōu)于PVD制備的銅種子層(圖16a). Lim等[102]利用Pd存在時(shí)DMAB的氧化電流,引入了一種電化學(xué)監(jiān)測(cè)方法,用于表征敏化-活化后阻擋層表面吸附的Pd納米顆粒數(shù)量與面積(圖16b),并以此優(yōu)化催化過程.

除敏化-活化法,使用SAM捕獲催化劑離子并活化也是常見手段. Chen與其合作者[22,103]經(jīng)過對(duì)比發(fā)現(xiàn),在Ta、TaN阻擋層上使用OTS-SAM吸附Ni離子、Pd離子并 還 原 得 到 的 納 米 顆 粒 尺 寸 要 遠(yuǎn) 小 于 直 接 通 過Ta-OH基團(tuán)吸附并還原的(圖16c),且吸附密度提高了至少一個(gè)數(shù)量級(jí),能夠沉積更好的鍍層(圖16d). Wu等[25]使用ETAS在SiO2/Si襯底上制備SAM,用于吸附Pd納米顆粒活化基底.退火后, ETAS分子層表現(xiàn)出了很強(qiáng)的束縛能力,黏附強(qiáng)度可達(dá)5.6 MPa.此外,通過對(duì)比有無(wú)SAM的鍍銅后橫截面圖像(圖16e),發(fā)現(xiàn)ETAS分子層很可能發(fā)揮著阻擋層的作用. Yu等[89,104]使用Ru層作為活化層,化學(xué)鍍Cu-Mn種子層, Mn會(huì)以氧化物或氫氧化物的形式沉積.經(jīng)過退火, Mn會(huì)在Cu-基底界面處偏析,從而形成阻擋層.他們還利用在Cu與Ru上欠電位沉積鉛的起始電位差異,獲得了Cu種子層在Ru上的覆蓋數(shù)據(jù),研究了Cu種子層的生長(zhǎng)模式.

5.3化學(xué)鍍TSV銅種子層

在Ta/TaN和Ti/TiN阻擋層上沉積金屬銅較為困難,而Ru、W、Co等金屬雖然對(duì)于沉積工藝較為友好,但它們 的 阻 擋 效 率 可 能 不 如Ta/TaN和Ti/TiN. Inoue等[45,97-99,105-106]認(rèn)為,使用原子層沉積或化學(xué)氣相沉積將Ru、W、Co等金屬沉積至Ta/TaN、Ti/TiN等良好的阻擋層上,則可以結(jié)合兩者的優(yōu)勢(shì).他們使用ALD在TiN阻擋層上分別沉積了Ru、W層,使用CVD在TiN阻擋層上沉積了Co層,并實(shí)現(xiàn)了在TSV阻擋層上無(wú)催化劑化學(xué)鍍銅種子層,但它們的原理并不相同. W會(huì)與鍍液中的銅離子發(fā)生置換反應(yīng),使Cu在W層表面析出,自催化化學(xué)鍍.但是該方式化學(xué)鍍的銅種子層與W層黏附強(qiáng)度很低,這可能是因?yàn)橹脫Q反應(yīng)發(fā)生時(shí)還會(huì)生成W的氧化物種,殘留在Cu與W的界面處,導(dǎo)致黏附強(qiáng)度的下降. Co同樣會(huì)與銅離子發(fā)生置換反應(yīng)從而使化學(xué)鍍銅進(jìn)行,但置換反應(yīng)對(duì)Co層的腐蝕對(duì)于制作工藝是不利的.在化學(xué)鍍初期,置換反應(yīng)與沉積反應(yīng)是競(jìng)爭(zhēng)關(guān)系,可以通過調(diào)整鍍液中EDTA與銅離子的濃度使化學(xué)鍍銅種子層的過程中Co的置換反應(yīng)達(dá)到最少,使用該方案化學(xué)鍍銅種子層的TEM圖像如圖17a所示.而Ru層對(duì)化學(xué)鍍銅種子層起的是催化作用,沒有氧化物種的生成,所以黏附強(qiáng)度較高.使用乙醛酸作為鍍液的還原劑可以縮短化學(xué)鍍銅時(shí)Cu核在Ru層表面生成的時(shí)間,2,2'-聯(lián)吡啶的加入可以獲得更光滑、純度更高的銅種子層.該技術(shù)可在3μm×50μm的TSV內(nèi)化學(xué)鍍銅種子層(圖17b),并應(yīng)用于30 mm的晶圓上.無(wú)獨(dú)有偶, Seo等[96]同樣使用Ru層作為催化層化學(xué)鍍銅種子層.但不同的是,他們?cè)赥a阻擋層上使用化學(xué)鍍的方式沉積Ru層,相比于ALD方法設(shè)備成本更低,實(shí)現(xiàn)了沉積Ru層到電鍍銅填充TSV的全濕工藝(圖17c). Ho等[107]為嵌入式晶圓級(jí)封裝開發(fā)了模內(nèi)通孔互連,使用化學(xué)鍍方式沉積銅種子層.

Inoue等[100]在鍍液中添加PEG-硫醇添加劑,在縱橫比高達(dá)10的TSV中成功制備了共形的銅種子層.Zhang等[108]在化學(xué)鍍銅種子層前引入Cu濺射,增強(qiáng)了種子層的連續(xù)性. Xiao等[109]提出脈沖超聲輔助化學(xué)鍍方法,成功在580μm深的TSV中沉積了連續(xù)且致密的銅種子層.

5.4芯片封裝載板化學(xué)鍍種子層

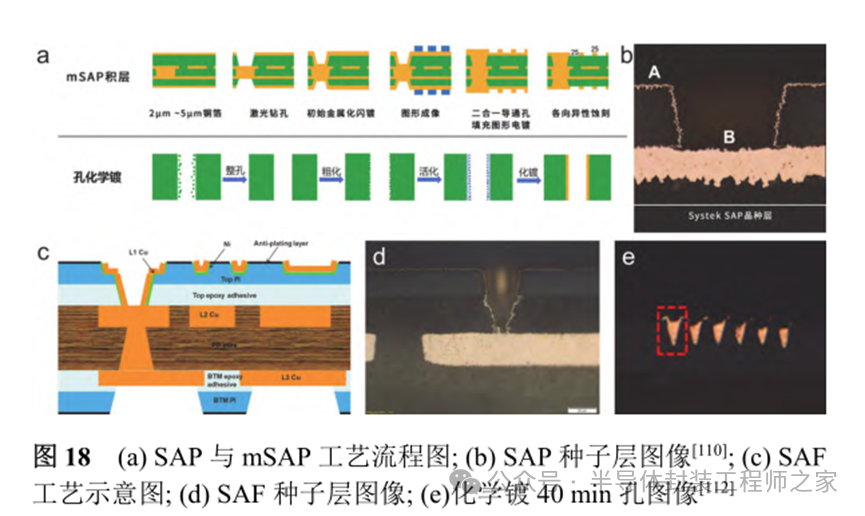

在目前的大規(guī)模生產(chǎn)制造中,芯片封裝載板和印制電路板(PCB)的孔金屬化種子層主要是通過化學(xué)鍍銅來實(shí)現(xiàn).芯片封裝載板通常使用半加成工藝(SAP)或改良半加成工藝(mSAP)制造(圖18a).在鉆孔之后,需要使用化學(xué)鍍銅技術(shù)在積層裸材表面覆蓋一層銅種子層(圖18b),以便后續(xù)的電鍍填充圖形[110].芯片封裝載板的化學(xué)鍍工藝已較為成熟,商業(yè)上通常選用化學(xué)鍍含鎳的銅膜來提高沉積速率和黏附強(qiáng)度.但是含鎳的銅膜不容易被刻蝕,這可能影響精細(xì)圖案的設(shè)計(jì)制造. Hakiri等[111]使用新開發(fā)的不含鎳鍍液鍍銅,獲得了優(yōu)異的黏附強(qiáng)度和保形能力. Chao等[112]開發(fā)了一種選擇性全加成工藝(SFA)用于替代SAP.如圖18c所示, SFA采用了抗鍍層以實(shí)現(xiàn)選擇性化學(xué)鍍,在化學(xué)鍍銅時(shí)間達(dá)到40 min時(shí)可填上3μm線寬的溝槽(圖18d、18e).與SAP相比, SFA可以摒棄CMP等步驟,其更少的流程步驟顯著降低了總體成本. Beyer等[113]開發(fā)了膠體銅活化劑取代鈀基活化劑,可降低SAP工藝中化學(xué)鍍成本.后續(xù)的測(cè)試結(jié)果也表明其覆蓋率、沉積速率、黏附強(qiáng)度和電氣可靠性性能與鈀基活化劑相當(dāng).

6芯片互連化學(xué)鍍孔填充

雙大馬士革工藝以及TSV填充工藝中,由于阻擋層電阻較大,想要進(jìn)行電鍍填充Cu必須要有種子層的存在.而化學(xué)鍍能夠在不導(dǎo)電基材上鍍銅的特性可以減少工序、降低成本,化學(xué)鍍直接進(jìn)行孔填充實(shí)現(xiàn)互連的研究得到關(guān)注.

6.1超填孔互連化學(xué)鍍添加劑及機(jī)理

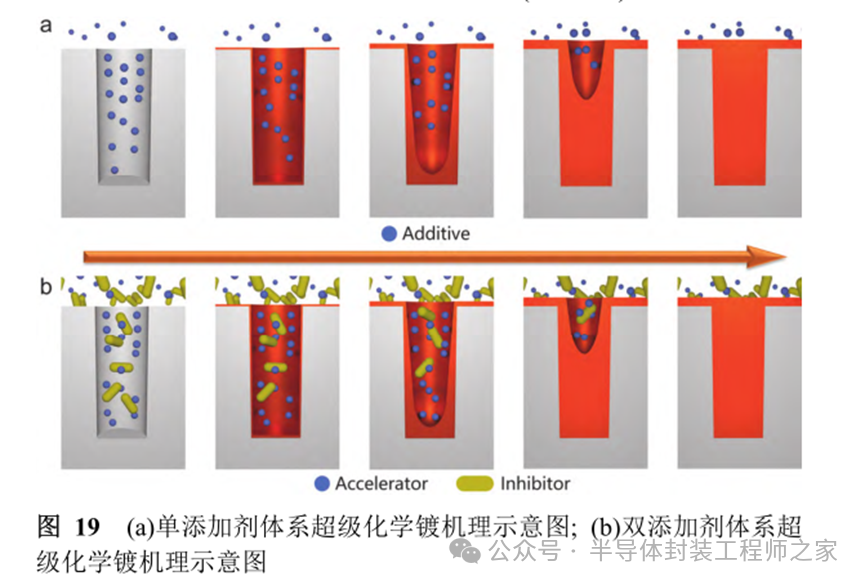

在傳統(tǒng)的電鍍填孔中,由于孔口位置銅離子濃度高,想要對(duì)溝槽、過孔和TSV進(jìn)行自下而上的超級(jí)填充,添加劑必不可少[114].超級(jí)化學(xué)鍍孔填充與電鍍孔填充相似,同樣需要添加劑的輔助,添加劑體系可分為單添加劑體系與雙添加劑體系[115].常見的添加劑體系有SPS、PEG、巰基烷基羧酸(MACA)、三嵌段共聚物、3-N,N-二甲氨基二硫代氨基甲酰基-1-丙磺酸(DPS)和2-巰基-5-苯并咪唑磺酸(MBIS)等. 2004年, Shingubara與其合作者[116-117]使用SPS單添加劑首次實(shí)現(xiàn)了超級(jí)化學(xué)鍍孔填充,并探究其中機(jī)理.如圖19a所示,他們認(rèn)為SPS吸附在沉積的銅膜表面時(shí)降低了Cu自催化沉積的活性面積,從而降低Cu的沉積速率.在Cu沉積過程中,SPS會(huì)被消耗(結(jié)合到銅膜內(nèi)),溝槽及過孔頂部的SPS會(huì)及時(shí)補(bǔ)充,繼續(xù)抑制沉積速率,而中部及底部由于擴(kuò)散的影響,消耗掉的SPS無(wú)法被及時(shí)補(bǔ)充,形成了濃度梯度,因此沉積速率也形成梯度,從而實(shí)現(xiàn)了自下而上的化學(xué)鍍銅沉積.楊等[118-119]探究了不同濃度、不同分子量PEG以及相同分子量PEG、聚丙二醇和三嵌段共聚物EPE對(duì)超級(jí)化學(xué)鍍的影響.結(jié)果表明PEG濃度與分子量越大,對(duì)化學(xué)鍍銅沉積速率的抑制越明顯,在相同分子量的情況下則是EPE對(duì)化學(xué)鍍銅的抑制作用最強(qiáng).此外, MACA[120]、三 嵌 段 共 聚 物EPE-8000[121]和PEP-3100[122]均使用抑制機(jī)理實(shí)現(xiàn)了超級(jí)化學(xué)鍍孔填充.Lee等[123]使用石英晶體微天平、混合電位分析等方法也對(duì)SPS添加劑的機(jī)理進(jìn)行了探究,認(rèn)為SPS并不是一直表現(xiàn)出抑制作用,在低濃度時(shí)SPS起到了加速沉積的效果.此外, DPS[124]與MBIS[125]也具有低濃度時(shí)加速沉積、高濃度時(shí)抑制沉積的特性,均可用于超級(jí)化學(xué)鍍填孔.

雙添加劑體系通常包含加速劑與抑制劑.研究者們開發(fā)的抑制劑-加速劑體系有:聚乙二醇與8-羥基-7-碘-5-喹啉磺酸(PEG-HIQSA)體系[126]、聚乙二醇與聚二硫二丙烷磺酸鈉(PEG-SPS)體系[127-128]、聚醚與2-巰基苯并噻唑(PE-3650-2-MBT)體系[129]和三嵌段共聚物與健那綠B(PEP-3100-JGB和RPE-2520-JGB)體系[130-131].雙添加劑體系通常有三個(gè)特性:一是加速劑的分子一般較小,擴(kuò)散速度快;抑制劑的分子量一般比加速劑大,擴(kuò)散速度慢.二是僅加速劑存在時(shí)沉積速率會(huì)被加快;僅抑制劑存在時(shí)沉積速率會(huì)被減慢.三是加速劑與抑制劑同時(shí)存在時(shí),沉積速率會(huì)被更強(qiáng)烈地抑制.綜上所述,雙添加劑體系實(shí)現(xiàn)超級(jí)化學(xué)鍍孔填充的機(jī)理為:抑制劑擴(kuò)散速度慢,在需要填充的孔內(nèi)會(huì)形成濃度梯度,頂部濃度高,底部濃度低.加速劑因?yàn)榉肿恿枯^小,可視為不存在濃度梯度.在底部加速劑能夠加快沉積速率,而中部與頂部由于抑制劑濃度的增大,沉積逐漸被抑制,從而實(shí)現(xiàn)了自下而上的超級(jí)化學(xué)鍍填孔(圖19b).

6.2芯片內(nèi)互連化學(xué)鍍填孔

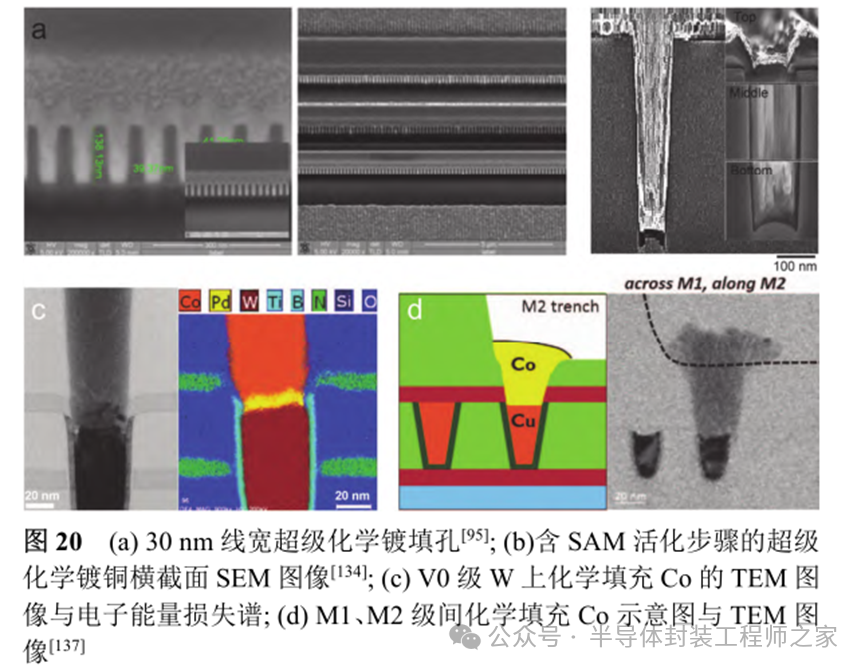

早些年,研究者們對(duì)于超級(jí)化學(xué)鍍填孔的研究重點(diǎn)在于添加劑. Shingubara與其合作者[42,116-117]開發(fā)了SPS與PEG-SPS體系在超級(jí)化學(xué)鍍填孔中的應(yīng)用; Hasegawa等[126]使用HIQSA替代SPS; Wang與其合作者[121-122,129]開發(fā)了三嵌段共聚物作為抑制劑; Lee等[124-125,132]開發(fā)了MBIS、DPS等添加劑,并使用2,2'-聯(lián)吡啶提高沉積的銅質(zhì)量,避免退火后產(chǎn)生空隙; Wang等[130-131]則更加關(guān)注以JGB為加速劑的體系,開發(fā)三嵌段共聚物作為抑制劑. Lee等探究了鍍液中添加劑和鍍銅條件的影響,在優(yōu)化后實(shí)現(xiàn)了30 nm線寬溝槽的填孔(圖20a).后續(xù)研究者們的關(guān)注點(diǎn)轉(zhuǎn)向了工藝優(yōu)化及超級(jí)化學(xué)鍍填充Co的可能性. Lim等[43]采用聲化學(xué)法,利用超聲將Pd納米顆粒均勻地還原在Ta阻擋層上,并實(shí)現(xiàn)了溝槽內(nèi)的超級(jí)化學(xué)鍍銅填孔.隨著工藝制程(線寬)的縮小,芯片內(nèi)銅互連線的電阻上升,將會(huì)對(duì)芯片性能造成影響. Chen等[30,133-134]認(rèn)為應(yīng)該縮小阻擋層厚度,為最大限度增加銅線寬留出空間.他們給出的解決方案是用于捕獲金屬離子的SAM兼作阻擋層.經(jīng)過實(shí)驗(yàn),他們發(fā)現(xiàn)脂肪族NH2-SAM、APTMS-SAM和MPTMS-SAM都可以發(fā)揮阻擋層的作用,且成功利用它們捕獲金屬離子并還原,催化超級(jí)化學(xué)鍍填孔(圖20b).這將簡(jiǎn)化工藝,降低填充Cu的電阻.研究者們提出的另一種解決方案為使用Co代替Cu作為互連線材料[135],因?yàn)樵诰€寬很小時(shí),不需阻擋層的Co互連線比需阻擋層的Cu互連線總電阻更低[136]. Veen等[137]提出并實(shí)現(xiàn)了BEOL中過孔的Co超級(jí)化學(xué)鍍填充.在W基底上使用Pd催化化學(xué)鍍鈷;在填充Cu的溝槽上可以無(wú)需催化劑直接化學(xué)鍍鈷(圖20c、20d).無(wú)獨(dú)有偶, Yu等[138]在28 nm技術(shù)節(jié)點(diǎn)實(shí)現(xiàn)了超級(jí)化學(xué)鍍鈷填充BEOL過孔,且電遷移失效分析表明其壽命要長(zhǎng)于Cu.

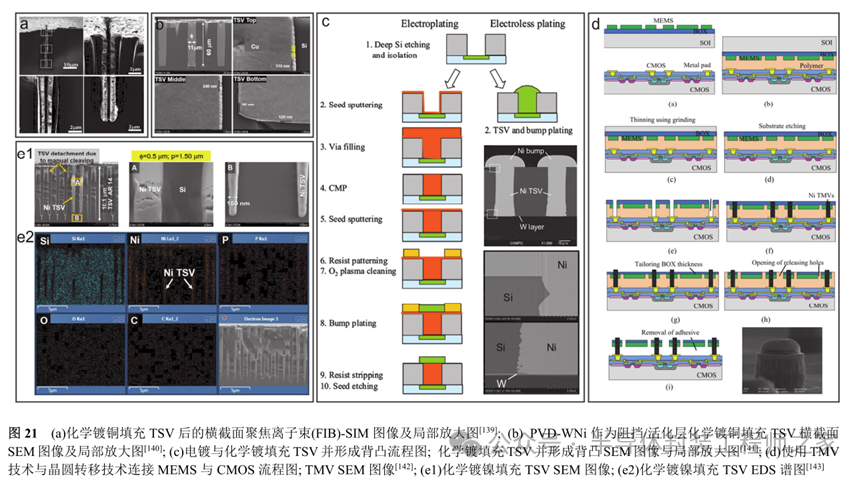

在面對(duì)孔徑與深度都遠(yuǎn)大于芯片內(nèi)互連的三維封裝TSV時(shí),化學(xué)鍍填充TSV更為困難,但隨著3D封裝互連線寬的不斷變小,化學(xué)鍍填充TSV也變得更具可行性. Inoue等[53,139]在覆蓋有W層的TSV內(nèi),使用含SPS與氯離子的鍍液成功地在開口為2μm×8μm、縱橫比為18.5的TSV內(nèi)完成了保形化學(xué)鍍銅.但如圖21a所示,初始填充的Cu并沒有完全閉合, TSV中心仍有一條空隙存在.后續(xù)經(jīng)過二次鍍銅,成功地填充了該TSV.Mariappan等[140]使用PVD在孔徑為11μm、縱橫比為5.5的TSV內(nèi)沉積WNi阻擋層/活化層,并成功地使用化學(xué)鍍銅填充了TSV(圖21b).化學(xué)鍍填充TSV研究得更多的是Ni填充,因?yàn)镹i不需要額外的擴(kuò)散阻擋層.Kawano等[141]開發(fā)了能夠在以W層為底的TSV內(nèi)化學(xué)鍍填充Ni并形成背凸的工藝,在W上使用Pd催化化學(xué)鍍鎳,形成背凸后進(jìn)行化學(xué)鍍鈀浸金.該化學(xué)鍍工藝將電鍍需要的10道工序縮減至2道(圖21c),并使用該工藝制 造 了 堆 疊 式 動(dòng) 態(tài) 隨 機(jī) 存 取 存 儲(chǔ) 器(DRAM). Du等[142]發(fā)現(xiàn),在鍍液中當(dāng)活性金屬與金焊盤接近而不是直接接觸時(shí)也會(huì)發(fā)生化學(xué)鍍鎳,稱為非接觸感應(yīng)化學(xué)鍍鎳.他們將此技術(shù)與晶圓轉(zhuǎn)移技術(shù)相結(jié)合,根據(jù)圖21d流程,制造了微機(jī)電系統(tǒng)通孔(TMV),用于連接CMOS與微機(jī)電系統(tǒng). Murugesan等[143]在12英寸晶圓上制造了孔徑為500 nm、縱橫比20的TSV,并使用改進(jìn)過的化學(xué)鍍鎳工藝進(jìn)行了填充(圖21e).該工藝與CMOS BEOL相兼容,可用于未來制造小孔徑TSV 3D互連.

6.3RDL和凸點(diǎn)鍵合化學(xué)鍍填孔

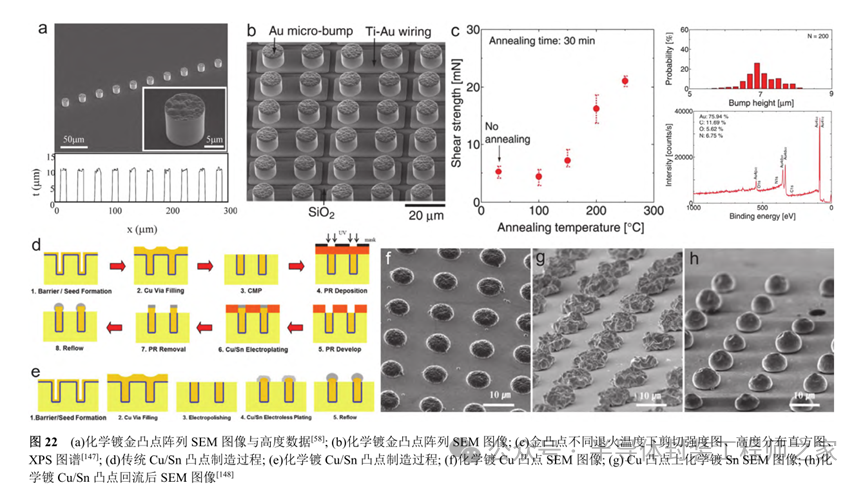

芯片封裝中凸點(diǎn)通常使用電沉積方式制造.但由于電流密度分布不均勻,難以制造小間距的均勻凸點(diǎn).此外,為電沉積提供電流的引線也有可能干擾高速信號(hào)的傳輸.因此,化學(xué)鍍制造凸點(diǎn)也得到了廣泛關(guān)注. Kim等[144-145]探究了化學(xué)鍍鎳形成凸點(diǎn)鍍鎳浴參數(shù)的影響,包括穩(wěn)定劑濃度、溫度、pH值和焊盤尺寸等,并提出了其最佳工藝條件.化學(xué)鍍金體系通常含有氰化物[146],對(duì)環(huán)境不友好, Yokoshima等[58]開發(fā)了一種無(wú)氰鍍金浴,克服了傳統(tǒng)化學(xué)鍍金沉積速率低、凸點(diǎn)高度無(wú)法超過5μm的缺點(diǎn),成功地在Cu線上制造了高度與直徑均為10μm、間距為20μm的Au微凸點(diǎn)陣列(圖22a). Watanabe等[147]在上述工作的基礎(chǔ)上,繼續(xù)對(duì)金凸點(diǎn)進(jìn)行高度測(cè)量、剪切測(cè)試、X射線光電子能譜分析,并在鍵合后進(jìn)行SIM觀察、剪切測(cè)試和四端測(cè)量等(圖22b、22c).最終結(jié)果表明金凸點(diǎn)具有良好的機(jī)械性能和電學(xué)性能.化學(xué)鍍的必要條件是有活性的活化物種, Koo等[148]利用該特性實(shí)現(xiàn)了在填充Cu的TSV上自對(duì)準(zhǔn)化學(xué)鍍Cu/Sn凸點(diǎn),并使用2,2'-聯(lián)吡啶增強(qiáng)銅的選擇性沉積.相比于電鍍制造,化學(xué)鍍工藝有效地降低了總過程成本和時(shí)間(圖22d~22h).

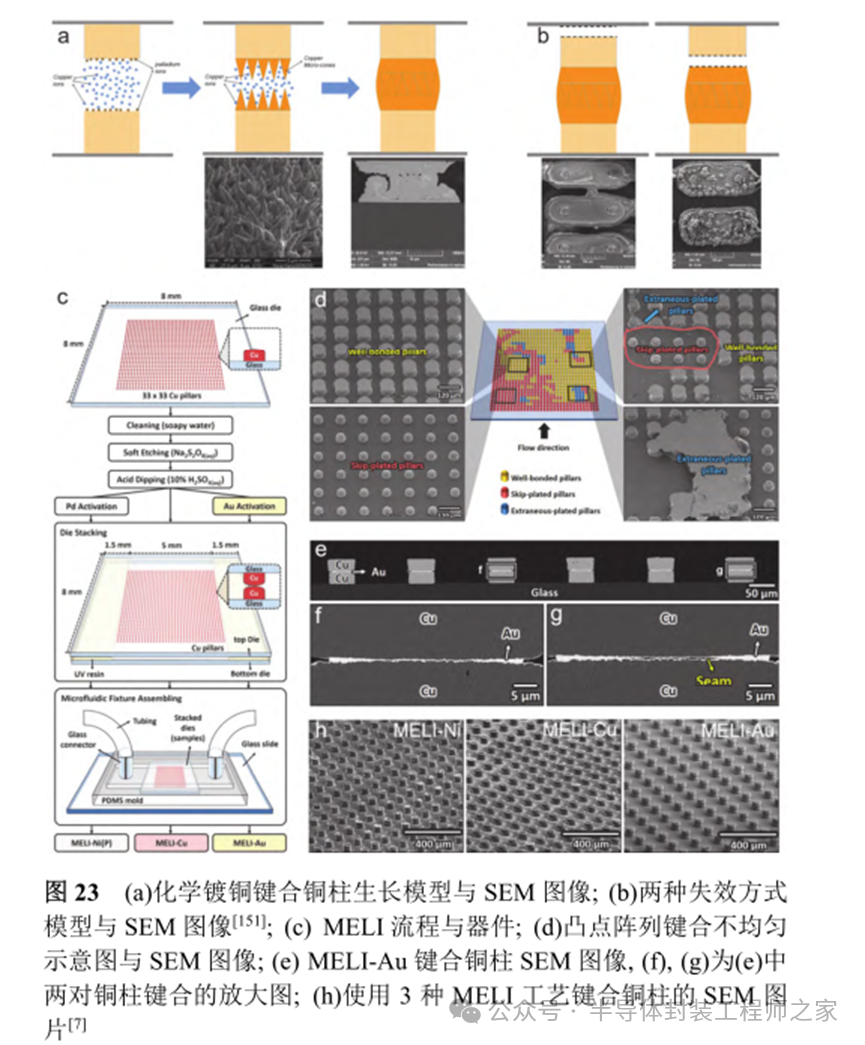

在芯片制程不斷進(jìn)步的今天,基于傳統(tǒng)焊料的凸點(diǎn)互連可能面臨電氣連接、熱穩(wěn)定性和機(jī)械可靠性問題,包括抗電遷移能力差或形成脆性金屬間化合物.與傳統(tǒng)焊接技術(shù)相比,銅柱凸點(diǎn)能夠提供更高的I/O密度以及更低的熱阻、電阻和出色的電遷移電阻[149].目前使用最為廣泛的銅柱鍵合技術(shù)是熱壓,然而其高溫高壓的條件可能會(huì)對(duì)芯片產(chǎn)生不良影響.因此,研究者們探究了條件溫和的化學(xué)鍍工藝在銅柱凸點(diǎn)鍵合上的應(yīng)用. Koo等[150]使用SPS作為添加劑,在兩個(gè)銅柱凸點(diǎn)間形成的縫隙內(nèi)實(shí)現(xiàn)了超級(jí)化學(xué)鍍填孔,成功地將銅柱凸點(diǎn)相連. Chen等[151]通過使用一種結(jié)晶改進(jìn)劑,使銅層的生長(zhǎng)達(dá)到高度各向異性,形成尖銳而快速生長(zhǎng)的微錐,沉積速率可達(dá)15 μm?h?1.如圖23a所示,兩個(gè)銅柱凸點(diǎn)之間相向生長(zhǎng)的微錐最終將會(huì)閉合,使凸點(diǎn)相連.失效分析表明,微錐閉合處黏附強(qiáng)度優(yōu)秀,失效主要發(fā)生在凸點(diǎn)與基底之間的斷裂以及化學(xué)鍍銅連接層與凸點(diǎn)之間的斷裂(圖23b). Kao與其合作者[7,152-154]開發(fā)了微流控化學(xué)鍍互連工藝(MELI). MELI工藝流程與器件如圖23c所示,對(duì)芯片上的銅柱凸點(diǎn)進(jìn)行清洗、刻蝕、活化(可選)之后,將兩個(gè)芯片對(duì)齊,使用UV樹脂使它們能夠堆疊放置.隨后,將堆疊的芯片放置在由聚二甲基硅氧烷(PDMS)和玻璃板組成的微流控夾具中,兩根玻璃管分別作為微流控通道的入口和出口連接到PDMS夾具上.借助MELI,可以通過化學(xué)鍍鎳、化學(xué)鍍銅和化學(xué)鍍金來鍵合銅柱凸點(diǎn).在使用化學(xué)鍍鎳與化學(xué)鍍銅鍵合時(shí),可能產(chǎn)生凸點(diǎn)陣列鍵合不均勻的現(xiàn)象(圖23d),其原因有二:一是原子氫的流動(dòng).原子氫是鍍鎳與鍍銅時(shí)還原反應(yīng)產(chǎn)生的中間體, MELI施加的鍍液流動(dòng)可能會(huì)將原子氫從Ni或Cu表面帶走,導(dǎo)致微流道入口處的凸點(diǎn)跳鍍,出口處凸點(diǎn)過鍍.二是氫氣泡的產(chǎn)生.化學(xué)鍍過程中產(chǎn)生的氫氣泡可能困在需要連接的凸點(diǎn)間,阻擋化學(xué)鍍的進(jìn)行,導(dǎo)致銅柱凸點(diǎn)無(wú)法鍵合.為了解決鍵合不均勻的問題, Hung等[7]采用定期停止流動(dòng)和定期逆流的方式,稱為間歇振蕩流.在使用該方式后,雖然化學(xué)鍍鎳仍會(huì)出現(xiàn)部分過鍍柱,但化學(xué)鍍銅已經(jīng)能均勻鍵合了.間歇振蕩流除可以讓化學(xué)鍍銅與化學(xué)鍍金的方式均勻鍵合外(圖23e~23g),還可以大幅縮短工藝時(shí)間.圖23h展示了使用3種MELI工藝鍵合銅柱的SEM圖片.Zhang等[155]對(duì)MELI工藝進(jìn)行建模計(jì)算與實(shí)際實(shí)驗(yàn)驗(yàn)證.結(jié)果表明該技術(shù)的主要局限是微通道中傳質(zhì)不足,他們通過探究流速與逆流對(duì)傳質(zhì)的影響,調(diào)節(jié)參數(shù)顯著增強(qiáng)了化學(xué)鍍鍵合的均勻性.

7總結(jié)與展望

在芯片工藝制程不斷縮小的今天,不僅僅是芯片內(nèi)互連線,包括TSV、UBM、凸點(diǎn)等的制造工藝面臨著挑戰(zhàn).互連線與TSV尺寸的縮小使得傳統(tǒng)的PVD、CVD工藝制備阻擋層、種子層時(shí)容易形成“倒垂”現(xiàn)象,化學(xué)鍍因其優(yōu)秀的均鍍保形能力恰好滿足了芯片內(nèi)互連與3D封裝TSV中阻擋層、種子層均勻沉積的需求,被研究人員寄予厚望.此外,化學(xué)鍍因其工藝簡(jiǎn)單、設(shè)備成本低和條件溫和等優(yōu)點(diǎn),還被研究用于填充芯片互連線、填充TSV、UBM、凸點(diǎn)及鍵合等.例如,傳統(tǒng)電沉積方式在制造小尺寸凸點(diǎn)時(shí),可能會(huì)由于電流密度不均勻?qū)е峦裹c(diǎn)陣列不均勻;傳統(tǒng)熱壓鍵合銅柱凸點(diǎn)的方式可能會(huì)破壞芯片.使用化學(xué)鍍工藝替代將會(huì)大幅降低成本,并解決上述問題.但目前化學(xué)鍍?nèi)源嬖谝恍﹩栴},例如傳統(tǒng)化學(xué)鍍預(yù)處理工藝復(fù)雜;較慢的沉積速率在制造凸點(diǎn)、填充TSV時(shí)耗時(shí)較長(zhǎng),在TSV粗孔時(shí)甚至可能出現(xiàn)不能完全填充的情況;傳統(tǒng)化學(xué)鍍銅液中使用甲醛造成的污染等.目前對(duì)于芯片化學(xué)鍍預(yù)處理工藝常用接枝活化,不再需要粗化、敏化等工序,復(fù)雜度已大幅降低.更重要的是,選用化學(xué)鍍工藝所導(dǎo)致的整體工序簡(jiǎn)化將帶來更高的收益.例如SAM將有可能發(fā)揮阻擋層的作用從而不再需要沉積阻擋層,化學(xué)鍍技術(shù)填充互連線或TSV將不再需要種子層,且與電鍍相比過鍍現(xiàn)象不易發(fā)生從而減少后續(xù)CMP的時(shí)間與成本.化學(xué)鍍鍍速慢的缺點(diǎn)也被逐漸解決,已有部分研究者對(duì)鍍液進(jìn)行改進(jìn)以提升沉積速率,如高速鍍銅浴[156]、高速鍍鎳浴以及上文中提到的高速鍍金浴等[58].雖然部分研究并非針對(duì)芯片化學(xué)鍍,但其鍍液添加劑與體系均可活用于芯片化學(xué)鍍中.此外,隨著新一代芯片工藝制程的線寬不斷縮小, TSV孔徑與深度、凸點(diǎn)尺寸都會(huì)相對(duì)應(yīng)縮小以適應(yīng)需求,使得對(duì)于化學(xué)鍍的鍍速不需很高.而關(guān)于鍍液中甲醛的污染,也已有乙醛酸、次磷酸鹽作為替代[157],污染問題將被解決.因此雖然目前介紹的多數(shù)研究成果尚停留在實(shí)驗(yàn)室階段,還沒有在工業(yè)生產(chǎn)中普遍應(yīng)用,但隨著技術(shù)的不斷進(jìn)步,且近年來隨著芯片工藝制程節(jié)點(diǎn)線寬進(jìn)一步不斷縮小至3 nm及以下,對(duì)于芯片內(nèi)及封裝導(dǎo)電互連也提出更小孔徑金屬化的要求,如TSV孔徑與深度、凸點(diǎn)尺寸都需對(duì)應(yīng)縮小以適應(yīng)更小制程節(jié)點(diǎn),化學(xué)鍍因其獨(dú)特的優(yōu)勢(shì)很有希望在未來更低線寬芯片制造中得到廣泛的使用.

-

集成電路

+關(guān)注

關(guān)注

5420文章

11950瀏覽量

367141 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28600瀏覽量

232528 -

芯片制造

+關(guān)注

關(guān)注

10文章

676瀏覽量

29517

原文標(biāo)題:芯片制造中的化學(xué)鍍技術(shù)研究進(jìn)展

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

新型銅互連方法—電化學(xué)機(jī)械拋光技術(shù)研究進(jìn)展

印制電路板用化學(xué)鍍鎳金工藝探討-悌末源

FPC的電鍍,化學(xué)鍍及熱風(fēng)整平

《炬豐科技-半導(dǎo)體工藝》用于半導(dǎo)體封裝基板的化學(xué)鍍 Ni-P/Pd/Au

印制電路板用化學(xué)鍍鎳金工藝探討(二)

廢舊鎳氫電池回收處理技術(shù)研究進(jìn)展

化學(xué)鍍鎳金板問題及解決措施

化學(xué)鍍的特點(diǎn)優(yōu)勢(shì)及應(yīng)用介紹

不合格的PCB化學(xué)鍍鎳層怎樣處置

化學(xué)鍍的原理及具有哪些應(yīng)用特性

農(nóng)業(yè)機(jī)械自動(dòng)導(dǎo)航技術(shù)研究進(jìn)展

量子計(jì)算關(guān)鍵技術(shù)研究進(jìn)展

先進(jìn)激光雷達(dá)探測(cè)技術(shù)研究進(jìn)展

pcb表面處理 什么是化學(xué)鍍鎳

芯片制造“鍍”金術(shù):化學(xué)鍍技術(shù)的前沿突破與未來藍(lán)圖

芯片制造中的化學(xué)鍍技術(shù)研究進(jìn)展

芯片制造中的化學(xué)鍍技術(shù)研究進(jìn)展

評(píng)論