文章來源:學習那些事

原文作者:小陳婆婆

本文介紹了晶圓級扇入封裝相關原理。

晶圓級扇入封裝

在微電子行業飛速發展的背景下,封裝技術已成為連接芯片創新與系統應用的核心紐帶。其核心價值不僅體現于物理防護與電氣/光學互聯等基礎功能,更在于應對多元化市場需求的適應性突破,本文著力介紹晶圓級扇入封裝,分述如下。

晶圓級封裝的發展

晶圓級扇入封裝技術

晶圓級封裝的發展

隨著移動計算、高性能計算(HPC)及人工智能/機器學習(AI/ML)領域的爆發式增長,傳統封裝方案正面臨雙重革命性挑戰:內部維度上,系統級芯片(SoC)需在有限空間內實現晶體管密度與存儲容量的指數級擴展。

外部維度上,移動終端與HPC系統對性能、能效、散熱及微型化提出了近乎苛刻的要求。這驅動著行業探索從單芯片封裝向異構系統集成躍遷。

晶圓級封裝(WLP)與晶圓級系統集成(WLSI)技術在此背景下脫穎而出。依托晶圓級工藝的規模化優勢,WLSI平臺通過低成本、超薄化與高集成度的解決方案,重新定義了系統級整合的邊界。

其技術突破集中體現為兩大方向:其一,深度摩爾定律(More Moore)路徑下,通過先進封裝實現邏輯芯片的晶體管密度持續微縮;其二,超越摩爾定律(More than Moore)路徑中,將CMOS芯片與非硅基功能單元(如傳感器、光電器件)異構集成,構建單器件級多功能系統。這一模式轉變已催生出集成扇出(InFO)等標志性技術,成為移動計算領域的主流方案,并逐步向HPC場景延伸。

晶圓級扇入封裝技術

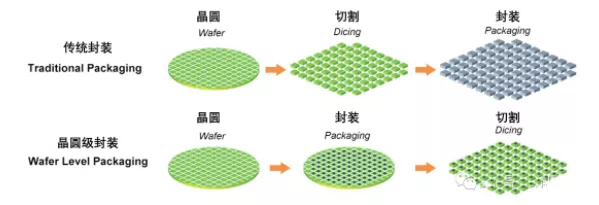

晶圓級封裝(WLP)作為先進封裝技術的核心分支,通過直接在晶圓上完成封裝工藝,實現了系統微型化與成本優化的雙重突破。

其技術體系包含扇入型(Fan-In)與扇出型(Fan-Out)兩大變體,本文僅聚焦扇入型WLP的技術特征與工程實踐。

封裝結構與工藝流程

扇入型WLP采用"芯片級封裝"架構,所有BGA焊球直接布局于硅芯片有效投影面積內,無需額外基板或轉接板。典型工藝流程包含四步:

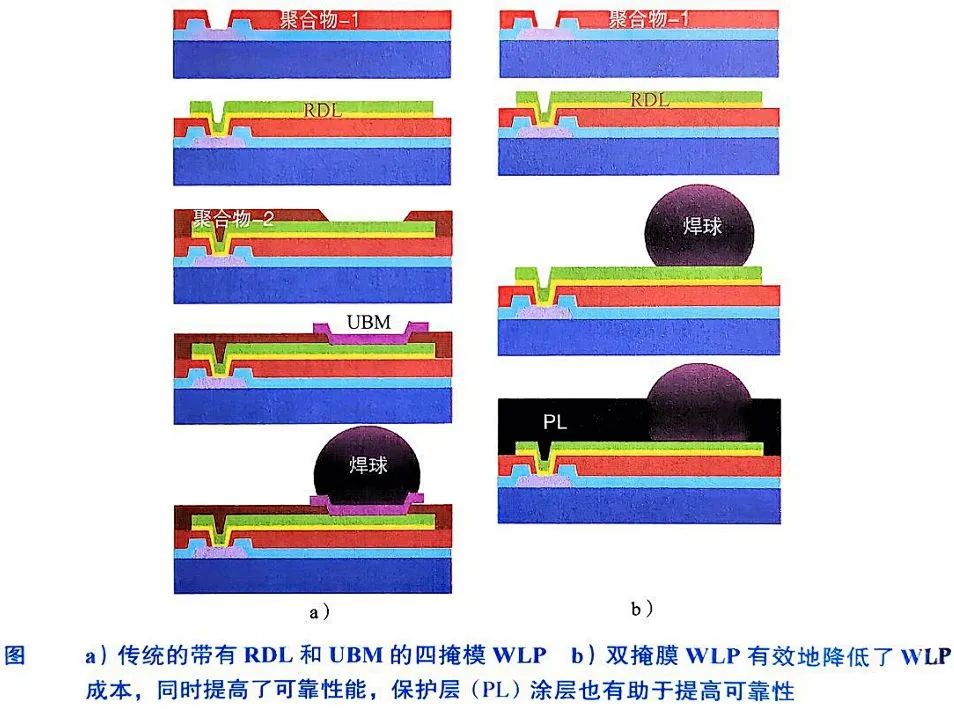

鈍化保護與RDL布線:在完成晶圓表面鈍化后,通過物理氣相沉積(PVD)制備鈦/銅種子層,電鍍銅形成再布線層(RDL),實現芯片I/O端口從密集焊盤區向封裝表面的扇入擴展;

介電層成型:采用聚酰亞胺(PI)或聚雙苯并惡唑(PBO)等光敏聚合物構建介電層,經光刻工藝形成互連通孔與布線溝槽;

UBM制備:通過電鍍或化學鍍工藝沉積凸點下金屬化層(UBM),常用材料包括銅、鎳或ENEPIG合金,形成與BGA焊球的冶金結合界面;

焊球植入與切割:在晶圓級完成BGA焊球植球后,進行晶圓切割獲得單顆封裝器件。

該工藝流程的精簡性賦予扇入型WLP三大優勢:封裝體尺寸與芯片尺寸1:1等比、工藝步驟較傳統封裝減少40%-60%、制造周期縮短至2-3天。

關鍵材料與結構優化

介電層設計:通過調節聚合物厚度(通常5-20μm)平衡機械緩沖與工藝精度。較厚介電層可緩解硅-PCB間熱膨脹系數失配(CTE mismatch)引發的熱應力,但會增加光刻通孔成型難度;

RDL層級擴展:單層銅布線可滿足常規需求,雙層RDL結構通過增加銅厚(≥5μm)提升機械可靠性,使芯片適用尺寸擴展至10mm×10mm級別;

UBM成本管控:銅基UBM方案較傳統鎳/金體系成本降低30%-50%,但需優化掩模數量(通常2-4層)以平衡工藝復雜度與良率。

可靠性挑戰與突破路徑

熱循環測試表明,硅-PCB界面CTE差異(硅4.3ppm/K vs. PCB 17ppm/K)導致的剪切應力是主要失效機理,具體表現為:

尺寸效應:芯片邊長超過8mm時,BGA焊球疲勞壽命呈指數下降;

應力緩解方案:通過三維結構優化實現應力分散:

增加封裝體高度(BGA球高≥0.3mm)提升中性點距離(DNP);

采用柔性聚合物材料(模量<2GPa)構建可變形緩沖層;

優化UBM焊盤形貌(圓形/環形設計)改善應力分布。

大尺寸芯片封裝實現

工程實踐證實,通過協同優化材料體系與結構設計,可實現邊長達25.4mm(1英寸)的大尺寸扇入型WLP。

關鍵技術包括:

復合緩沖結構:采用"介電層/RDL/UBM"三層復合緩沖,將熱循環壽命提升至1000次以上;

焊球強化技術:通過頸部聚合物包覆(Underfill Encapsulation)使焊球抗剪強度提升40%;

制造良率管控:在6mm×6mm以下尺寸可保持99%以上良率,8mm×8mm器件需引入缺陷檢測與激光修復工藝。

當前行業實踐顯示,扇入型WLP在消費電子領域形成標準化方案,而10mm×10mm以上尺寸則需權衡工藝成本與可靠性裕度,這推動了扇出型WLP在高性能計算領域的迭代發展。

-

芯片

+關注

關注

459文章

52174瀏覽量

436138 -

晶圓

+關注

關注

52文章

5118瀏覽量

129163 -

封裝

+關注

關注

128文章

8497瀏覽量

144784

原文標題:晶圓級扇入封裝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是晶圓級扇入封裝技術

什么是晶圓級扇入封裝技術

評論