晶圓級封裝(Wafer Level Packaging,縮寫WLP)是一種先進的封裝技術,因其具有尺寸小、電性能優良、散熱好、成本低等優勢,近年來發展迅速。根據Verified Market Research 研究數據,晶圓級封裝市場 2020 年為 48.4 億美元,預計到 2028 年將達到 228.3 億美元,從 2021 年到 2028 年的復合年增長率為 21.4%。

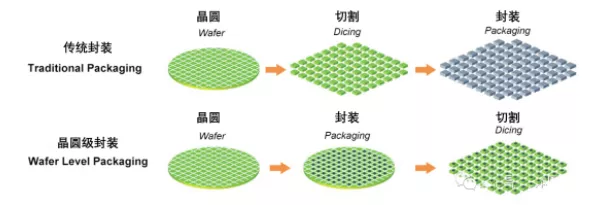

一、晶圓級封裝VS傳統封裝

在傳統晶圓封裝中,是將成品晶圓切割成單個芯片,然后再進行黏合封裝。不同于傳統封裝工藝,晶圓級封裝是在芯片還在晶圓上的時候就對芯片進行封裝,保護層可以黏接在晶圓的頂部或底部,然后連接電路,再將晶圓切成單個芯片。

相比于傳統封裝,晶圓級封裝具有以下優點:

1、封裝尺寸小

由于沒有引線、鍵合和塑膠工藝,封裝無需向芯片外擴展,使得WLP的封裝尺寸幾乎等于芯片尺寸。

2、高傳輸速度

與傳統金屬引線產品相比,WLP一般有較短的連接線路,在高效能要求如高頻下,會有較好的表現。

3、高密度連接

WLP可運用數組式連接,芯片和電路板之間連接不限制于芯片四周,提高單位面積的連接密度。

4、生產周期短

WLP從芯片制造到、封裝到成品的整個過程中,中間環節大大減少,生產效率高,周期縮短很多。

5、工藝成本低

WLP是在硅片層面上完成封裝測試的,以批量化的生產方式達到成本最小化的目標。WLP的成本取決于每個硅片上合格芯片的數量,芯片設計尺寸減小和硅片尺寸增大的發展趨勢使得單個器件封裝的成本相應地減少。WLP可充分利用晶圓制造設備,生產設施費用低。

二、晶圓級封裝的工藝流程

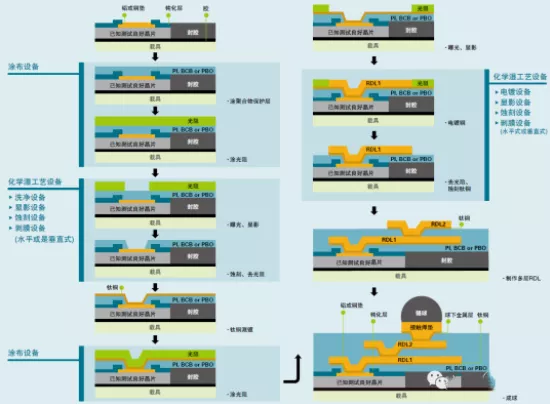

圖 WLP工藝流程

晶圓級封裝工藝流程如圖所示:

1、涂覆第一層聚合物薄膜,以加強芯片的鈍化層,起到應力緩沖的作用。聚合物種類有光敏聚酰亞胺(PI)、苯并環丁烯(BCB)、聚苯并惡唑(PBO)。

2、重布線層(RDL)是對芯片的鋁/銅焊區位置重新布局,使新焊區滿足對焊料球最小間距的要求,并使新焊區按照陣列排布。光刻膠作為選擇性電鍍的模板以規劃RDL的線路圖形,最后濕法蝕刻去除光刻膠和濺射層。

3、涂覆第二層聚合物薄膜,是圓片表面平坦化并保護RDL層。在第二層聚合物薄膜光刻出新焊區位置。

4、凸點下金屬層(UBM)采用和RDL一樣的工藝流程制作。

5、植球。焊膏和焊料球通過掩膜板進行準確定位,將焊料球放置于UBM上,放入回流爐中,焊料經回流融化與UBM形成良好的浸潤結合,達到良好的焊接效果。

三、晶圓級封裝的發展趨勢

隨著電子產品不斷升級換代,智能手機、5G、AI等新興市場對封裝技術提出了更高要求,使得封裝技術朝著高度集成、三維、超細節距互連等方向發展。晶圓級封裝技術可以減小芯片尺寸、布線長度、焊球間距等,因此可以提高集成電路的集成度、處理器的速度等,降低功耗,提高可靠性,順應了電子產品日益輕薄短小、低成本的發展要需求。

晶圓級封裝技術要不斷降低成本,提高可靠性水平,擴大在大型IC方面的應用:

1、通過減少WLP的層數降低工藝成本,縮短工藝時間,主要是針對I/O少、芯片尺寸小的產品。

2、通過新材料應用提高WLP的性能和可靠度。主要針對I/O多、芯片尺寸大的產品。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52169瀏覽量

436094 -

晶圓

+關注

關注

52文章

5118瀏覽量

129160 -

封裝

+關注

關注

128文章

8494瀏覽量

144779

原文標題:【科普】什么是晶圓級封裝

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

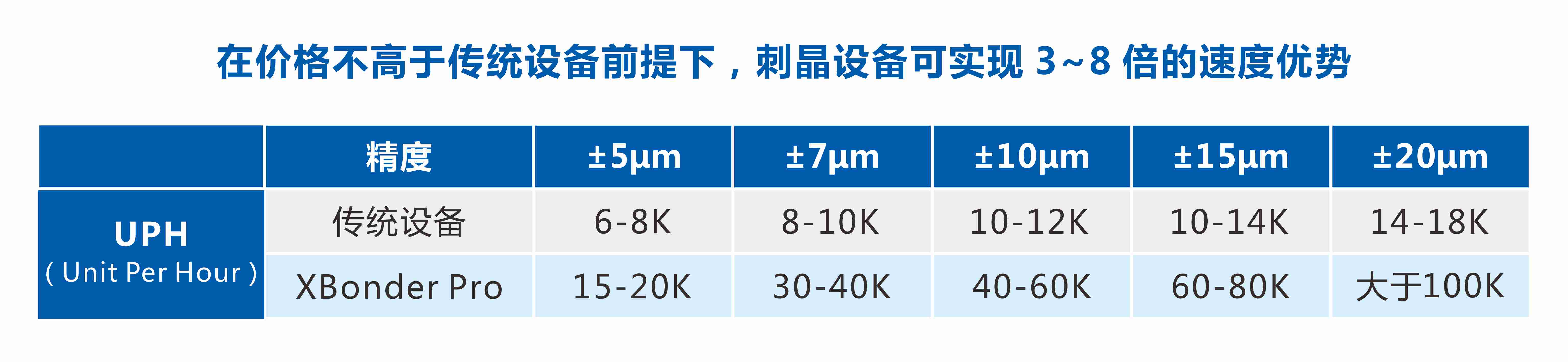

簽約頂級封裝廠,普萊信巨量轉移技術掀起晶圓級封裝和板級封裝的技術革命

一種新型RDL PoP扇出晶圓級封裝工藝芯片到晶圓鍵合技術

先進封裝技術- 6扇出型晶圓級封裝(FOWLP)

扇入型和扇出型晶圓級封裝的區別

Moldex3D模流分析之晶圓級封裝(EWLP)制程

什么是晶圓級封裝

什么是晶圓級封裝

評論