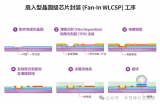

隨著半導體技術的飛速發展,晶圓級封裝(WLP)作為先進封裝技術的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。在晶圓級封裝過程中,Bump工藝扮演著至關重要的角色。Bump,即凸塊,是晶圓級封裝中實現芯片與外部電路電氣連接的關鍵結構。本文將深入解析晶圓級封裝Bump工藝的關鍵點,探討其技術原理、工藝流程、關鍵參數以及面臨的挑戰和解決方案。

一、Bump工藝概述

Bump工藝,又稱凸點工藝,是晶圓級封裝中的一道核心工序。其主要目的是在晶圓的輸入輸出(I/O)焊盤上形成微米級的金屬凸塊,這些凸塊將作為電氣連接的中介,實現芯片與封裝基板或電路板上的焊盤之間的電氣連接。與傳統的引線鍵合技術相比,Bump工藝具有更高的端口密度、更短的信號傳輸路徑、更低的信號延遲以及更優良的熱傳導性和可靠性。

Bump工藝的實現方式多種多樣,包括電鍍、植球、印刷等。其中,電鍍型凸點工藝因其高精度、高可靠性和高一致性而被廣泛應用。電鍍型凸點工藝通常包括底層金屬(UBM)形成、光刻、電鍍、去膠、刻蝕等步驟。

二、Bump工藝流程詳解

- 晶圓清洗

晶圓清洗是Bump工藝的第一步,其目的是去除晶圓表面的污染物(如顆粒、氧化物、有機物等),確保后續工藝的可靠性。清洗過程通常采用濕法清洗(如RCA清洗)、等離子清洗或化學機械拋光(CMP)等方法。

- 底層金屬(UBM)形成

UBM層是Bump工藝中的關鍵結構之一,它位于晶圓焊盤和凸塊之間,主要起到增強粘附性、提高導電性和擴散阻擋的作用。UBM層通常由多層金屬薄膜組成,如Ti/Cu、TiW/Cu等。UBM層的形成通常采用濺射、化學鍍或電鍍等方法。

- 光刻

光刻是Bump工藝中的關鍵步驟之一,其目的是將凸點的圖形轉移到光刻膠上。光刻過程包括涂覆光刻膠、曝光、顯影等步驟。光刻膠的厚度和分辨率需與凸塊的高度和尺寸相匹配,以確保凸點圖形的準確性和一致性。

- 電鍍

電鍍是Bump工藝中的核心步驟之一,其目的是在光刻膠開口處沉積金屬形成凸塊。電鍍過程通常采用掛鍍法或垂直鍍法,電鍍液的選擇和電鍍參數的控制對凸塊的形貌和機械性能具有重要影響。常用的電鍍金屬包括銅、錫銀合金(SAC)等。

- 去膠與刻蝕

電鍍完成后,需要去除光刻膠和UBM層上的多余金屬。去膠過程通常采用濕法去膠或干法去膠等方法,刻蝕過程則采用化學刻蝕或等離子刻蝕等方法。去膠和刻蝕過程需精確控制,以避免對凸塊和晶圓表面造成損傷。

- 回流焊與檢測

對于某些類型的凸塊(如錫銀合金凸塊),還需要進行回流焊處理以增強凸塊與焊盤之間的粘附性。回流焊過程需精確控制溫度和時間等參數,以避免對凸塊和晶圓造成熱損傷。最后,還需對凸塊進行外觀和電氣性能檢測,以確保其滿足設計要求。

三、Bump工藝關鍵參數分析

- 凸塊高度與尺寸

凸塊的高度和尺寸是Bump工藝中的關鍵參數之一。凸塊的高度需與封裝基板或電路板上的焊盤高度相匹配,以確保電氣連接的可靠性。凸塊的尺寸則需與晶圓焊盤的尺寸相匹配,以避免在回流焊過程中發生偏移或脫落。

- UBM層厚度與成分

UBM層的厚度和成分對凸塊的粘附性、導電性和擴散阻擋性能具有重要影響。UBM層的厚度需足夠厚以增強粘附性,但過厚則會導致電鍍過程中金屬沉積不均勻。UBM層的成分需根據電鍍金屬和晶圓材料的特性進行選擇,以確保良好的導電性和擴散阻擋性能。

- 光刻膠厚度與分辨率

光刻膠的厚度和分辨率對凸點圖形的準確性和一致性具有重要影響。光刻膠的厚度需與凸塊的高度相匹配,以確保凸點圖形的準確性。光刻膠的分辨率則需足夠高以滿足微凸點(<50μm)的需求。

- 電鍍參數控制

電鍍參數的控制對凸塊的形貌和機械性能具有重要影響。電鍍電流密度、電鍍液成分和溫度等參數需精確控制以確保凸塊的均勻性和一致性。同時,還需避免電鍍過程中產生的氣泡和雜質對凸塊質量的影響。

- 回流焊參數控制

對于需要進行回流焊處理的凸塊,回流焊參數的控制同樣至關重要。回流焊溫度、時間和氣氛等參數需精確控制以避免對凸塊和晶圓造成熱損傷。同時,還需確保回流焊過程中凸塊與焊盤之間的粘附性得到增強。

四、Bump工藝面臨的挑戰與解決方案

- 凸塊間距微縮化挑戰

隨著半導體技術的不斷發展,凸塊間距正逐漸微縮化。目前,凸塊間距已縮小到70-80μm的極細間距范圍。這對Bump工藝的精度和一致性提出了更高要求。為解決這一問題,可采用更先進的光刻技術和電鍍設備,以及更精細的鋼網和錫膏材料。

- 凸塊高度一致性挑戰

凸塊高度的一致性對電氣連接的可靠性具有重要影響。然而,在實際生產中,由于晶圓表面平整度、電鍍液成分和溫度等因素的波動,凸塊高度往往存在一定的差異。為解決這一問題,可采用更精確的電鍍參數控制和回流焊參數控制方法,以及更先進的檢測技術和設備。

- 凸塊與焊盤粘附性挑戰

凸塊與焊盤之間的粘附性對電氣連接的穩定性和可靠性具有重要影響。然而,在實際生產中,由于晶圓表面污染、UBM層成分和厚度等因素的影響,凸塊與焊盤之間的粘附性往往存在不足。為解決這一問題,可采用更嚴格的晶圓清洗和UBM層形成工藝控制方法,以及更先進的回流焊技術和設備。

- 凸塊材料選擇與成本挑戰

凸塊材料的選擇對Bump工藝的成本和性能具有重要影響。然而,在實際生產中,由于不同凸塊材料的成本和性能差異較大,往往需要在成本和性能之間進行權衡。為解決這一問題,可采用更先進的材料研發和生產技術,以及更靈活的材料選擇和組合方法。

五、Bump工藝在晶圓級封裝中的應用前景

隨著半導體技術的不斷發展,晶圓級封裝正逐漸成為集成電路封裝的主流趨勢。而Bump工藝作為晶圓級封裝中的核心工序之一,其應用前景十分廣闊。未來,隨著凸塊間距的進一步微縮化、凸塊高度的進一步一致化以及凸塊材料與焊盤粘附性的進一步提高,Bump工藝將在晶圓級封裝中發揮更加重要的作用。

同時,隨著5G通信、人工智能、物聯網等新興技術的不斷發展,對集成電路的性能和集成度提出了更高要求。而Bump工藝作為提高集成電路性能和集成度的關鍵手段之一,將在這些新興技術的應用中發揮重要作用。例如,在5G通信中,Bump工藝可實現高速信號傳輸和低延遲性能;在人工智能中,Bump工藝可實現高密度計算和高效能存儲;在物聯網中,Bump工藝可實現低功耗和長續航性能。

六、結論

晶圓級封裝Bump工藝作為先進封裝技術的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。通過深入解析Bump工藝的技術原理、工藝流程、關鍵參數以及面臨的挑戰和解決方案,我們可以更好地理解和應用這項技術。未來,隨著半導體技術的不斷發展和新興技術的不斷涌現,Bump工藝將在晶圓級封裝中發揮更加重要的作用,為集成電路的性能和集成度提升做出更大貢獻。同時,我們也需要不斷關注Bump工藝的最新進展和趨勢,以及時應對各種挑戰和機遇。

-

晶圓

+關注

關注

52文章

5118瀏覽量

129163 -

封裝

+關注

關注

128文章

8497瀏覽量

144784 -

wlp

+關注

關注

0文章

14瀏覽量

10802

發布評論請先 登錄

深入探索:晶圓級封裝Bump工藝的關鍵點

深入探索:晶圓級封裝Bump工藝的關鍵點

評論