該方法只用于慢到快時鐘域的1bit信號傳遞。在Xilinx器件中,可以使用(* ASYNC_REG ....

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個 LogiCORE IP....

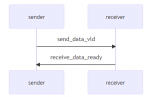

本文主要介紹握手的基本概念,讀者可通過該篇文章對握手有個基本概念。

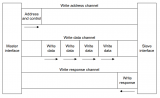

寫數據通道從主設備傳輸數據到從設備,在寫傳輸時,從設備使用寫響應通道通知主設備傳輸完成。

Architectural Configuration選擇為并行模式,具有單周期數據吞吐量和較大的硅....

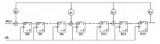

在做模塊劃分時,通常會出現這種情形,某個大的模塊中包含了一個或多個功能子模塊,verilog是通過模....

下面是調用的DDR3模塊的,模塊的倒數第二行是,模塊的時鐘輸入,時鐘源來自PLL產生的系統時鐘的倍頻....

大家好,歡迎來到至芯科技FPGA煉獄營地,準備開啟我們的偉大征程!正所謂“兵馬未動,糧草先行”,戰前....

位流驗證,對于芯片研發是一個非常重要的測試手段,對于純軟件開發人員,最難理解的就是位流驗證。在FPG....

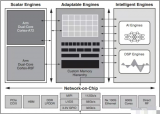

Ultrascale是賽靈思開發的支持包含步進功能的增強型FPGA架構,相比7系列的28nm工藝,U....

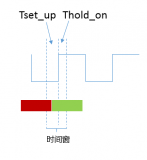

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或fal....

在實際電路中存在兩種延遲,慣性延遲 (Inertial delay) 和傳導延遲 (Transpor....

zynq系列中的FPGA,都會自帶兩個iic設備,我們直接調用其接口函數即可運用。使用xilinx官....

為了盡快把新產品推向市場,數字系統的設計者需要考慮如何加速設計開發的周期。設計加速主要可以從“設計的....

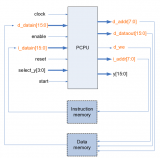

本文實現的CPU是一個五級流水線的精簡版CPU(也叫PCPU,即pipeline),包括IF(取指令....

本文詳細闡述了在一個testbench中,應該如何使用阻塞賦值與非阻塞賦值。首先說結論,建議在tes....

用最右邊的字符下劃線代表低電平有效,高電平有效的信號不得以下劃線表示,短暫的有效信號建議采用高電平有....

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynam....

FIFO(First in First out)為先進先出隊列,具有存儲功能,可用于不同時鐘域間傳輸....

AXI直接數值存取(Drect Memory Access,DMA)IP核在AXI4內存映射和AXI....

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號的時鐘并行視頻數據,....

隨著數字化時代的飛速發展,人工智能(AI)、大數據分析、自動駕駛等新興領域的需求不斷攀升。FPGA作....

本文簡單介紹Zynq中的SPI控制器。本文將“master”稱為“主機”;將“slave”稱為“從機....

添加好ZYNQ7 Processing System IP核后,需要對其進行配置,雙擊彈出如下窗口。....

線網類型表示硬件電路元件之間實際存在的物理連線,有很多種:wire、tri、wor等等,當然日常使用....

CRC即循環冗余校驗碼:是數據通信領域中最常用的一種查錯校驗碼,其特征是信息字段和校驗字段的長度可以....

Vivado的時序約束是保存在xdc文件中,添加或創建設計的工程源文件后,需要創建xdc文件設置時序....

Verilog HDL(Hardware Description Language)是一種硬件描述語....

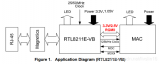

以太網MAC模塊負責實現以太網MAC子層的功能,完成802.3ab的數據封裝與解封。其同時負責適配硬....

本文將使用三段式狀態機(Moore型)的寫法來對DS18B20進行測溫操作,以便了解DS18B20和....