1.[Place 30-51] IDELAYCTRL elements have been found to be associated with IODELAY_GROUP ‘DDR3_IODELAY_MIG0’, but the design does not contain IODELAY elements associated with this IODELAY_GROUP.

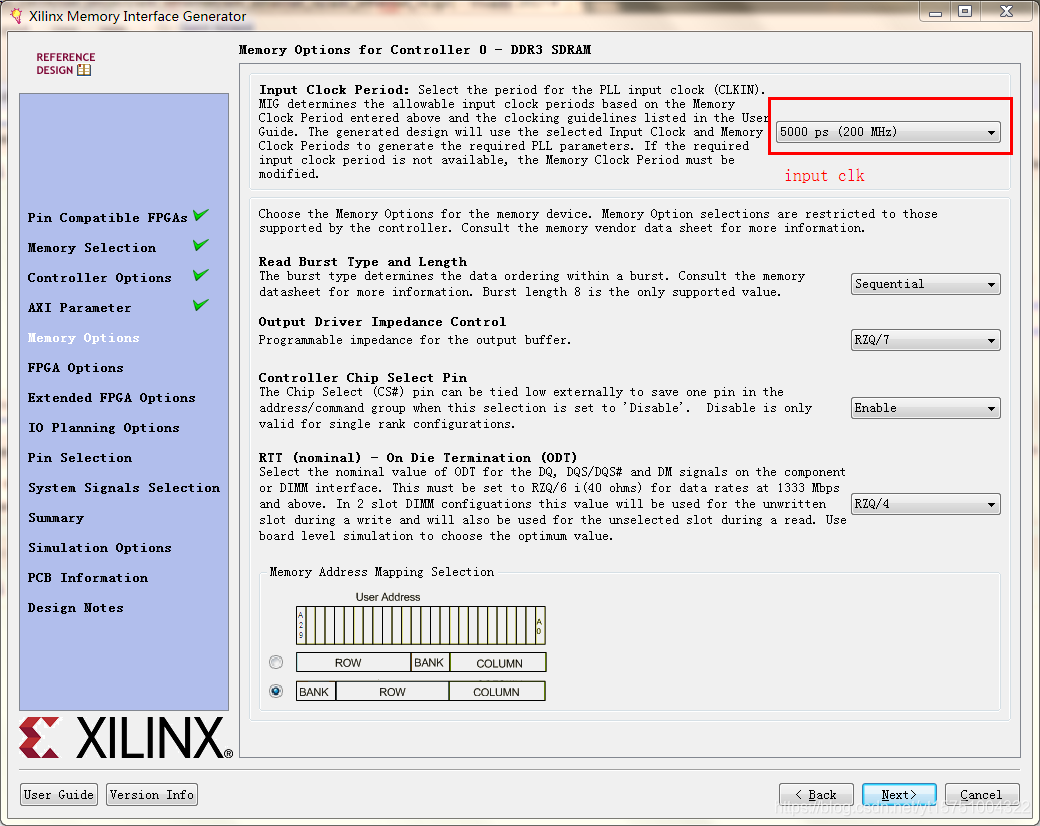

問題解析:這個(gè)問題很簡(jiǎn)單,就是DDR3 module 的輸入時(shí)鐘與所需要的時(shí)鐘不匹配,例如配置所需的時(shí)鐘為200MHz

下面是調(diào)用的DDR3模塊的,模塊的倒數(shù)第二行是,模塊的時(shí)鐘輸入,時(shí)鐘源來自PLL產(chǎn)生的系統(tǒng)時(shí)鐘的倍頻。

ddr3 ddr3_1 ( // Memory interface ports .ddr3_addr (ddr3_addr), .ddr3_ba (ddr3_ba), .ddr3_cas_n (ddr3_cas_n), .ddr3_ck_n (ddr3_ck_n), .ddr3_ck_p (ddr3_ck_p),.ddr3_cke (ddr3_cke), .ddr3_ras_n (ddr3_ras_n), .ddr3_reset_n (ddr3_reset_n), .ddr3_we_n (ddr3_we_n), .ddr3_dq (ddr3_dq), .ddr3_dqs_n (ddr3_dqs_n), .ddr3_dqs_p (ddr3_dqs_p), .init_calib_complete (init_calib_complete), .ddr3_cs_n (ddr3_cs_n), .ddr3_dm (ddr3_dm), .ddr3_odt (ddr3_odt), // Application interface ports.ui_clk (ui_clk), .ui_clk_sync_rst (ui_clk_sync_rst), // outputui_clk_sync_rst.mmcm_locked (), // outputmmcm_locked.aresetn (1'b1), // inputaresetn.app_sr_req (1'b0), // inputapp_sr_req.app_ref_req (1'b0), // inputapp_ref_req.app_zq_req (1'b0), // inputapp_zq_req.app_sr_active (), // outputapp_sr_active.app_ref_ack (), // outputapp_ref_ack.app_zq_ack (), // outputapp_zq_ack// Slave Interface Write Address Ports.s_axi_awid (s00_axi_awid), // input [0:0]s_axi_awid.s_axi_awaddr (s00_axi_awaddr), // input [29:0]s_axi_awaddr.s_axi_awlen (s00_axi_awlen), // input [7:0]s_axi_awlen.s_axi_awsize (s00_axi_awsize), // input [2:0]s_axi_awsize.s_axi_awburst (s00_axi_awburst), // input [1:0]s_axi_awburst.s_axi_awlock (s00_axi_awlock), // input [0:0]s_axi_awlock.s_axi_awcache (s00_axi_awcache), // input [3:0]s_axi_awcache.s_axi_awprot (s00_axi_awprot), // input [2:0]s_axi_awprot.s_axi_awqos (s00_axi_awqos), // input [3:0]s_axi_awqos.s_axi_awvalid (s00_axi_awvalid), // inputs_axi_awvalid.s_axi_awready (s00_axi_awready), // outputs_axi_awready// Slave Interface Write Data Ports.s_axi_wdata (s00_axi_wdata), // input [63:0]s_axi_wdata.s_axi_wstrb (s00_axi_wstrb), // input [7:0]s_axi_wstrb.s_axi_wlast (s00_axi_wlast), // inputs_axi_wlast.s_axi_wvalid (s00_axi_wvalid), // inputs_axi_wvalid.s_axi_wready (s00_axi_wready), // outputs_axi_wready// Slave Interface Write Response Ports.s_axi_bid (s00_axi_bid), // output [0:0]s_axi_bid.s_axi_bresp (s00_axi_bresp), // output [1:0]s_axi_bresp.s_axi_bvalid (s00_axi_bvalid), // outputs_axi_bvalid.s_axi_bready (s00_axi_bready), // inputs_axi_bready// Slave Interface Read Address Ports.s_axi_arid (s00_axi_arid), // input [0:0]s_axi_arid.s_axi_araddr (s00_axi_araddr), // input [29:0]s_axi_araddr.s_axi_arlen (s00_axi_arlen), // input [7:0]s_axi_arlen.s_axi_arsize (s00_axi_arsize), // input [2:0]s_axi_arsize.s_axi_arburst (s00_axi_arburst), // input [1:0]s_axi_arburst.s_axi_arlock (s00_axi_arlock), // input [0:0]s_axi_arlock.s_axi_arcache (s00_axi_arcache), // input [3:0]s_axi_arcache.s_axi_arprot (s00_axi_arprot), // input [2:0]s_axi_arprot.s_axi_arqos (s00_axi_arqos), // input [3:0]s_axi_arqos.s_axi_arvalid (s00_axi_arvalid), // inputs_axi_arvalid.s_axi_arready (s00_axi_arready), // outputs_axi_arready// Slave Interface Read Data Ports.s_axi_rid (s00_axi_rid), // output [0:0]s_axi_rid.s_axi_rdata (s00_axi_rdata), // output [63:0]s_axi_rdata.s_axi_rresp (s00_axi_rresp), // output [1:0]s_axi_rresp.s_axi_rlast (s00_axi_rlast), // outputs_axi_rlast.s_axi_rvalid (s00_axi_rvalid), // outputs_axi_rvalid.s_axi_rready (s00_axi_rready), // inputs_axi_rready// System Clock Ports.sys_clk_i (clk_DDR ),// input DDR3 CLK,DDR3模塊的輸入時(shí)鐘.sys_rst (rst_n ));// input sys_rst

下面是系統(tǒng)時(shí)鐘緩沖模塊IBUFG module,和時(shí)鐘倍頻PLL module,如果這個(gè)時(shí)候的clk_DDR時(shí)鐘不是DRR3模塊所需要的200MHz,那么就會(huì)產(chǎn)生上面的錯(cuò)誤。

IBUFGIBUFG_U( .O(clk_bufg), .I(sys_clk) );//generate the video and CMOS sensor clocksys_pllvideo ( // Clock out ports .clk_out1(clk_video), // output clk_out1,40M.clk_out2(clk_40m), // output clk_out2 .clk_out3(adc_clk), // output clk_out3,125M.clk_out4(clk_DDR), // output clk_out3,125M// Status and control signals .locked( ), // output locked// Clock in ports .clk_in1(clk_bufg)); // input clk_in1

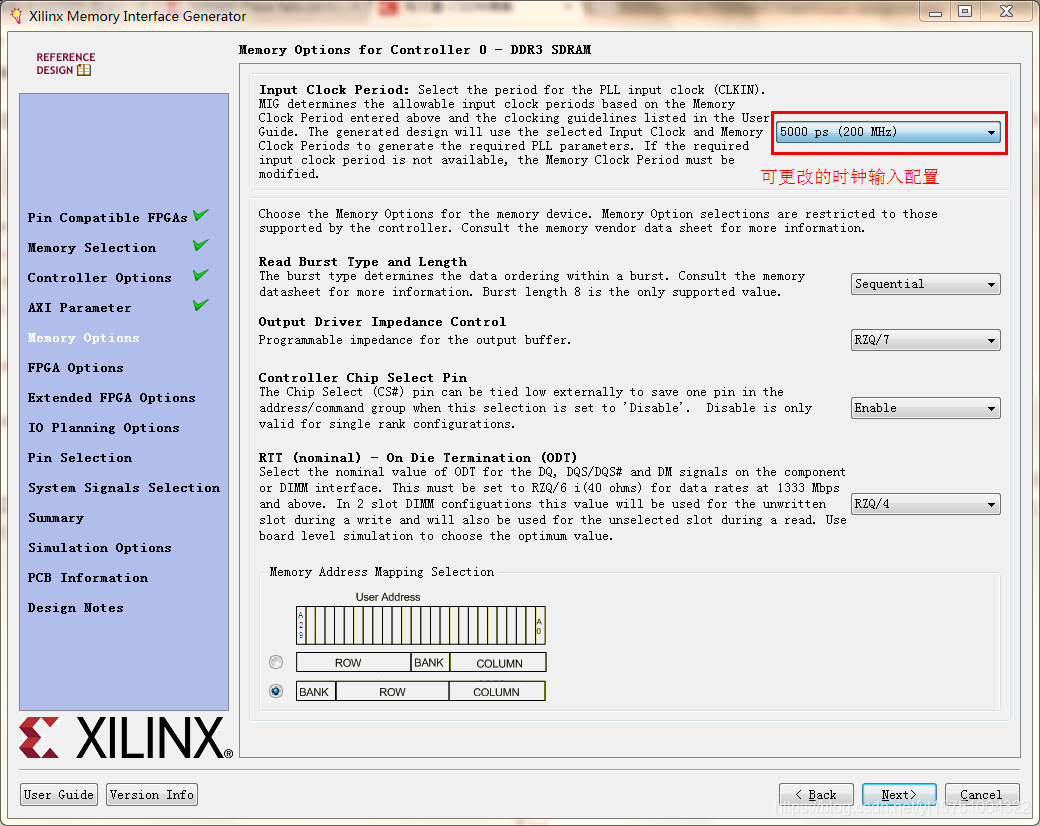

解決方法:把PLL部分的clk_DDR的時(shí)鐘輸出為200MHz就可以了,或者把MIG中的DDR3的輸入時(shí)鐘改成你想要的時(shí)鐘大小即可,反正時(shí)鐘匹配上就可以了。

-

DDR3

+關(guān)注

關(guān)注

2文章

282瀏覽量

42933 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1879瀏覽量

132840 -

MIG

+關(guān)注

關(guān)注

0文章

13瀏覽量

11093 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68217

原文標(biāo)題:VIVADO調(diào)用MIG產(chǎn)生DDR3時(shí)實(shí)例化遇到的問題以及解決方法

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于Arty Artix-35T FPGA開發(fā)板的DDR3和mig介紹

cyclone V控制DDR3的讀寫,quartusII配置DDR3 ip核后,如何調(diào)用實(shí)現(xiàn)DDR3的讀寫呢,謝謝

完成DDR3校準(zhǔn)的MIG IP失敗的原因?

如何解決電路板中的DDR3校準(zhǔn)問題?

如何在Vivado中使用MIG設(shè)計(jì)DDR3 SODIMM接口?

基于FPGA的DDR3多端口讀寫存儲(chǔ)管理的設(shè)計(jì)與實(shí)現(xiàn)

關(guān)于DDR3信號(hào)扇出和走線問題解析

基于Digilent介紹DDR3和mig

關(guān)于Virtex7上DDR3的測(cè)試?yán)淘斀?/a>

lattice DDR3 IP核的生成及調(diào)用過程

Virtex7上DDR3的測(cè)試?yán)?/a>

DDR3緩存模塊仿真平臺(tái)構(gòu)建步驟

基于AXI總線的DDR3讀寫測(cè)試

基于FPGA的DDR3讀寫測(cè)試

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

評(píng)論