本文簡單介紹Zynq中的SPI控制器。本文將“master”稱為“主機”;將“slave”稱為“從機”;將“slave slect”從機選擇簡稱為SS。

SPI控制器

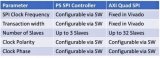

Zynq中的SPI總線控制器能夠與各種外設通信,如存儲器、溫度傳感器、壓力傳感器、模擬轉換器、實時時鐘、任何支持串行模式的SD卡。SPI控制器可以工作在主機模式、從機模式、舵主模式。Zynq-7000系列包括2個SPI控制器。

主機模式:控制器驅動串行時鐘(源自PS時鐘系統)和從機選擇信號。控制器有3個從機選擇信號(Slave Select,簡稱SS),并且可以在外部擴展。控制器通過向32位的讀/寫數據端口寄存器寫入字節,實現讀取或寫入從機設備。

從機模式:控制器接收來自外部設備的串行時鐘,并使用SPI_Ref_Clk來同步數據捕獲。從機模式包括一個可編程的啟動檢測機制,當SS信號有效時使能控制器。

多主模式:當控制器處于無效狀態時,其輸出信號是三態的;當控制器使能時,可以檢測連接錯誤。通過復位SPI使能位,控制器輸出將立刻轉換為三態。

SPI I/O接口和軟件之間有讀、寫FIFO,作為緩存。主機、從機I/O模式下都可使用FIFO。

控制器特性

每個SPI控制器可以獨立配置,包括如下特性:

四線式總線:MOSI(主機輸出-從機輸入)、MISO(主機輸入-從機輸出)、SCLK、SS,主機模式下有3個從機選擇信號;

全雙工工作,支持同時接收和發送;

通過APB從接口的32位可編程寄存器;

將讀/寫數據映射到Rx/Tx FIFO,以字節為單位;

主機模式下,可選擇手動或自動啟動數據傳輸、手動或自動從機選擇模式、從機選擇信號可以直接與從機設備連接,也可以在外部做擴展(比如3-8譯碼器)、可編程的SS和MOSI延遲;

從機模式下,可編程的啟動檢測模式;

當SPI的I/O信號由MIO引腳引出時,SCLK為50MHz;由EMIO接口引出到PL管腳時,SCLK為25MHz;

可編程的時鐘相位和極性;

可選擇中斷驅動或輪詢狀態。

系統框圖

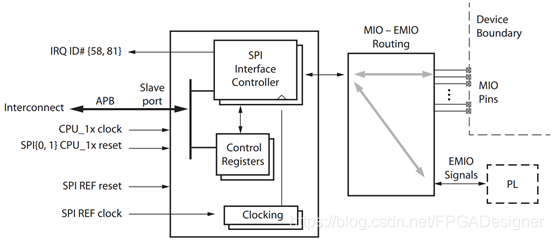

SPI控制器的系統框圖如下,簡單介紹一下各部分。

上圖中有兩個獨立的SPI接口控制器,每個控制器的I/O信號可以路由(Routing)到MIO管腳或EMIO接口。每個控制器有單獨的中斷信號(中斷ID 58和81)到PS中斷控制器,還有單獨的復位信號。每個控制器都有自己的一組控制寄存器和狀態寄存器。

PS時鐘子系統為SPI控制器提供一個參考時鐘SPI_Ref_Clk,用于控制器的邏輯功能,再通過波特率發生器產生用于主機模式的SCLK。

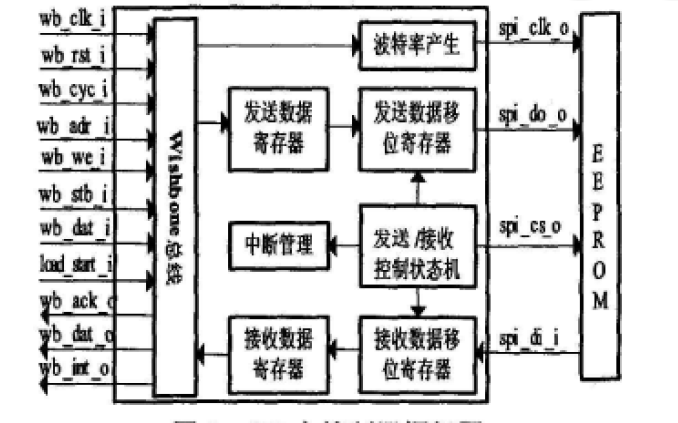

功能模塊框圖

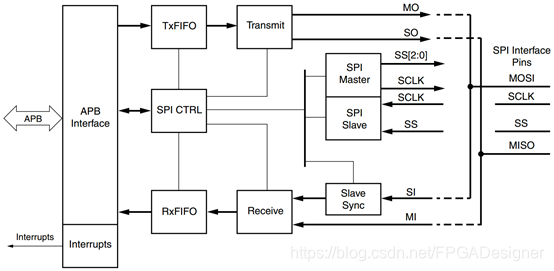

SPI控制器的功能模塊框圖如下所示:

簡單介紹一下各部分:

APB接口:32位,用于響應寄存器的讀、寫,處理數據端口和FIFO之間的讀寫命令和數據。數據端口以字節(即[7:0])為單位。

SPI主機:此時控制器要驅動SCLK,并輸出3個從機選擇信號。MOSI信號上的從機選擇和傳輸開始,可以在軟件中手動控制,也可以由硬件自動控制。

SPI從機:此時控制器只使用一個從機選擇的輸入信號(SS0)。SCLK與控制器的參考時鐘(SPI_Ref_Clk)同步。

Tx和Rx FIFO:每個FIFO都是128字節,軟件使用寄存器映射后的數據端口寄存器來讀、寫FIFO。FIFO橋接了兩個時鐘域:APB接口和控制器的SPI_Ref_Clk。

主機模式

SPI I/O接口向從機發送數據,或者接收從機的數據。控制器一次只能選擇一個從機設備。如果從機設備超過3個,可以使用3-8譯碼器,將3個從機選擇信號擴展為8路。

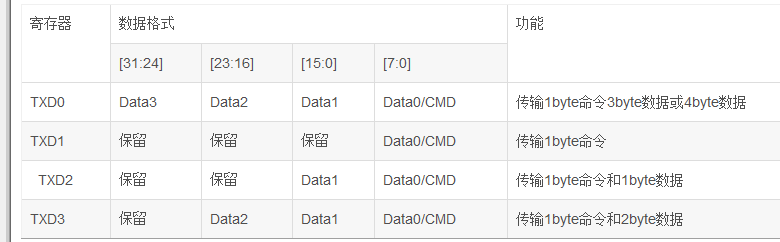

1.數據傳輸

發送:SCLK和MOSI信號由主機控制。軟件把要傳輸的數據寫入TxFIFO,由手動或自動的方式啟動傳輸,數據驅動到MOSI(主輸出-從輸入)管腳上。只要TxFIFO中有數據便會連續傳輸。

接收:數據從MISO(主輸入-從輸出)管腳上串行接收數據,一次加載8bit到RxFIFO中,軟件讀取RxFIFO。每向TxFIFO寫n字節數據,也會有n字節數據存儲在RxFIFO中,軟件必須讀取完這些數據后才能開啟下一次傳輸。

2.自動/手動SS與啟動

SPI I/O接口上的數據傳輸可以通過軟件手動啟動,也可以由控制器硬件自動啟動。從機選擇也可以由軟件或硬件完成。四種情況總結如下表:

軟件中要通過Tx/Rx FIFO的閾值級別來避免FIFO中數據不夠或溢出。當TxFIFO中的字節數小于TxFIFO閾值級別時,標記TxFIFO Not Full狀態;當RxFIFO中的字節數達到128時,標記RxFIFO Full狀態。

從機模式

控制器接收來自外部主機的數據,同時輸出一個應答。SCLK鎖存MOSI(輸入)信號上的數據。如果SS(輸入)信號為無效狀態,控制器便忽略MOSI上的輸入。當SS有效時,在傳輸期間必須持續保持有效狀態。如果傳輸過程中SS變為無效,控制器會發出中斷,以提醒用戶。

軟件把要發送給主機的數據寫入TxFIFO中,然后控制器將其串行化到MISO信號上。當TxFIFO中有數據且SS信號持續有效時,將保持傳輸狀態。SS輸入管腳必須由SCLK輸入同步驅動。控制器工作在SPI_Ref_Clk時鐘域,輸入信號也是在SPI_Ref_Clk域中同步并進行分析。

從機模式在SPI_Ref_Clk時鐘域中檢測一個字(word)的開始,有兩種情況:

啟用控制器時檢測:如果在SS無效時使能了控制器,控制器將忽略數據,等待SCLK變為非活躍狀態,然后捕獲數據。SCLK不活躍時,控制器在SPI_Ref_Clk域中計數,達到設定值(可編程)時,便假定有一個新字(word)。

SS有效時檢測:啟用控制器且SS被檢測為無效時,當SS轉為有效后,下一個SCLK的活躍邊沿便被控制器認為是一個字的開始。

一個“開始”必須在至少4個SPI_Ref_Clk周期內保持有效狀態。在外部主機“馬上”開始數據傳輸的時候,才使能從機模式,這樣會有概率(很小)發生同步錯誤的情況。可以采用如下措施避免這個問題:

在使能從機模式后,確保至少10個SPI_Ref_Clk周期后外部主機才開始數據傳輸;

確保在使能了外部的主機模式后,再使能從機模式;

確保當使能從機時SS輸入信號為無效狀態。

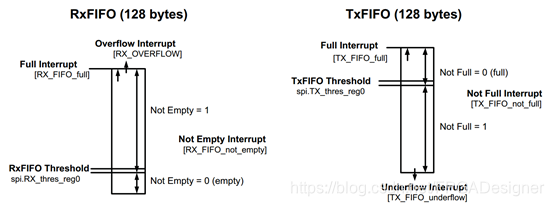

控制器的FIFO

Rx和Tx FIFO各有128個字節深度。如果控制器試圖將數據送入到一個已滿的RxFIFO,該數據將會丟失,同時設置溢出(overflow)標志。如果TxFIFO已滿,則不要向其寫入更多數據。當TxFIFO的級別高于TxFIFO_Not_FULL的閾值級別時,會保持Tx_FIFO_FULL狀態。如果我們向已滿的TxFIFO寫數據,該數據會丟失且不會發出任何指示(比如中斷)。

上圖展示兩個FIFO各自的中斷情況。

SPI協議詳解

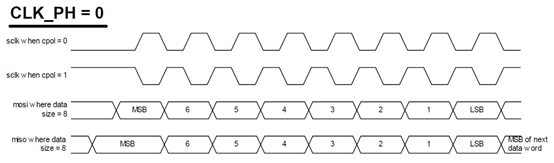

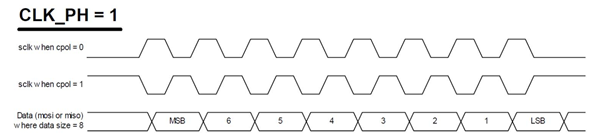

主機模式下,控制器支持幾種不同的I/O信號關系,4種時鐘相位(CLK_PH)和極性(CLK_POL)的配置組成了通常所說的4種SPI模式。不同的配置參數主要影響SCLK的活躍邊沿、SS的選擇、SCLK的空閑狀態。具體見下表(高電平無效,低電平有效):

如果以前沒有專門了解過SPI協議,看到這個表可能頭都要大了,我們結合下面的解釋和時序圖加深自己的理解(表頭,將上表參數部分看作4×4的矩陣)。

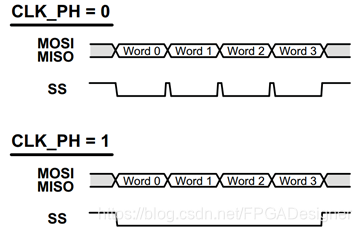

當CLK_PH=0時,設定的一段時間內,主機設備自動驅動SS輸出為無效狀態(表[3,1]與[3,2]),最小保持2個SPI_Ref_Clk的周期。兩個字間有最短3個SPI_Ref_Clk周期的延遲,這段延遲內卸載(unload)TxFIFO,為下一次并-串轉換做準備,并將SS切換為無效。

當CLK_PH=1時,字之間的SS輸出信號仍保持有效狀態(表[3,3]和[3,4])。兩個字之間的最小延遲可達1個SPI_Ref_Clk周期,同樣會卸載(unload)TxFIFO,為下一次并-串轉換做準備。

下面看CLK_PH=0時的時序圖。以POL=0為例,“驅動邊沿”是指下降沿(表[1,1])處驅動bit間的切換,“采樣邊沿”是指上升沿處(表[2,1])對信號采樣,此時正好位于數據中央。POL=1時,恰好相反(表[1,2]和[2,2])。

下面看CLK_PH=1的時序圖,情況如上類似(表[1,3]、[1,4]、[2,3]、[2,4])。

SPI還有一種“背靠背(back-to-back)”傳輸模式,即連續傳輸字(word),時序見下圖:

看到CLK_PH=0時,字間SS會有短暫的無效狀態;而CLK=1時,SS持續有效。

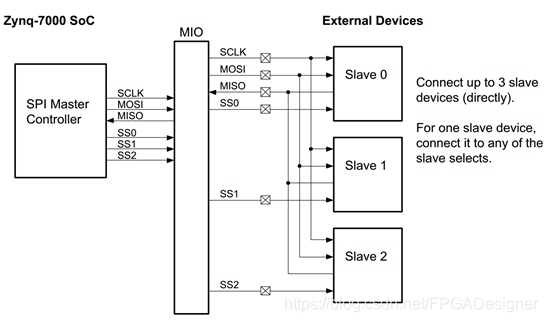

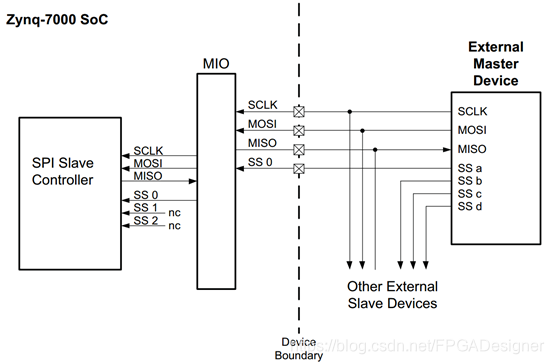

SPI信號路由

SPI接口信號可以路由到MIO管腳(50MHz)或EMIO接口(25MHz)。使用EMIO接口時,用戶必須在PL部分創建邏輯,將SPI EMIO接口直接連到PL管腳上的I/O Buffer。

用于可以連接每個SPI控制器和外部的SPI從機設備。在主機模式下,如果不使用SS0信號,則必須將其連接到VCC。這是因為主機模式下,控制器會檢查這個信號以判斷是否是多主機模式。如果SS0為邏輯低,控制器會假設為多主機模式,發出命令前會一直等待SS0變為無效。

路由到MIO的主機模式框圖如下,SS信號直接相連的情況下,最多可以連接3個從機設備:

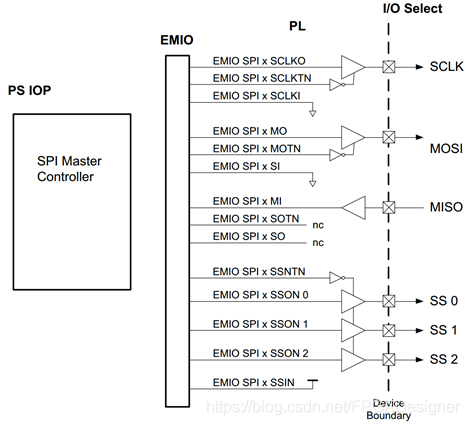

路由到EMIO的主機模式框圖如下,確保使能了PS-PL電壓電平轉換器,且為PL提供電源和配置,否則SPI控制器將無法工作:

路由到MIO的從機模式框圖如下:

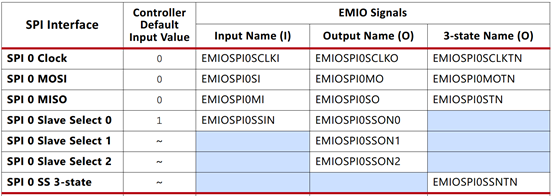

將SPI接口路由到MIO接口時的配置很簡單,配置ZYNQ IP核,選擇MIO管腳即可。路由到EMIO則有點麻煩,很多人看到這么多信號可能都懵了,我的天,不應該只有簡簡單單的SCLK、MOSI、MISO、SS0、SS1、SS2共6根線就夠了嗎?

在EMIO接口上可用的SPI I/O接口信號雖然只有6“種”,但絕不是6“根”,很多信號都有3態接口。以SPI 0為例,14根信號如下表所示(一般我們不會全部用到):

原文鏈接:https://blog.csdn.net/FPGADesigner/article/details/88932544

-

控制器

+關注

關注

114文章

16959瀏覽量

182867 -

接口

+關注

關注

33文章

8932瀏覽量

153188 -

SPI

+關注

關注

17文章

1775瀏覽量

94658 -

總線

+關注

關注

10文章

2947瀏覽量

89332 -

Zynq

+關注

關注

10文章

614瀏覽量

48012

原文標題:SPI控制器簡介

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何在zynq中將GPIO轉換為SPI控制器?

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

《振南電子STM32視頻教程》第十一講:SPI總線

基于FPGA 的SPI Flash 控制器設計及驗證

創建主/從SPI接口的兩種方法詳談

淺談Zynq Qspi控制器的三種模式

淺談Zynq實現SPI接口設計

Zynq UltraScale+ MPSoC LPDDR器件中硬化控制器的性能介紹

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

基于SPI的EEPROM控制器設計與實現

瑞蘇盈科Xilinx Zynq UltraScale+ MPSoC無人機控制器

詳解Zynq中的SPI控制器

詳解Zynq中的SPI控制器

評論