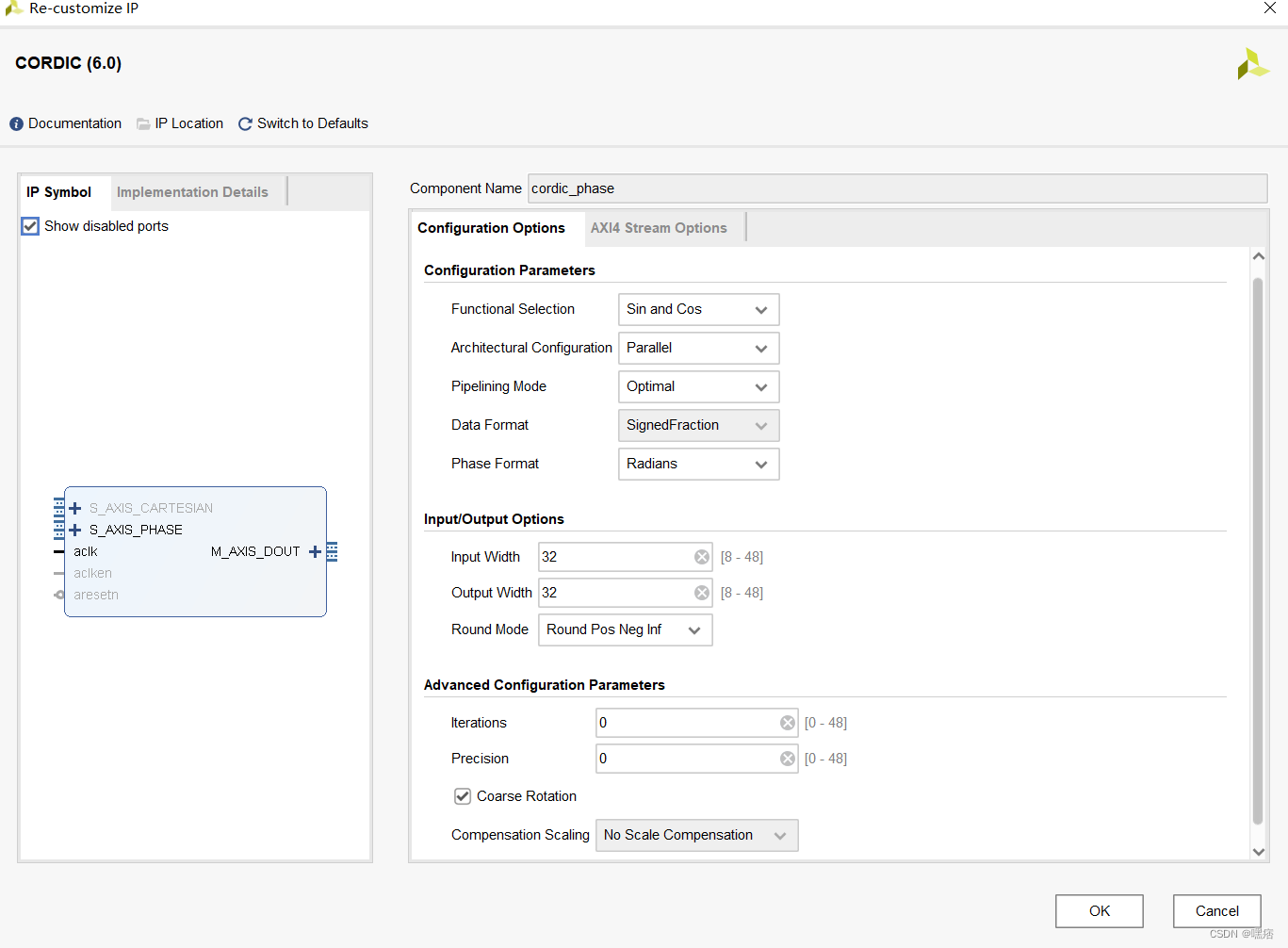

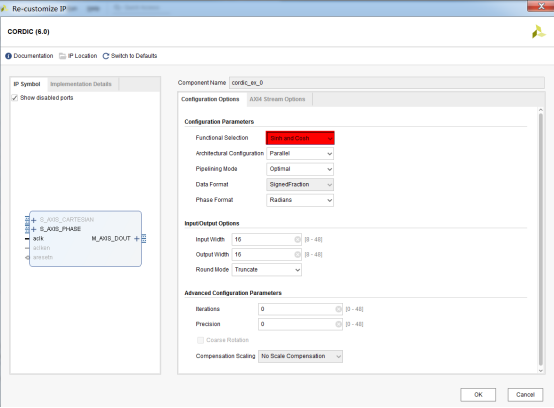

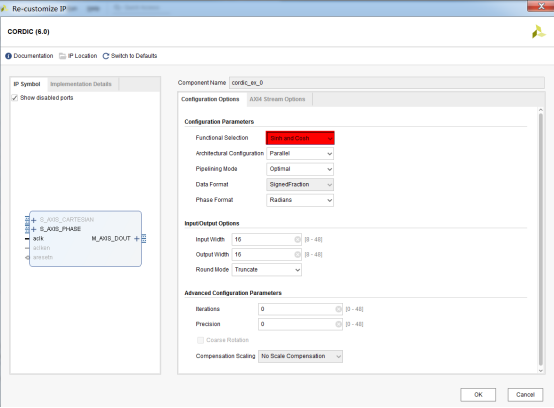

IP核的配置

其輸入為角度值。

1. 功能選擇為sin and cos(輸出時(shí)sin在高32位,cos在低32位)

2.Architectural Configuration選擇為并行模式,具有單周期數(shù)據(jù)吞吐量和較大的硅面積。具有并行結(jié)構(gòu)配置的CORDIC核使用移位相加子級(jí)數(shù)組并行實(shí)現(xiàn)這些移位相加操作。該并形電路的實(shí)現(xiàn)規(guī)模與(內(nèi)部精度 * 迭代次數(shù))成正比。

3.Pipelining Mode選擇Optimal:在不使用任何額外LUT的情況下,以盡可能多的使用流水線級(jí)數(shù)。

4.Signed Fraction:有符號(hào)分?jǐn)?shù)(默認(rèn)格式)。X和Y的輸入和輸出表示為整數(shù)寬度為2位的二進(jìn)制補(bǔ)碼定點(diǎn)數(shù)。這里輸入的角度值是第一位表示正負(fù),第二位和第三位表示整數(shù)部分,后29位表示小數(shù)部分,范圍[-π,π]。輸出的值是第一位表示正負(fù),第二位表示整數(shù)部分,后30位表示小數(shù)部分,范圍[-1,1]。

5.Radians:弧度制,范圍[-Pi,Pi]。相位將表示位整數(shù)寬度位3位的二進(jìn)制補(bǔ)碼定點(diǎn)數(shù)。

6.Round Mode:Pos Neg Infinity:類(lèi)似 round(x)。 四舍五入。

7.Iterations

控制要執(zhí)行的內(nèi)部 add-sub 迭代次數(shù)。

當(dāng)設(shè)置為0時(shí)(默認(rèn)情況),執(zhí)行的迭代次數(shù)由輸出的所需精度決定,自動(dòng)確定迭代次數(shù),通常為輸出位寬。

手動(dòng)設(shè)置時(shí),開(kāi)方設(shè)置比較復(fù)雜,參照手冊(cè)描述。其他情況下,對(duì)于位寬大于13的,應(yīng)加1。

8.Precision

控制要執(zhí)行的內(nèi)部 add-sub 計(jì)算精度。

當(dāng)設(shè)置為0時(shí)(默認(rèn)情況),根據(jù)輸出所需精度和內(nèi)部迭代次數(shù)自動(dòng)確定內(nèi)部精度。

設(shè)置為( Input _ Width + Output _ Width + log2 ( Output _ Width) )時(shí),無(wú)論輸入幅度如何,輸出相位都精確到全輸出寬度。

9.Coarse Rotation

控制粗旋轉(zhuǎn)模塊的實(shí)例化。作用于:Vector rotation, Vector translation, Sin and Cos, and ArcTan 功能。

關(guān)閉粗旋轉(zhuǎn)模塊,輸入輸出范圍限制在第一象限( - Pi / 4至+ Pi / 4)。

開(kāi)啟粗旋轉(zhuǎn)模塊,粗旋轉(zhuǎn)通過(guò)將輸入樣本旋轉(zhuǎn)到第一象限,反向旋轉(zhuǎn)輸出樣本回到合適的象限,將CORDIC運(yùn)算范圍擴(kuò)展到全圓。

10.Compensation Scaling

控制用于補(bǔ)償CORDIC幅度縮放的補(bǔ)償縮放模塊。作用于:Vector Rotation and Vector Translation 功能。當(dāng)選擇不補(bǔ)償時(shí)輸出是乘了倍數(shù)Z的。對(duì)于 Sin, Cos, Sinh, Cosh, ArcTan, ArcTanh and Square Root 無(wú)影響,應(yīng)設(shè)置為 No Scale Compensation。

modulesincos_test( input clk, input start, input[31:0] pha_in, outputwire over, outputwire[31:0] sin_out, outputwire[31:0] cos_out ); cordic_sincos my_sincos ( .aclk(clk), // input wire aclk.s_axis_phase_tvalid(start), // input wire s_axis_phase_tvalid.s_axis_phase_tdata(pha_in), // input wire [31 : 0] s_axis_phase_tdata.m_axis_dout_tvalid(over), // output wire m_axis_dout_tvalid.m_axis_dout_tdata({sin_out,cos_out}) // output wire [63 : 0] m_axis_dout_tdata); endmodule

`timescale1ns / 1psmoduletb_sincos();regclk =0;regstart =0;reg[31:0] pha_in=0;wireover;wire[31:0] sin_out;wire[31:0] cos_out;always#4.069clk=~clk;initialbegin #10 start<=1;?// ? ? ? pha_in<=32'b00111001000000000000000000000000;? ? ? ? ?pha_in<=32'b01010000111110001000101101100010; ? ?endsincos_test my_sincos_test ( ? ?.clk? ? ? ? ? (clk), ? ?.start? ? ? ? (start), ? ?.pha_in? ? ? ?(pha_in), ? ?.over? ? ? ? ?(over), ? ?.sin_out? ? ? (sin_out), ? ?.cos_out? ? ? (cos_out) );endmodule

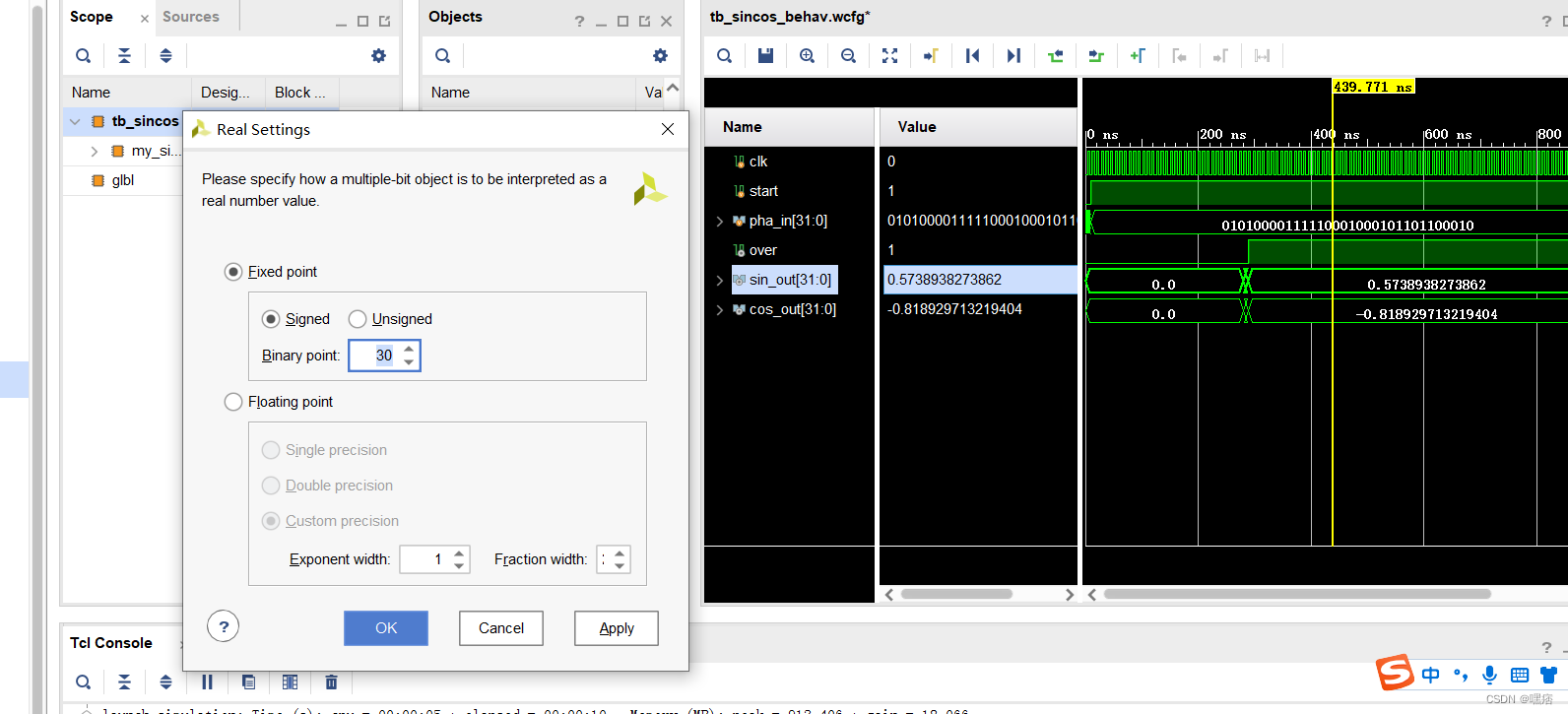

仿真結(jié)果:

-

模塊

+關(guān)注

關(guān)注

7文章

2783瀏覽量

49502 -

IP核

+關(guān)注

關(guān)注

4文章

338瀏覽量

50439 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68192

原文標(biāo)題:vivado IP核 cordic 中sin和cos的計(jì)算

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx FPGA入門(mén)連載73:波形發(fā)生器之IP核CORDIC(正弦波)配置

請(qǐng)問(wèn)8335電機(jī)套件程序中sin cos怎么計(jì)算

LabVIEW FPGA CORDIC IP核的arctan使用方法

控制函數(shù)中的cos和sin函數(shù)數(shù)值的獲取,

Vivado生成IP核

xilinx vivado調(diào)用cordic IP核進(jìn)行實(shí)現(xiàn)時(shí)報(bào)錯(cuò)多重驅(qū)動(dòng)?

sin/cos發(fā)生器,sin/cos信號(hào)產(chǎn)生電路圖

使用Xilinx CORDIC IP核生成正、余弦波

了解Vivado中IP核的原理與應(yīng)用

vivado調(diào)用IP核詳細(xì)介紹

Vivado中xilinx_courdic IP核的使用方法

Vivado中xilinx_courdic IP核(求exp指數(shù)函數(shù))使用

Xilinx Vivado DDS IP使用方法

vivado IP核cordic中sin和cos的計(jì)算

vivado IP核cordic中sin和cos的計(jì)算

評(píng)論