一、背景

Vivado中時序分析工具默認會分析設計中所有時鐘相關的時序路徑,除非時序約束中設置了時鐘組或false路徑。使用set_clock_groups命令可以使時序分析工具不分析時鐘組中時鐘的時序路徑,使用set_false_path約束則會雙向忽略時鐘間的時序路徑

使用-group參數可以將一個時鐘設置到多個時鐘組中,如果時鐘組中沒有時鐘,則時鐘組為空組。只有至少兩個組都是非空組,為有效組時set_clock_groups約束才有效。如果只有一個組有效,其他組是空的,流程將會報錯。

二、時鐘間關系

2.1 時鐘關系分類

兩個時鐘的關系可以是同步時鐘,異步時鐘,非擴展時鐘。

同步時鐘: 兩個時鐘的相位關系是可預知的,常見的是兩個時鐘來源于相同的根時鐘或者共同的周期,如生成時鐘和主時鐘。

異步時鐘:當兩個是時鐘的相位關系不可預知時,則為異步時鐘,例如來源兩個晶振的時鐘,通過不同的輸入端口進入到FPGA內部,無法知道兩者的相位關系。

非擴展時鐘:當兩個時鐘在1000個周期內仍無無法找到共同的邊沿,在這種情況下,最差的setup關系在超過1000個周期上,但是時序分析工具將無法確認這是最差的情況。典型的例子是兩個奇數倍分頻的時鐘,如clk0和clk1都是由MMCMs產生的生成時鐘,周期分別為5.125ns和6.666ns。它們的上升沿在1000個周期內不存在重合。時序分析工具有一個0.01ns的setup路徑裕量,盡管兩個時鐘有已知的相位關系,但它們的波形使得無法進行正確的時序分析。

異步時鐘中,slack值可以按常規方法計算,但計算出的值不一定正確。因此,非擴展時鐘通常作為異步時鐘。

2.2 時鐘關系查看

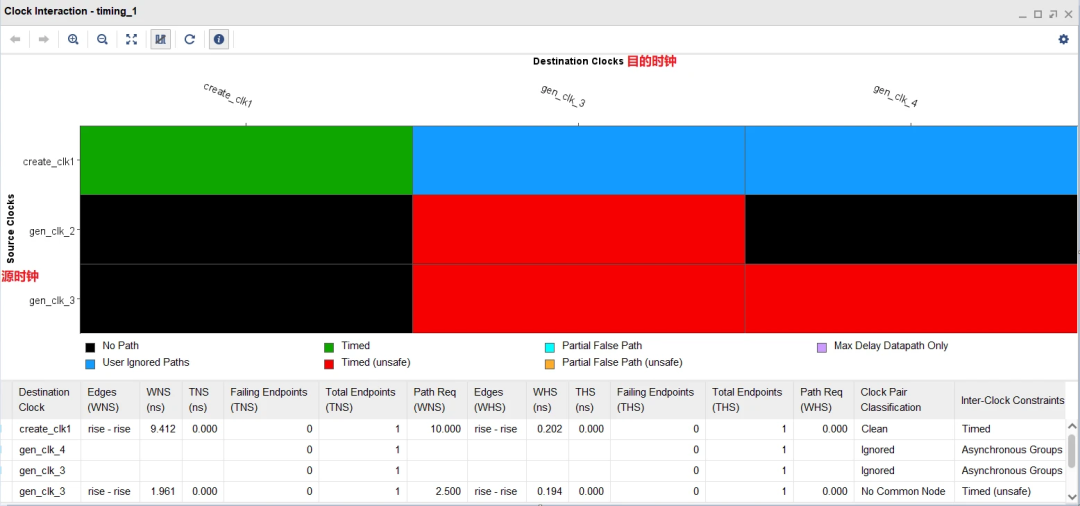

時鐘Vivado中Report Clock Interaction可以查看時鐘間的關系

下圖顏色方塊中,橫坐標表示目的時鐘,縱坐標表示源時鐘,黑色No path表示不存在時序路徑,藍色User ignored Paths為用戶設置了不分析的約束,紅色Timed(Unsafe)表示異步時鐘或非擴展的時鐘,顏色塊下方的列表也顯示了時序的詳細信息。

三、異步時鐘組

3.1 優先級

異步時鐘和非擴展時鐘是沒法正確地進行時序分析, 在它們之間的時序路徑在分析時應該使用set_clock_groups進行忽略。相比于其他時序例外的命令,set_clock_groups的優先級最高,如果需要對異步時鐘進行分析,則不能對該時鐘使用set_clock_groups命令。

3.2 使用格式

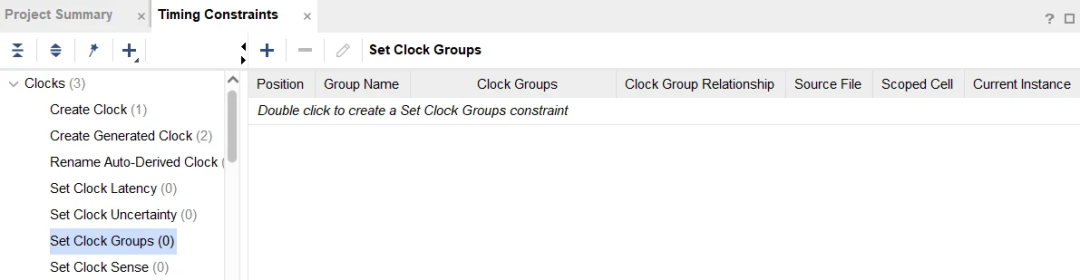

在Timing Constraints窗口中,Clocks列下選擇Set Clock Groups

進入Set Clock Groups界面

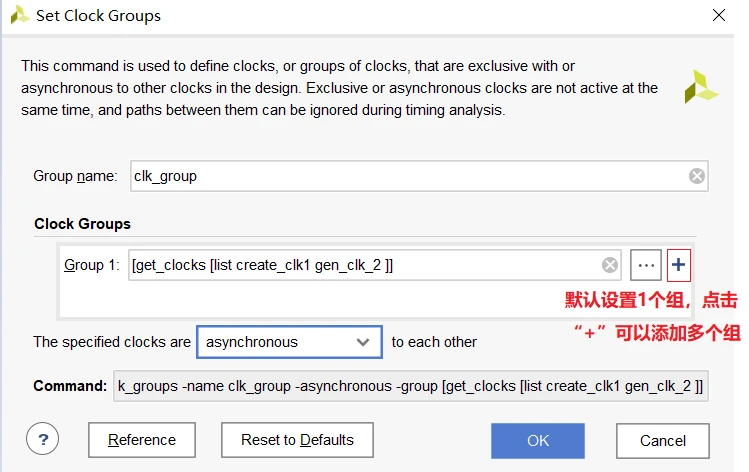

Group name:設置時鐘組的名稱

Group 1: 添加屬于Group 1中的時鐘,點擊最右側的“+”可以設置多個組

The specified clocks are: 設置時鐘組里的時鐘與其他時鐘的關系,可為asynchronous,logically exclusive,physically exclusive。

-asynchronous:約束為異步時鐘組

-logically_exclusive:約束為邏輯互斥的時鐘組

-physically_exclusive:約束為物理線路互斥的時鐘組,設計中不能同時存在,最終表現的效果和-logically_exclusive是相同的。

約束命令示例:

set_clock_groups -name clk_group -asynchronous -group[get_clocks{create_clk1 gen_clk_2}]

3.3 asynchronous和exclusive

參數asynchronous表示創建異步時鐘組,使用場景如數據在不同速率的時鐘間通過FIFO進行傳輸時,使用異步時鐘組隔離時序關系。

參數exclusive表示時鐘組里的時鐘為互斥關系,例如,同一個節點中存在多個時鐘,當同一時間內只能一個時鐘生效,常用在時鐘多路復用上。

3.4 結果示例

以設計中存在4個時鐘clk1,clk2,clk3,clk4為例,時鐘之間均存在可分析的時序路徑。對時鐘進行不同的時鐘組約束,約束后的分析結果如下,Y表示進行時序分析,N表示不進行時序分析,參數使用asynchronous。

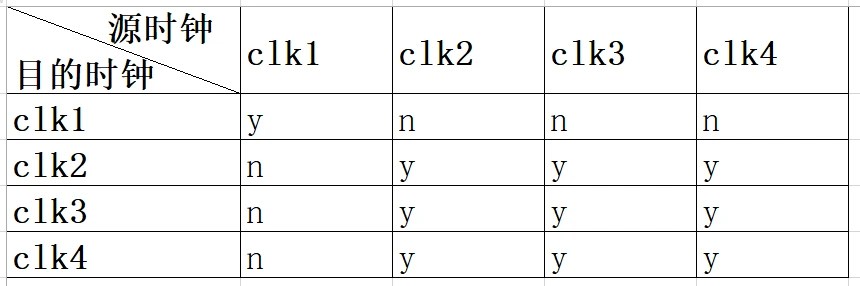

a)場景1:

set_clock_groups -name clk_group -asynchronous -group[get_clocksclk1]

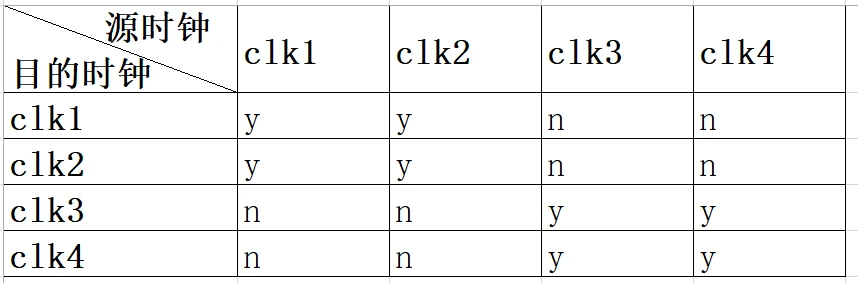

b)場景2

set_clock_groups -name clk_group -asynchronous -group[get_clocks{clk1 clk2}]

時鐘組內部的時鐘間進行時序分析,和外部的時鐘不會進行時序分析

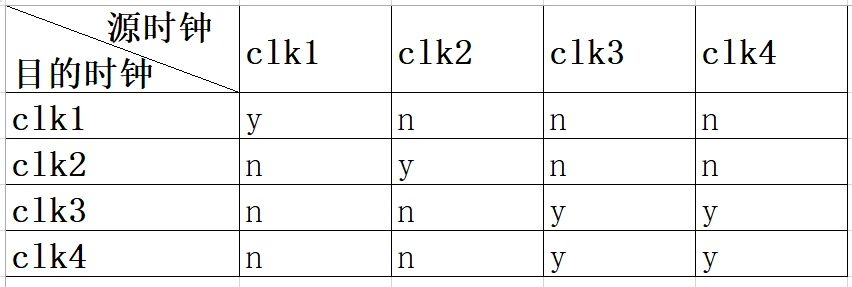

c)場景3

set_clock_groups -name clk_group -asynchronous -group[get_clocksclk1] -group[get_clocksclk2]

設置多個groups時,groups之間的clk不會進行時序分析

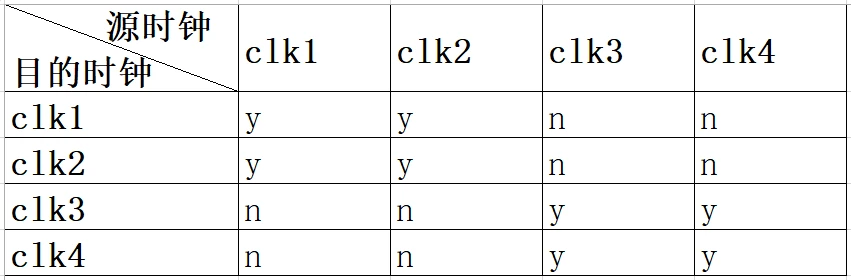

d)場景4

set_clock_groups -name clk_group -asynchronous -group[get_clocks{clk1 clk2}] -group[get_clocks{clk3 clk4}]

設置多個group時,group內部的時鐘間會進行時序分析,group間不會進行時序分析

總結:set_clock_group中group內部的時鐘只能組內間進行分析,不能跨組或與非約束中的時鐘進行時序分析

-

命令

+關注

關注

5文章

726瀏覽量

22666 -

時序約束

+關注

關注

1文章

118瀏覽量

13617 -

Vivado

+關注

關注

19文章

828瀏覽量

68192

原文標題:FPGA時序約束之設置時鐘組set_clock_groups

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA時序約束之衍生時鐘約束和時鐘分組約束

Xilinx FPGA編程技巧之常用時序約束詳解

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA實戰演練邏輯篇56:VGA驅動接口時序設計之3時鐘約束

FPGA中的時序約束設計

FPGA時序約束之設置時鐘組

FPGA時序約束之設置時鐘組

評論