概述

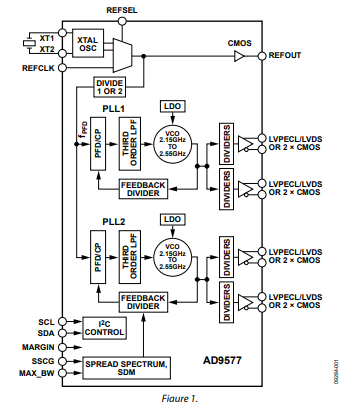

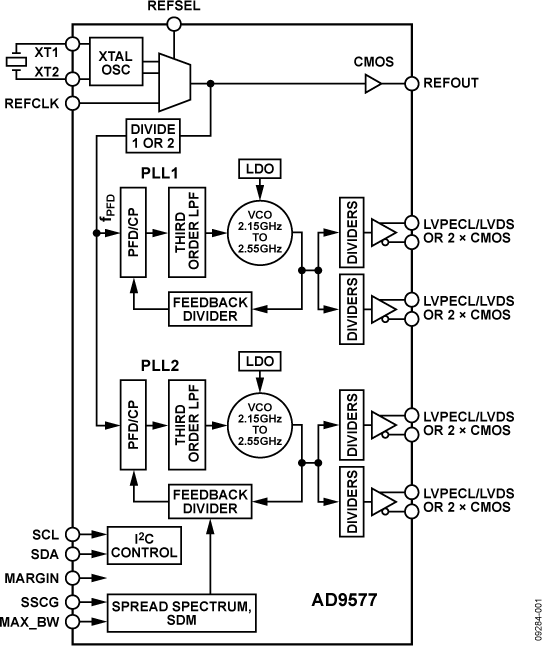

AD9577既提供一個多路輸出時鐘發生器功能,又帶有兩個片上鎖相環內核PLL1和PLL2,專門針對網絡時鐘應用而優化。PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現較高的網絡性能。PLL具有I^2^C 可編程輸出頻率和格式。小數N分頻PLL可支持擴頻時鐘功能,降低EMI輻射的峰值功率。兩個PLL均可支持頻率余量微調功能。

數據表:*附件:AD9577帶雙路PLL、擴頻和余量微調功能的時鐘發生器技術手冊.pdf

第一個整數N分頻PLL部分(PLL1)由一個鑒頻鑒相器(PFD)、一個電荷泵(CP)、一個低噪聲電壓控制振蕩器(VCO)、一個可編程反饋分頻器和兩個獨立可編程輸出分頻器組成。通過將外部晶振或基準時鐘連接至REFCLK引腳,可將最高達637.5 MHz的頻率同步至輸入基準。針對所需輸出速率,每個輸出分頻器和反饋分頻器的比率可以是工廠設定或I^2^C 編程設定。

第二個小數N分頻PLL(PLL2)內置一個可編程模塊,可合成基準頻率小數倍的VCO頻率。針對所需輸出速率(最高達637.5 MHz),每個輸出分頻器和反饋分頻器的比率可以通過工廠編程設定。這個小數N分頻PLL還可在整數N分頻模式下工作以充分降低抖動。

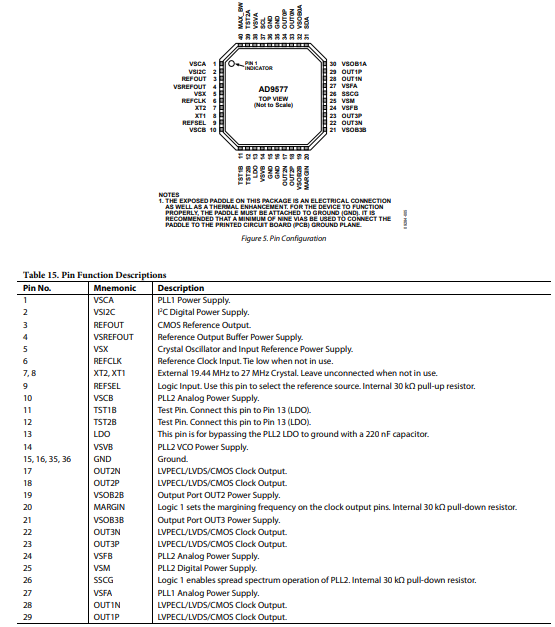

最多四個差分輸出時鐘信號可配置成LVPECL或LVDS信號傳輸格式。每個輸出對也可配置用于最多八個CMOS輸出。支持這類格式的組合。無需外部環路濾波器元件,從而節約了寶貴的設計時間和電路板空間。AD9577提供40引腳6 mm × 6 mm LFCSP封裝,采用3.3 V單電源供電,工作溫度范圍為-40℃至+85°C。

應用

特性

- 完全集成雙路PLL/VCO內核

- 1個整數N分頻和1個小數N分頻PLL

- 連續頻率范圍:11.2 MHz至200 MHz

-- 提供200 MHz至637.5 MHz的大多數頻率 - PLL1相位抖動

(12 kHz至20 MHz):

460 fs rms(典型值) - PLL2相位抖動(12 kHz至20 MHz)

- 整數N分頻模式:470 fs rms(典型值)

- 小數N分頻模式:660 fs rms(典型值)

- 輸入晶體或基準時鐘頻率

- 擴頻向下擴頻 [0, ?0.5]%

- 2引腳控制的頻率分布圖余量微調

- 集成環路濾波器

- 欲了解更多特性,請參考數據手冊

框圖

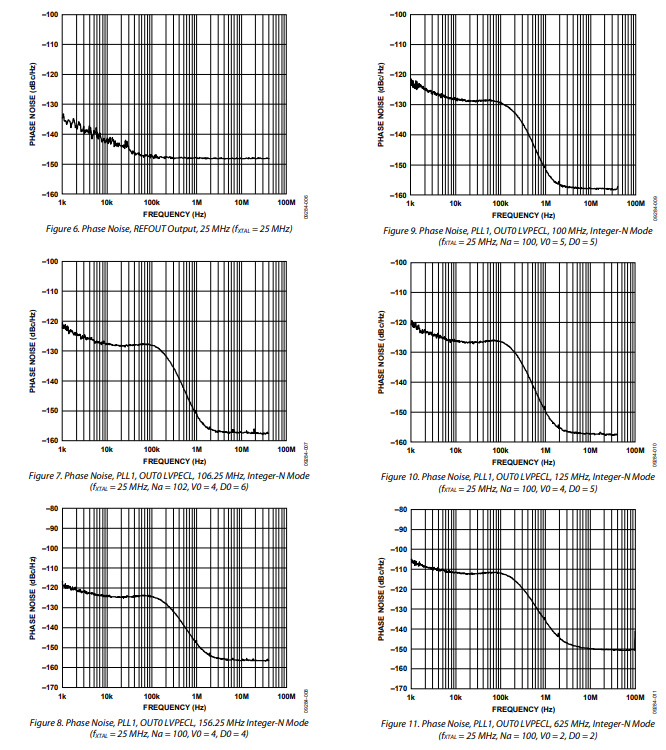

引腳配置描述

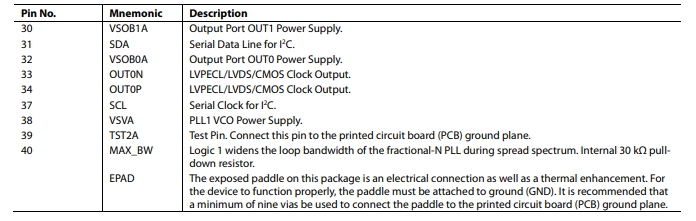

典型性能特征

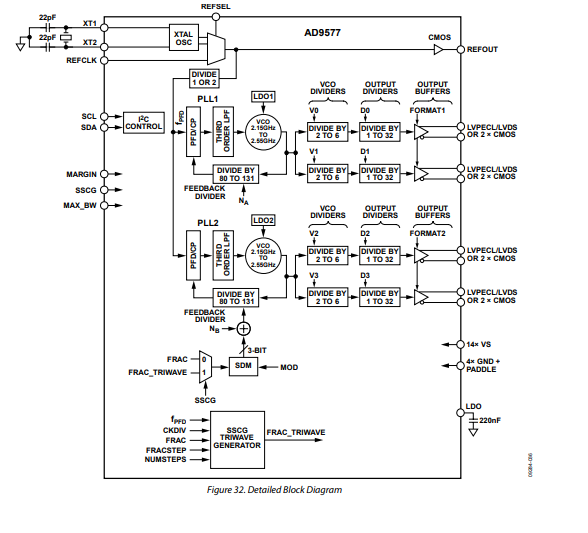

詳細框圖

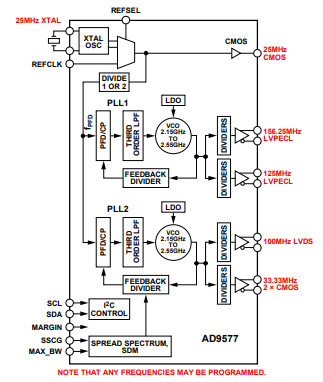

示例應用程序

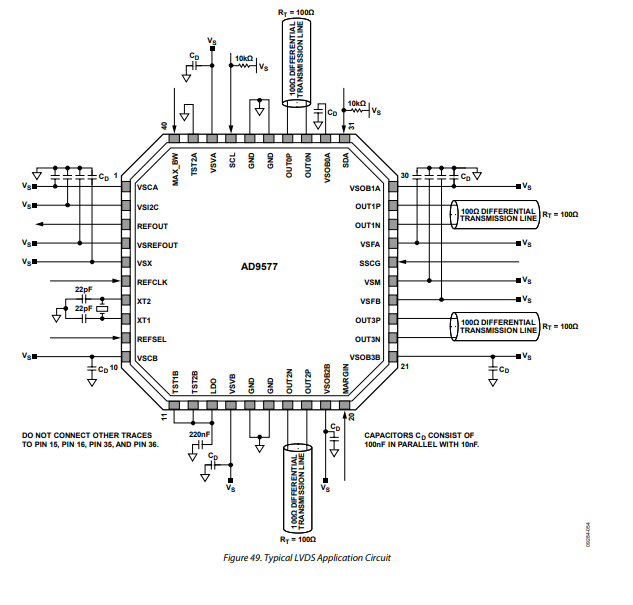

典型應用電路

-

發生器

+關注

關注

4文章

1395瀏覽量

62504 -

時鐘

+關注

關注

11文章

1879瀏覽量

132840 -

AD9577

+關注

關注

0文章

4瀏覽量

10145

發布評論請先 登錄

基于FPGA 的新的DDS+PLL時鐘發生器

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

雙鎖相環擴頻和冗余時鐘發生器ad9577數據表

AD9577 帶雙路PLL、擴頻和余量微調功能的時鐘發生器

HMC1031:0.1 MHz至500 MHz時鐘發生器,帶整數N PLL數據表

評估低抖動PLL時鐘發生器的電源噪聲抑制

時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

AD9577帶雙路PLL、擴頻和余量微調功能的時鐘發生器技術手冊

AD9577帶雙路PLL、擴頻和余量微調功能的時鐘發生器技術手冊

評論