LMK6 時鐘發(fā)生器 計時 評估板

2024-03-14 23:22:15

CS2200-CP 時鐘發(fā)生器 時鐘定時 mikroBUS? Click? 平臺評估擴展板

2024-03-14 23:11:37

Si5350,Si5351 時鐘發(fā)生器 計時 評估板

2024-03-14 22:30:46

Si5348 時鐘發(fā)生器 計時 評估板

2024-03-14 22:30:44

Si50122-A5 時鐘發(fā)生器 計時 評估板

2024-03-14 22:30:31

ICS501 時鐘發(fā)生器 時鐘定時 mikroBUS? Click? 平臺評估擴展板

2024-03-14 22:03:12

Si5351A 時鐘發(fā)生器 時鐘定時 STEMMA QT 平臺評估擴展板

2024-03-14 20:37:59

,ADC值相差不大,但是采用PLL異步時鐘,復位后有概率ADC采樣值發(fā)生偏差(所以我懷疑復位后ADC時鐘出現(xiàn)了問題)。

補充:問題芯片具體是L431RCT6,我還有一塊L431CCT6的芯片,同樣的配置,同樣的代碼邏輯,ADC采樣值就很準確且穩(wěn)定。

以下是時鐘樹與ADC配置(PLL時鐘)

2024-03-08 07:32:15

電子發(fā)燒友網(wǎng)站提供《CDCE6214超低功率時鐘發(fā)生器數(shù)據(jù)表.pdf》資料免費下載

2024-02-28 15:38:40 0

0 函數(shù)發(fā)生器和信號發(fā)生器是電子工程領域常用的兩種設備,它們在實驗室和工業(yè)制造領域中扮演著重要的角色。盡管兩者在名稱和功能上有一定的相似性,但它們的原理和應用有所不同。本文將詳細探討函數(shù)發(fā)生器和信號

2024-02-23 16:10:50 214

214 國芯思辰SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設備。SYSREF

2024-02-19 09:41:40

時鐘發(fā)生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術,以實現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現(xiàn)小于0.3ps RMS的相位抖動性能

2024-02-04 11:41:14

小視頻,波形不停地在左右抖動,并且整周期的AD采樣值也會發(fā)生相位移動,我們懷疑這個相位波動是導致上層算法出現(xiàn)較大誤差的原因,采用外部信號發(fā)生器做對比試驗誤差則縮小10倍。我們不清楚這個正弦發(fā)生器的內(nèi)部原理,所以想請問一下,問什么會出現(xiàn)相位波動的情況?謝謝

2024-02-04 08:59:00

電子發(fā)燒友網(wǎng)站提供《毫微微時鐘網(wǎng)絡同步器、抖動衰減器和時鐘發(fā)生器RC32112A 數(shù)據(jù)表.pdf》資料免費下載

2024-01-31 10:09:17 0

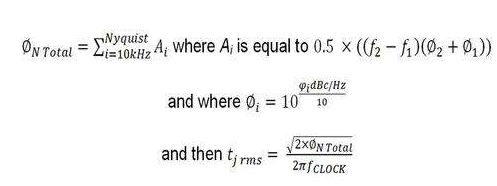

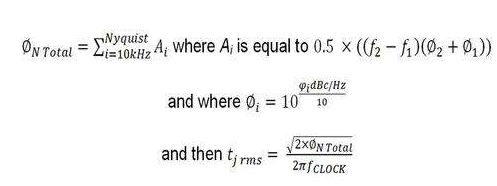

0 會導致晶振的輸出頻率出現(xiàn)一定的不穩(wěn)定性,從而影響到系統(tǒng)的時鐘同步和信號處理。相位抖動常常以皮克-到-皮克的相位偏移量來衡量,通常以ps級別或fs級別來表示。相位抖動在通信系統(tǒng)、時鐘系統(tǒng)和高精度測量設備中都是非常重要

2024-01-25 13:51:07 126

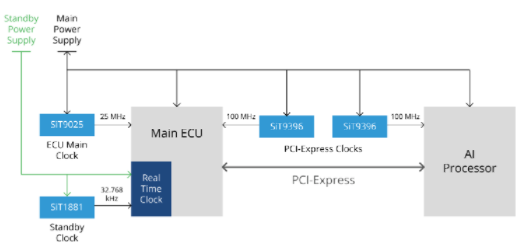

126 ? ? ? ?RS2CG5705B是一款符合PCI Express 3.0和以太網(wǎng)要求的擴頻時鐘發(fā)生器。該電路用于PC或嵌入式系統(tǒng),以顯著減少電磁干擾(EMI)。RS2CG5705B提供

2024-01-25 09:41:32 0

0 RS2CG5705B是一款符合PCI Express 3.0和以太網(wǎng)要求的擴頻時鐘發(fā)生器。該電路用于PC或嵌入式系統(tǒng),以顯著減少電磁干擾(EMI)。RS2CG5705B提供4對差分(HCSL)或

2024-01-24 17:31:16

波特率發(fā)生器是一種用于控制串行數(shù)據(jù)通信速率的設備,它可以生成特定波特率的時鐘信號。在嵌入式系統(tǒng)、通信設備和計算機硬件中,波特率發(fā)生器的使用十分常見。波特率發(fā)生器通常使用定時器來實現(xiàn)時鐘信號的生成

2024-01-24 09:56:20 265

265 產(chǎn)品介紹:斯坦福數(shù)字延遲發(fā)生器DG535美國SRS/DG535 4通道數(shù)字延遲/脈沖發(fā)生器詳細說明規(guī)格時滯頻道四個獨立的延遲輸出范圍0到999.999,999,999,995秒分辨率5 PS精度

2024-01-20 15:15:32

信號發(fā)生器是一種電子測試儀器,用于產(chǎn)生各種類型的電信號。它可以在實驗室、工廠和其他領域提供標準化的、可重復的信號,用于測試和驗證其他電子設備的性能。信號發(fā)生器的使用方法有很多種,下面將詳細介紹

2024-01-19 14:51:02 402

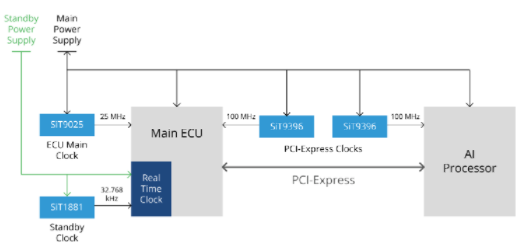

402 核芯互聯(lián)近日發(fā)布了一款專為高性能服務器和計算中心應用打造的支持PCIe 6.0的高性能時鐘發(fā)生器——CLG440。這款產(chǎn)品符合CK440Q標準,旨在滿足下一代服務器和數(shù)據(jù)中心的需求。

2024-01-16 16:09:07 445

445 “核芯互聯(lián)CLG440是一顆專為高性能服務器、計算中心應用推出的支持PCIe 6.0、符合CK440Q標準的高性能時鐘發(fā)生器。

2024-01-16 15:57:40 279

279

電子發(fā)燒友網(wǎng)站提供《FemtoClock2抖動衰減器和時鐘發(fā)生器RC325008A數(shù)據(jù)手冊.pdf》資料免費下載

2024-01-14 10:55:06 0

0 時鐘發(fā)生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術,以實現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現(xiàn)小于0.3ps RMS的相位抖動性能

2023-12-29 09:29:50

時鐘緩沖器芯片時鐘芯片是一種基于PLL的時鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術,以實現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現(xiàn)小于0.3ps RMS的相位抖動性能。可輸出差分

2023-12-28 13:46:09

100fs-300fs之間?

疑問3:是不是使用PLL類型的時鐘發(fā)生器芯片帶來的抖動誤差會比較大?針對14位的ADC輸入差分時鐘有此類型的參考嗎?

模擬輸入部分:

疑問1:參考文檔中使用AD8138差分驅(qū)動芯片

2023-12-22 08:19:31

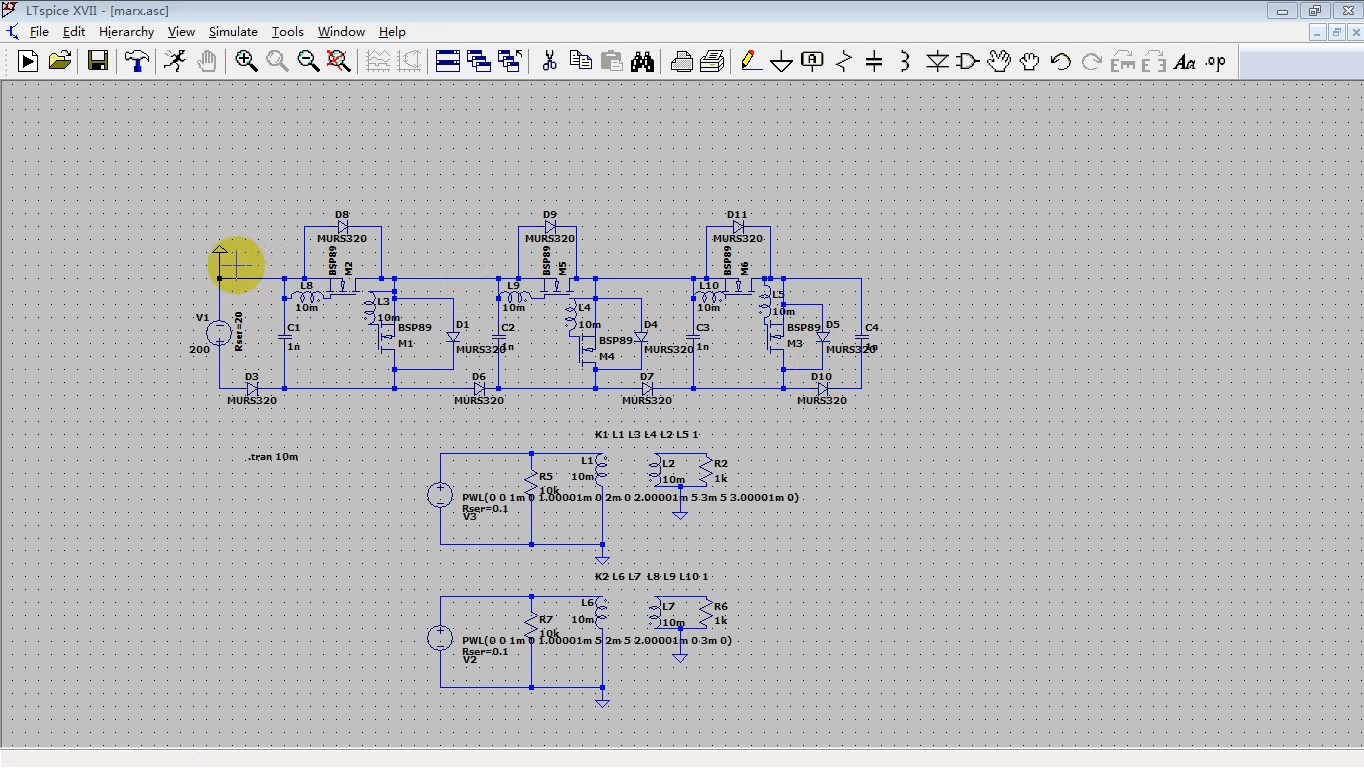

原本打算使用FPGA的PLL輸出端口得到AD的輸入時鐘,但發(fā)現(xiàn)FPGA的時鐘輸出jitter過大(600ps),遠大于得到優(yōu)秀SNR所需的抖動水平

如圖為AD9233的推薦的時鐘輸入方法

2023-12-22 06:29:38

信號發(fā)生器的特點 信號發(fā)生器可以產(chǎn)生哪些波形? 信號發(fā)生器是一種用于產(chǎn)生各種頻率、振幅和波形的電信號的設備。它是電子測試儀器中常用的一種,廣泛應用于科研、生產(chǎn)和教學等領域。信號發(fā)生器具有以下幾個特點

2023-12-21 15:05:42 503

503 信號發(fā)生器如何發(fā)出雙脈沖? 信號發(fā)生器是一種用于產(chǎn)生各種信號波形的儀器。雙脈沖信號是一種特殊的信號波形,由兩個脈沖組成,通常用于測試和測量系統(tǒng)的響應和性能。在本文中,將詳細介紹信號發(fā)生器如何發(fā)出

2023-12-21 15:03:35 442

442 信號發(fā)生器的占空比是什么 信號發(fā)生器占空比怎么設置? 信號發(fā)生器的占空比是指方波波形中高電平和低電平的時間比例。它是描述信號發(fā)生器輸出方波的高低電平持續(xù)時間的一個重要參數(shù)。在數(shù)字電子技術和通信系統(tǒng)

2023-12-21 14:02:26 982

982 直流高壓發(fā)生器的原理 直流高壓發(fā)生器的使用方法 直流高壓發(fā)生器有自動保護嗎? 直流高壓發(fā)生器是一種能夠產(chǎn)生高電壓直流輸出的設備。其原理是基于電子器件的整流和倍壓原理。下面將詳細介紹直流高壓發(fā)生器

2023-12-20 15:01:33 508

508 AC1571 是用于 5G 基站應用的基于 PLL的時鐘發(fā)生器,該芯片采用全數(shù)字鎖相環(huán)技術,以實現(xiàn)最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應用場景:· 無線基站·

2023-12-12 14:25:17

83650BAgilent 83650B信號發(fā)生器,HP-83650B 50G信號發(fā)生器|10MHz至50GHz美國安捷倫Agilent 惠普HP產(chǎn)品規(guī)格 提供+20dbm

2023-12-11 11:00:38

Agilent安捷倫E4432B ESG-D系列數(shù)字 RF 信號發(fā)生器, 3 GHz帶寬。安捷倫E4432B信號發(fā)生器/Agilent E4432B特點250 kHz 至 3 GHz 頻率范圍RF

2023-12-07 14:39:09

的時鐘發(fā)生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發(fā)生器。然而,如果不慎重考慮時鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器、動態(tài)范圍和線性度性能可能受到嚴重的影響。...

2023-11-28 14:33:57 0

0 電子發(fā)燒友網(wǎng)站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

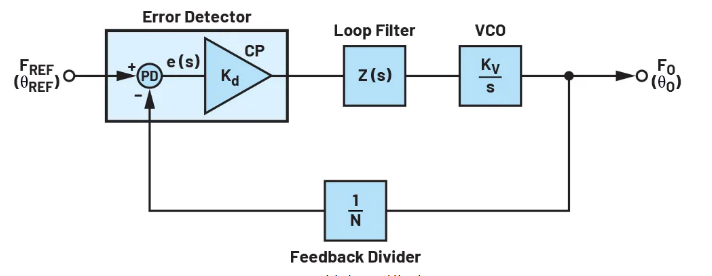

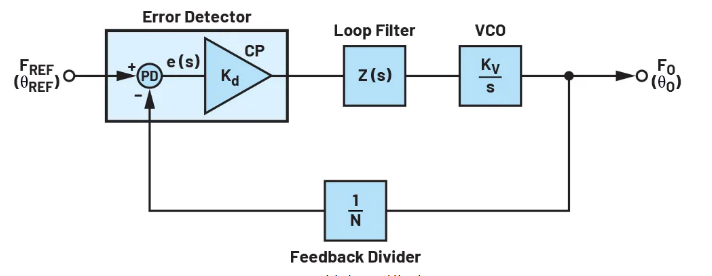

1 RF信號發(fā)生器,尤其是微波頻率的RF信號發(fā)生器,是基于鎖相環(huán)(PLL)合成器產(chǎn)生的。[1]PLL允許從低頻參考產(chǎn)生穩(wěn)定的高頻。圖1給出了一個基本的PLL模型。該模型由一個反饋系統(tǒng)組成,該系統(tǒng)由一個改變輸出頻率的壓控振蕩器、一個比較輸入?yún)⒖碱l率和輸出頻率的誤差檢測器以及分頻器組成。

2023-11-23 15:52:52 292

292

靜電放電發(fā)生器原理 靜電放電發(fā)生器的主要用途 靜電發(fā)生器怎么使用? 靜電放電發(fā)生器(Electrostatic Discharge Generator)是一種用于模擬和測試電子器件和系統(tǒng)在靜電放電

2023-11-23 10:07:22 664

664 81110A81110A 脈沖/碼型發(fā)生器|Agilent|安捷倫脈沖信號發(fā)生器|165MHz安捷倫 | Agilent | 惠普 | HP與外部時鐘同步(固定和可變延遲)2ns可變躍變時間,在50

2023-11-16 18:00:00

時鐘合成器和時鐘發(fā)生器是兩種用于產(chǎn)生時鐘信號的電子器件,它們在功能和應用上有一些區(qū)別。

2023-11-09 10:26:56 298

298 時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 892

892

本應用筆記詳細介紹了具有外部VCO的完整12GHz、超低相位噪聲小數(shù)N分頻鎖相環(huán)(PLL)的設計。它由高性能小數(shù)N分頻PLL (MAX2880)、基于運算放大器的有源環(huán)路濾波器(MAX

2023-10-28 14:45:41 6895

6895 ;SI5338Q-B-GMSi5338是一款高性能、低抖動的時鐘發(fā)生器,能夠在設備的四個輸出驅(qū)動器中的每一個上合成任何頻率。這個時間IC能夠更換多達四個不同頻率的

2023-10-17 17:02:33

時鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點是什么?如何用硬件配置pll? 時鐘發(fā)生器是指通過特定的電路設計產(chǎn)生適合各種電子設備使用的時鐘信號的器件。時鐘發(fā)生器由多個部分組成,其中最核心的是鎖相環(huán)

2023-10-13 17:39:50 443

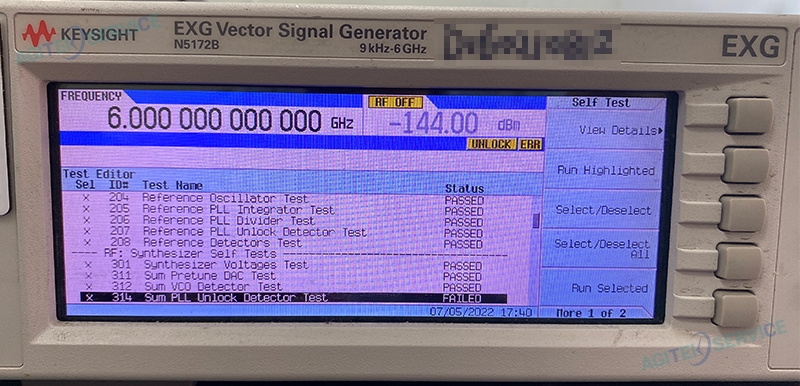

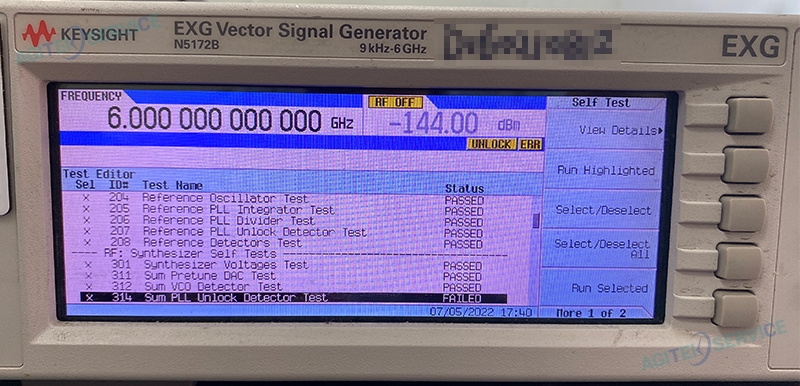

443 維修情況 ? 安捷倫信號發(fā)生器 N5172BMP1報釘頭反接維修 一、信號發(fā)生器 維修型號:安捷倫-N5172B。 二、報修故障:MP1報釘頭反接。 三、故障檢測:700MHz以下信號抖動。經(jīng)過工程師拆機檢測,對內(nèi)部元件進行詳細檢測,發(fā)現(xiàn)儀器射頻板損壞。 四、維修措施:更換射

2023-10-10 17:07:36 492

492

81110A81110A 脈沖/碼型發(fā)生器|Agilent|安捷倫脈沖信號發(fā)生器|165MHz安捷倫 | Agilent | 惠普 | HP與外部時鐘同步(固定和可變延遲)2ns可變躍變時間,在50

2023-09-25 10:32:47

早期制作的電視信號發(fā)生器基本上是由分頻器和門電路構成 ,所用元器件較多、電路復雜 ,自制起來相當麻煩 ,要想增加顯示圖像的種類或改變信號的時序就更困難了。高速單片機的出現(xiàn)給信號發(fā)生器的設計制作帶來

2023-09-19 07:27:23

時鐘發(fā)生器IC 200MHz 2 MSOP10_3X3MM

2023-09-18 15:10:50

時鐘抖動技術適合于各種周期性的脈沖信號,典型的是電力電子設備中的PWM電壓和數(shù)字電路中的時鐘信號。

2023-09-11 10:55:34 502

502

用FPGA的鎖相環(huán)PLL給外圍芯片提供時鐘 FPGA鎖相環(huán)PLL(Phase-Locked Loop)是一種廣泛使用的時鐘管理電路,可以對輸入時鐘信號進行精確控制和提高穩(wěn)定性,以滿足各種應用場

2023-09-02 15:12:34 1319

1319 風冷雕刻電主軸發(fā)生抖動的原因?|深圳恒興隆機電

2023-08-28 11:24:23 325

325

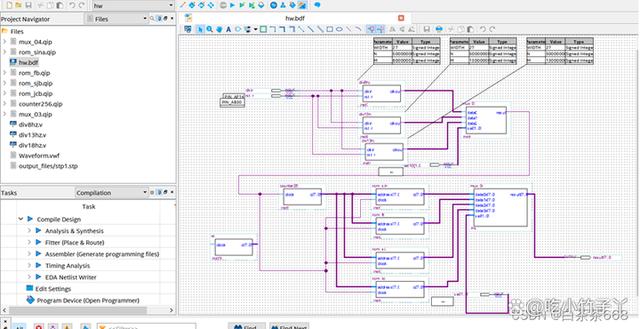

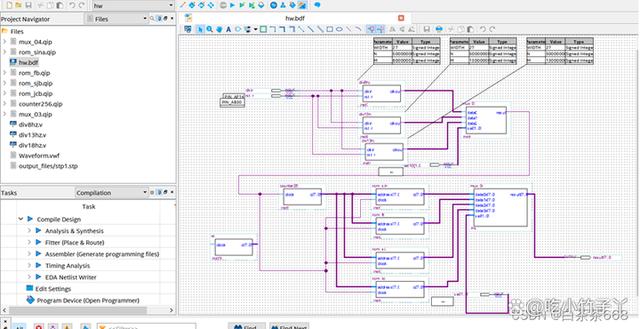

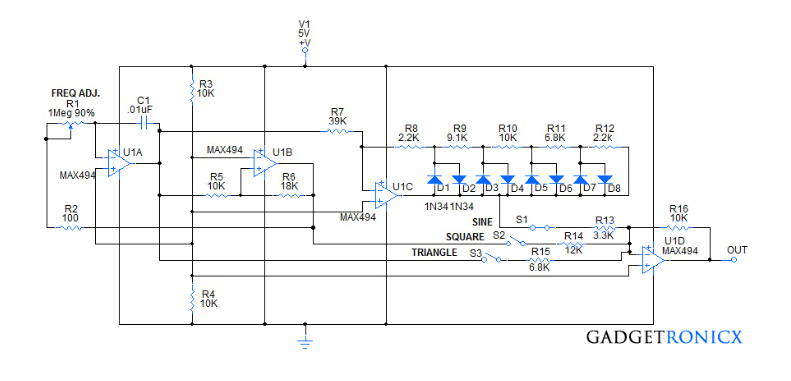

多功能信號發(fā)生器的原理框圖如圖所示。其中,CLKGEN是分頻器,提供的50MHz的主頻率進行分頻,以得到滿足多功能信號發(fā)生器設計需要的時鐘頻率。

2023-08-25 16:34:51 1291

1291

,在很多應用場景中都可以用來構建序列發(fā)生器。本文將介紹使用D觸發(fā)器設計序列發(fā)生器的方法和步驟。 首先,我們需要了解D觸發(fā)器的基本原理和性質(zhì)。D觸發(fā)器是一種時序電路,它可以存儲和延遲一個輸入信號,并在時鐘信號到來時輸出

2023-08-24 15:50:17 2728

2728 簡易信號發(fā)生器的設計? 信號發(fā)生器是一種能夠產(chǎn)生可靠、標準化的交替電流、交流電壓和脈沖的電子設備。在電子測試和測量、頻率標準校準等領域中,信號發(fā)生器都是不可或缺的儀器。然而,通常市面上的信號發(fā)生器

2023-08-24 15:49:50 1159

1159 脈沖發(fā)生器是什么意思?脈沖發(fā)生器怎么使用? 脈沖發(fā)生器是一種電子設備,可以生成不同類型的脈沖信號。這些信號可以被用于各種測試、測量和控制應用,包括電子、通信、無線電、雷達、醫(yī)療等領域。它通常由多個

2023-08-24 15:18:09 2127

2127 脈沖發(fā)生器輸出是1嗎?信號發(fā)生器怎么只發(fā)一個脈沖? 脈沖發(fā)生器和信號發(fā)生器是常用的電子測量儀器,用于產(chǎn)生脈沖和不同類型的信號。在實際應用中,人們通常會誤解它們的作用和輸出特性,因此需要進行詳細的解釋

2023-08-24 15:18:06 882

882 信號發(fā)生器系列波形發(fā)生器你知道多少?虹科信號發(fā)生器系列波形發(fā)生器:波形發(fā)生器是用于產(chǎn)生各種形狀和頻率電信號波形的電子測量儀器。根據(jù)用戶配置,可以輸出不同頻率、振幅、相位和波形的信號。波形發(fā)生器既可以

2023-08-05 08:07:41 1817

1817

型 號:33522B名 稱:波形發(fā)生器,30 MHz,2 通道,具有任意波形生成能力品 牌:是徳(KEYSIGHT)分 類:通用電子測試 > 信號

2023-08-04 16:38:50

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX3625BEUG+T相關產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有MAX3625BEUG+T的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MAX3625BEUG+T真值表,MAX3625BEUG+T管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-07-28 18:45:33

電子發(fā)燒友網(wǎng)為你提供Maxim(Maxim)MAX3625BEUG+相關產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有MAX3625BEUG+的引腳圖、接線圖、封裝手冊、中文資料、英文資料,MAX3625BEUG+真值表,MAX3625BEUG+管腳等資料,希望可以幫助到廣大的電子工程師們。

2023-07-28 18:45:18

產(chǎn)品概況: SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7

2023-07-25 17:06:53

需要。將波形發(fā)生器產(chǎn)生的信號注入到設備中,以便在測試期間進行分析、發(fā)現(xiàn)設備問題或確認正常運行。 4.2 GS/s 采樣率模擬高達 2.1 GHz 的真實信號 2 個 2.0 ps 的標記;RMS

2023-07-12 14:24:57 235

235

需要。將波形發(fā)生器產(chǎn)生的信號注入到設備中,以便在測試期間進行分析、發(fā)現(xiàn)設備問題或確認正常運行。 附加的功能: 一個通道,10 位垂直分辨率 外部時鐘輸入允許抖動插入和同步 10 通道、1 GHz 數(shù)字數(shù)據(jù)生成(選項 03) 實時噪聲生成 支持直接外部時鐘和 10 MHz 參考

2023-07-12 11:28:49 248

248

9ZXL1951D PCIe 時鐘發(fā)生器評估板用戶指南

2023-07-07 19:19:11 0

0 本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 959

959

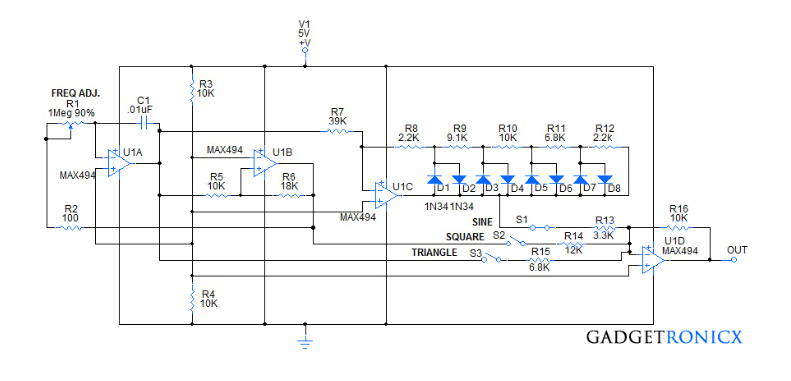

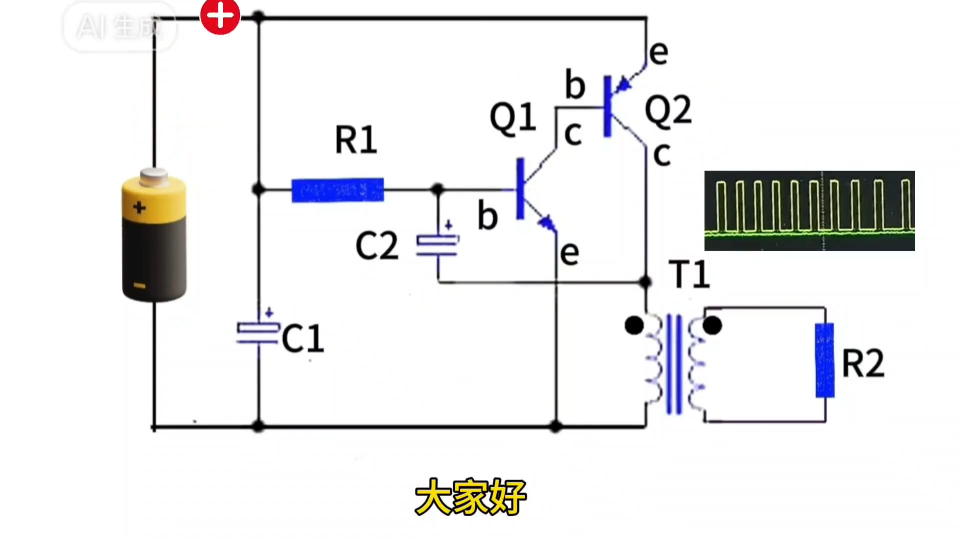

函數(shù)發(fā)生器(又名FG)在許多音頻和模擬電路中廣泛使用。FG能夠生成正弦波、方波、鋸齒波和三角波。但是,沒有多少電子愛好者能夠負擔得起購買FG用于實驗目的。對于那些想要自己構建簡單具有成本效益的函數(shù)發(fā)生器的人來說,這種函數(shù)發(fā)生器電路將派上用場。

2023-07-02 10:41:56 420

420

在本例中,我們將研究如何利用低抖動時鐘發(fā)生器AD9643對雙通道14位250 MSPS ADC進行計時。使用這些特定產(chǎn)品的常見時鐘頻率為9523.245 MHz,因此我們將為AD76使用30.72 MHz基準電壓源(外部振蕩器),并設置內(nèi)部寄存器,為AD9523生成低抖動時鐘輸出。

2023-06-30 16:59:52 798

798

先來聊一聊什么是時鐘抖動。時鐘抖動實際上是相比于理想時鐘的時鐘邊沿位置,實際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實際上,時鐘源例如PLL是無法產(chǎn)生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 1121

1121

? 安捷倫33621A任意波形發(fā)生器 33621A 是安捷倫的任意波形發(fā)生器。任意波形發(fā)生器 (AWG) 是人們用來生成重復或單次電波形的一種電子測試設備。單次波形需要內(nèi)部或外部觸發(fā)源,而重復波形

2023-06-06 15:21:29 648

648

首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1024

1024

) 以及其他通常要求時域抖動規(guī)范(如周期)的應用生成時鐘- 周期和周期抖動。 然而,對于串行解串器 (SerDes)、千兆以太網(wǎng) (GbE)、10 GbE、同步光網(wǎng)絡/同步數(shù)字體系 (SONET/SDH) 和光纖通道等高速接口,情況就不同了。有嚴格的頻域抖動要求。 為了正常運行,這些高速接口依賴于低頻

2023-05-26 22:15:02 1385

1385 無源諧振器和有源振蕩器是眾所周知的定時元件。更復雜的組件包括時鐘發(fā)生器、同步器和抖動衰減器。汽車系統(tǒng)中時序的主要目的是為每個數(shù)字集成電路提供穩(wěn)定的參考,同步大量數(shù)據(jù)的傳輸,并實現(xiàn)V2X和5G通信。

2023-05-04 11:42:28 1025

1025

CLG5908是一顆高性能的任意頻率任意輸出格式通用時鐘發(fā)生器,可以支持1~750M任意頻點輸出,頻率精度 < 0.001 PPM,并且jitter性能優(yōu)越,通常模式下RMS jitter<200fs,同時支持Down-Spread和Center-Spread SSC。

2023-04-23 14:43:12 626

626

) 頻帶內(nèi)和頻帶外 (VCO) 噪聲的影響。基準時鐘發(fā)生器的相位噪聲性能需要在PLL環(huán)路帶寬內(nèi)和帶寬外都表現(xiàn)得很出色,以符合更加嚴格的抖動技術規(guī)格要求。

2023-04-17 10:37:30 357

357

本文討論電源噪聲干擾對基于PLL的時鐘發(fā)生器的影響,并介紹幾種用于評估由此產(chǎn)生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發(fā)生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

時鐘發(fā)生器/PLL頻率合成器 VQFN32_5X5MM_EP 3V~3.6V 683.28MHz

2023-04-06 12:10:37

系統(tǒng)時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1633

1633 斯坦福SRS DG535 延遲發(fā)生器脈沖發(fā)生器產(chǎn)品介紹:斯坦福數(shù)字延遲發(fā)生器DG535美國SRS/DG535 4通道數(shù)字延遲/脈沖發(fā)生器詳細說明規(guī)格時滯頻道四個獨立的延遲輸出范圍0到

2023-04-03 17:54:44

利用運算放大器構成的脈沖序列發(fā)生器和積分器構成三角波發(fā)生器。可是我怎么將匹配器件的參數(shù),調(diào)出三角波的波形呢。現(xiàn)在怎么調(diào)都 沒法弄在線性工作區(qū)。。。。

2023-03-31 13:53:44

KIT EVALUATION MAX MAX3625B

2023-03-30 11:46:01

12 LVPECL/24 CMOS輸出時鐘發(fā)生器,集成2 GHz VCO

2023-03-28 18:26:07

CDCM61002 1:2 超低抖動晶體時鐘發(fā)生器

2023-03-28 18:26:06

時鐘發(fā)生器/PLL頻率合成器 QFN24_4X4MM_EP 3~5.2V 8GHz

2023-03-28 18:26:06

14輸出時鐘發(fā)生器,集成2.0 GHz VCO

2023-03-28 18:12:38

時鐘發(fā)生器 MSOP10 3~3.6V

2023-03-28 12:54:08

嘿,不幸的是,我必須為我的應用程序使用 LVPECL 時鐘發(fā)生器,并且我試圖弄清楚如何最好地將其轉(zhuǎn)換為 DIFF_SYSCLK/DIFF_SYSCLK_B 輸入的 LVDS 電平,這讓我有些困惑。在

2023-03-27 08:00:13

時鐘發(fā)生器/PLL頻率合成器 QFN-24 2.7~5.5V 8GHz 1:1 CMOS CMOS

2023-03-23 05:01:32

結合時鐘發(fā)生器輸出和FTDICHIP-ID TM安全加密狗

2023-03-23 04:59:11

電子發(fā)燒友App

電子發(fā)燒友App

評論