時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll

時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相環PLL(Phase-Locked Loop)電路。PLL是一種閉環反饋電子電路,其基本原理是通過不斷比較輸入信號和產生的時鐘信號之間的相位差來調節輸出信號,使得輸出信號與輸入信號相位同步。PLL的特點包括高精度、輸出紋波小、抗噪聲干擾能力強,并且可以實現頻率倍頻和分頻等功能。

PLL電路由三部分組成:相頻控振蕩器(VCO)、頻率控制電路和相位比較器。其中,相頻控振蕩器是PLL電路的核心部件,它負責產生比輸入信號高若干倍的時鐘信號;頻率控制電路用于控制輸出時鐘頻率,使其與輸入信號的頻率相匹配;相位比較器則用于監測輸入信號和時鐘信號之間的相位差,并將控制信號送至頻率控制電路。PLL還包括一個使能電路,在輸入信號失效時,能夠在一定時間內維持輸出時鐘的頻率和相位。

要用硬件配置PLL,需要按照以下步驟進行:

1.確定輸入信號的頻率范圍和精度。這可以通過測量輸入信號,并根據需要,選擇適當的 PLL 設計參數。

2.確定輸出時鐘信號的頻率范圍和精度。這需要根據所連接的電路要求和具體應用場景選擇。

3.確定 PLL 的設計參數,包括 VCO 頻率、參考信號頻率、N 倍頻、分頻參數等。

4.根據設計參數計算 PLL 的電路元件參數,例如反相放大器增益、電容值、電阻值等。

5.按照電路設計方案,選配電路元件,布局設計,最后進行電路搭建和測試。

總之,PLL電路是時鐘發生器的核心部分,它能夠實現高精度、低抖動、抗干擾的時鐘信號輸出,并且可以根據應用需要進行倍頻和分頻等功能。通過上述步驟,我們可以在硬件上配置PLL電路,從而實現高質量的時鐘發生器設計。

-

鎖相環

+關注

關注

35文章

597瀏覽量

89610 -

振蕩器

+關注

關注

28文章

4007瀏覽量

140830 -

pll

+關注

關注

6文章

889瀏覽量

136400 -

時鐘發生器

+關注

關注

1文章

227瀏覽量

69118

發布評論請先 登錄

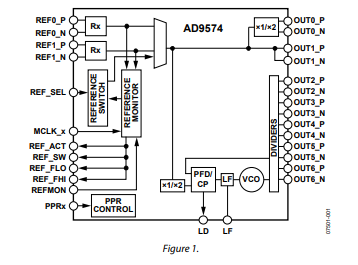

AD9574以太網 千兆以太網時鐘發生器技術手冊

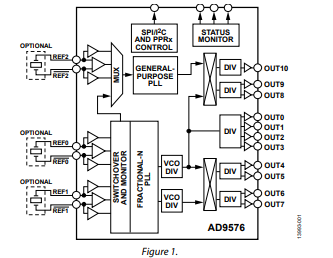

AD9576雙通道PLL、異步時鐘發生器技術手冊

時鐘發生器的特點和應用

鎖相環是什么意思

鎖相環PLL的噪聲分析與優化 鎖相環PLL與相位噪聲的關系

鎖相環PLL在無線電中的應用 鎖相環PLL與模擬電路的結合

鎖相環PLL與頻率合成器的區別

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

PLL1707/PLL1708 3.3V雙通道PLL多時鐘發生器數據表

時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?

時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?

評論