本文討論電源噪聲干擾對基于PLL的時鐘發生器的影響,并介紹幾種用于評估由此產生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發生器的電源噪聲抑制(PSNR)性能。

采用PLL的時鐘發生器廣泛用于網絡設備中,用于生成高精度和低抖動參考時鐘或保持同步網絡操作。大多數時鐘振蕩器使用理想、干凈的電源給出其抖動或相位噪聲規格。然而,在實際的系統環境中,電源可能會因板載開關電源或嘈雜的數字ASIC而受到干擾。為了在系統設計中實現最佳性能,了解這種干擾的影響非常重要。

首先,我們將研究基于PLL的時鐘發生器的基本電源噪聲抑制(PSNR)特性。然后,我們將解釋如何從頻域測量中提取時序抖動信息。然后應用這些技術,并使用實驗室臺架測試比較幾種不同的測量方法。最后,我們將總結首選方法的優點。

PLL時鐘發生器的PSNR特性

典型的PLL時鐘發生器如圖1所示。由于輸出驅動器對于不同類型的邏輯接口可能具有非常不同的PSNR性能,因此以下分析將重點介紹電源噪聲對PLL本身的影響。

圖1.PLL時鐘發生器的典型拓撲。

圖2顯示了PLL相位模型。該模型假設電源噪聲為 VN,注入 PLL/VCO,并且分頻比 M 和 N 設置為 1。

圖2.鎖相環的相位模型。

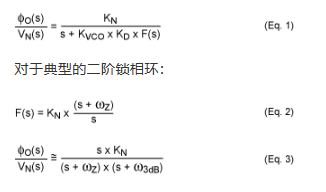

從VN(s)到ΦO(s)的PLL閉環傳遞函數由下式給出:

這里 ω3分貝是 PLL 3dB 帶寬,ΩZ是PLL零點頻率,ωZ<< ω3分貝.

公式3表明,在PLL時鐘發生器中,當電源干擾(PSI)頻率大于PLL20dB帶寬時,電源噪聲抑制3dB/dec。對于 ω 之間的 PSI 頻率Z和 ω3分貝,輸出時鐘相位隨PSI幅度變化,如下所示:

例如,圖3顯示了PLL在PLL的3dB帶寬的兩種不同設置下的PSNR特性。

圖3.典型的 PLL PSNR 特性。

功率頻譜雜散到DJ的轉換

當單音正弦信號時,fM,應用于PLL的電源,它在時鐘輸出端產生窄帶相位調制。這種相位調制通常可以用傅里葉級數表示來描述:

這里β是表示最大相位偏差的調制指數。對于小折射率調制(β << 1),貝塞爾函數可以近似為:

這里 n = 0 表示載體本身。當n = ±1時,相位調制信號由下式給出:

測量雙邊帶功率譜SV(f)時,如果變量x表示fO處載波與fM處基波邊帶音之間的電平差,則:

由于β是以弧度為單位的最大相位偏差,因此由這種小折射率相位調制引起的峰峰值DJ可以推導出為:

上述分析假設沒有幅度調制對fM音調的影響。實際上,幅度和相位調制都可以產生,從而降低了這種方法的精度。

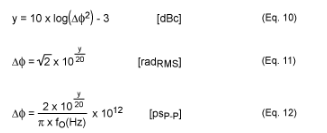

將相位噪聲頻譜雜散轉換為DJ

有一種方法可以在測量功率譜S 時避免調幅效應V(f).可以通過測量相位噪聲頻譜中的雜散來計算DJ,同時在電源上施加單音正弦干擾。變量y(dBc)表示在頻率偏移f下測得的單邊帶相位雜散功率M,產生的相位偏差ΔΦ(rad有效值) 可以派生為:

需要注意的是,上述分析中的單邊帶相位譜并不是雙邊帶譜的折疊版本。這就是公式3中10dB分量的原因。圖4顯示了DJ與公式12給出的相位雜散功率之間的關系。

圖4.DJ 與相位雜散功率。

PSNR測量技術

下一節將演示測量時鐘源PSNR的五種不同方法。MAX3624低抖動時鐘發生器作為示例。圖5所示的測量設置使用函數發生器將正弦信號注入MAX3624評估(EV)板的電源。單音干擾的幅度直接在V處測量抄送引腳靠近 IC。限幅放大器MAX3272用于消除幅度調制;隨后是一個巴倫,將差分輸出轉換為單端信號,用于驅動不同的測試設備。為了比較不同測試的結果,所有測量均在以下條件下進行:

時鐘輸出頻率:fO= 125兆赫

正弦調制頻率:fM= 100kHz

正弦信號幅度:80mVP-P

圖5.PSNR 測量設置。

方法 1.功率譜測量

在功率頻譜分析儀上觀察時,窄帶相位調制表現為載波周圍的兩個邊帶。圖 6 顯示了使用安捷倫 E5052 的頻譜監控器功能查看時的情況。測得的第一邊帶幅度相對于載波幅度為-53.1dBc,換算為11.2ps?P-PDJ,根據公式 9。

圖6.測量的功率譜。

方法 2.SSB 相位雜散測量

在相位噪聲分析儀上,PSI將表現為相對于載波的相位雜散。測得的相位噪聲頻譜如圖7所示。100kHz時的相位雜散功率為-53.9dBc,相當于10.2psP-PDJ使用公式12。

圖7.測量的SSB相位噪聲和雜散。

方法 3.相位解調測量

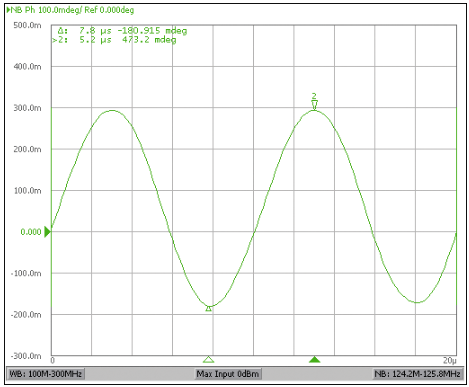

使用 Agilent E5052 信號分析儀,可直接測量 100kHz 處的相位解調正弦信號,如圖 8 所示,給出了與其理想位置的最大相位偏差。峰峰值相位偏差為0.47°,換算為10.5psP-P在 125MHz 的輸出頻率下。

圖8.MAX3624相位解調信號

方法 4.實時示波器測量

在時域測量中,PSI引起的DJ可以通過測量時間間隔誤差(TIE)直方圖來獲得。在實時示波器上,當單音干擾注入PLL時,時鐘輸出TIE分布將顯示為正弦概率密度函數(PDF)。DJ 可以使用雙狄拉克模型1 通過測量 TIE 直方圖中兩個高斯分布的平均值之間的峰值距離來估計。圖 9 顯示了使用安捷倫無限 DSO81304A 40GSa/s 實時示波器測得的 TIE 直方圖。測得的峰分離為9.4ps。

圖9.測量的 TIE 直方圖。

應該注意的是,實時示波器的存儲深度可能會限制可應用于PLL電源的低正弦調制頻率。例如,如果測試設備的存儲深度在采樣率設置為2Gsps時為40Msps,則它只能捕獲低至20kHz的抖動頻率分量。

方法 5.采樣范圍測量

使用采樣示波器時,需要同步觸發信號來分析被測時鐘抖動。TIE測量可以使用兩種觸發方法。

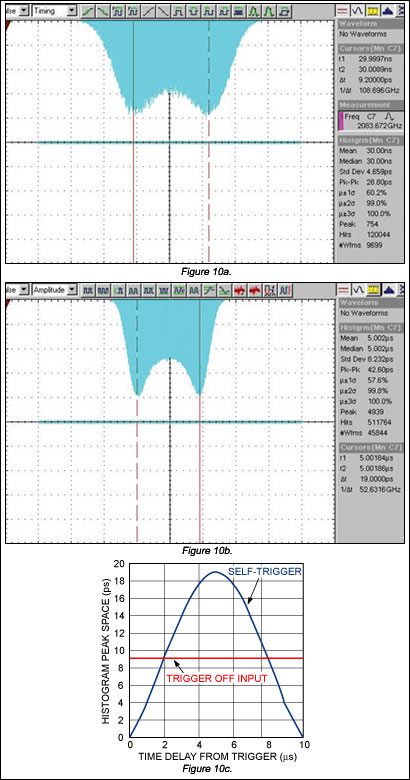

第一種方法是將低抖動參考時鐘應用于PLL時鐘發生器的輸入;使用與采樣示波器觸發器相同的時鐘源。圖10a顯示了測得的TIE直方圖,其峰值間距為9.2ps。使用參考時鐘觸發的優點是,測得的TIE直方圖峰間距與觸發位置的水平時間延遲無關。但是,測得的TIE直方圖可能會受到觸發時鐘抖動的影響。因此,使用抖動比被測時鐘發生器器件低得多的時鐘源非常重要。

替代方法使用自觸發來消除觸發時鐘抖動的影響。在這種情況下,被測時鐘發生器的輸出使用功率分配器分成兩個相同的信號。一個信號施加到采樣示波器的數據輸入,另一個信號施加到觸發輸入。由于觸發信號包含與測試信號相同的DJ,因此當示波器主時基的水平位置掃過正弦調制頻率的一個周期時,直方圖峰值分離會發生變化。在調制信號半個周期的水平位置,TIE直方圖上的峰值間隔將是測試信號的兩倍。圖10b所示為水平時延設置為3624μs時測得的MAX5 TIE直方圖。估計的TIE峰值分離為19ps,相當于9.5ps的DJP-P.

圖10c顯示了在與觸發點不同的水平時間延遲下測得的TIE直方圖峰間距。為了進行比較,當采樣范圍由參考時鐘輸入觸發時,也會顯示TIE結果。

圖 10.TIE 直方圖顯示了各種觸發條件:由REF_IN (a) 觸發;自觸發,Td= 5μs (b);以及峰值間距與觸發時間延遲的關系 (c)。

測量摘要

表1總結了MAX3624 125MHz時鐘輸出端測得的DJ。使用上面討論的不同方法收集數據。應該注意的是,使用TIE直方圖的雙狄拉克近似測量的DJ略小于從頻域頻譜分析中獲得的DJ。這種差異是由正弦抖動 (SJ) PDF 與隨機抖動分量的高斯分布卷積過程引起的。 因此,從雙狄拉克模型中提取的 DJ 只是一個估計值;僅當隨機抖動的標準偏差遠小于抖動直方圖的兩個峰值間隔之間的距離時,才應應用它。

| 測量方法 | DJ (psP-P) |

| 功率譜 | 11.2 |

| SSB 相位雜散 | 10.3 |

| 相分解 | 10.5 |

| 實時范圍 | 9.4 |

|

采樣范圍 (參考觸發) |

9.2 |

|

采樣范圍 (自觸發) |

9.5 |

| *80mVP-P,電源上的100kHz正弦信號。 | |

結論

對于示例中使用的相對較大的干擾,結果具有很好的相關性。但是,當干擾水平相對于隨機抖動下降時,時域方法變得不那么精確。此外,如果時鐘信號被幅度調制破壞,則使用功率譜分析儀的測量將變得不可靠。因此,在所介紹的所有方法中,使用相位噪聲分析儀測量相位雜散功率是表征時鐘發生器PSNR的最準確、最方便的方法。相同的方法可以擴展為評估由相位噪聲頻譜上出現的其他雜散產物引起的DJ方面。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18251瀏覽量

254875 -

pll

+關注

關注

6文章

880瀏覽量

136016 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68824

發布評論請先 登錄

超低抖動時鐘發生器與串行鏈路系統性能的優化

用于評估AD9576時鐘倍頻器異步時鐘發生器的評估板AD9576/PCBZ

用于評估AD9525 3.6 GHz時鐘發生器的評估板AD9525/PCBZ

低抖動高精度時鐘發生器MAX3625B相關資料分享

MAX3625B中文資料,pdf,低抖動、精密時鐘發生器

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

評估低抖動PLL時鐘發生器的電源噪聲抑制

評估低抖動PLL時鐘發生器的電源噪聲抑制

評論