文章來源:學習那些事

原文作者:小陳婆婆

干法刻蝕技術作為半導體制造的核心工藝模塊,通過等離子體與材料表面的相互作用實現(xiàn)精準刻蝕,其技術特性與工藝優(yōu)勢深刻影響著先進制程的演進方向。

干法刻蝕理論概述

等離子體驅動的技術特性

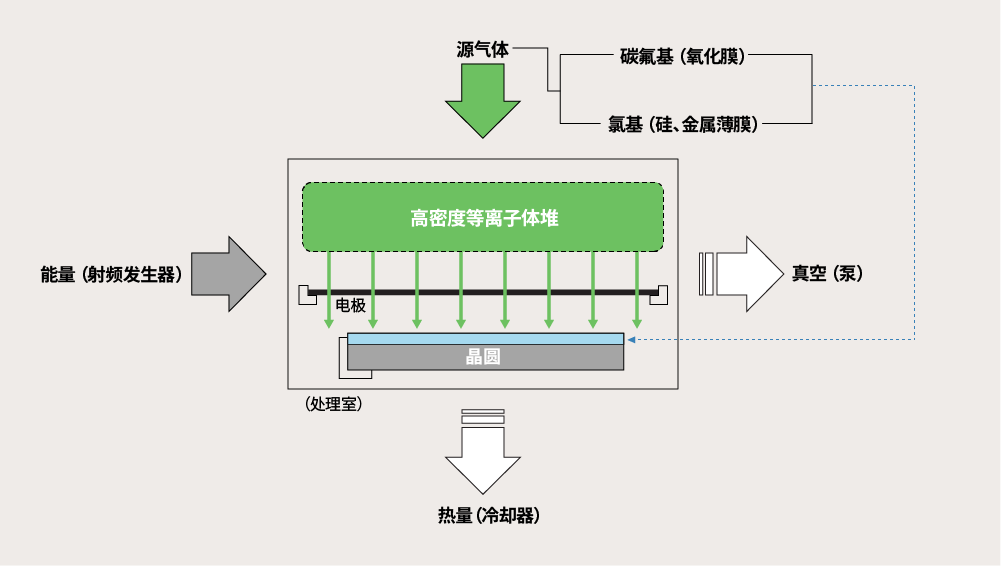

在真空環(huán)境下,反應氣體經(jīng)電離形成由電子、離子及自由基構成的等離子體,其離化率雖僅0.01%~10%,但通過局部電荷積累效應可維持穩(wěn)定的刻蝕能量場。

相較于濕法工藝,干法刻蝕摒棄了液態(tài)化學試劑,轉而通過物理轟擊與化學反應的協(xié)同作用實現(xiàn)材料去除,這種轉變帶來三大核心優(yōu)勢:其一是各向異性刻蝕能力,通過離子束方向性控制可實現(xiàn)垂直度優(yōu)于85°的側壁形貌;其二為關鍵尺寸(CD)控制精度,借助實時終點檢測技術可將線寬偏差控制在±5nm以內;其三在于工藝穩(wěn)定性,通過腔體壓力與射頻功率的精確調控,可實現(xiàn)晶圓內、批次間刻蝕速率波動<2%的極致均勻性。

工藝分類與作用機理

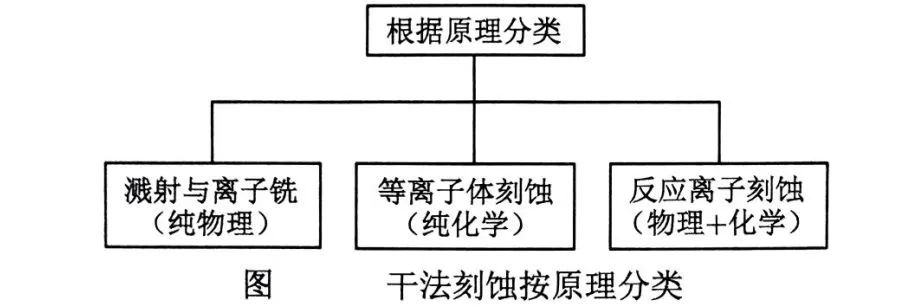

根據(jù)能量耦合方式,干法刻蝕可分為三大技術路線:

純物理刻蝕(濺射/離子銑):依托高能惰性氣體離子(如Ar ^+^ )的垂直轟擊實現(xiàn)材料濺射去除,具有完全各向異性特征,但缺乏化學選擇性,常用于金屬互聯(lián)層的修整

純化學刻蝕(等離子體刻蝕):利用氟基/氯基自由基與硅基材料的化學反應生成揮發(fā)性產(chǎn)物(如SiF4),呈現(xiàn)各向同性特征,對氧化硅/氮化硅的選擇比可達10:1以上

反應離子刻蝕(RIE):通過物理轟擊與化學刻蝕的動態(tài)平衡,在維持各向異性的同時提升刻蝕選擇比,已成為邏輯器件柵極刻蝕、存儲器三維堆疊的主流解決方案

復合刻蝕機制解析

現(xiàn)代RIE工藝通過多參數(shù)協(xié)同實現(xiàn)精密控制:

化學刻蝕主導區(qū):中性自由基在表面吸附后引發(fā)化學反應,生成易揮發(fā)產(chǎn)物,該過程決定基礎刻蝕速率與材料選擇性

物理轟擊增強區(qū):加速離子束通過動量傳遞打破化學鍵,清除表面鈍化層,其能量密度直接影響各向異性程度

聚合物沉積調控:含碳前驅體在離子轟擊下于側壁形成保護層,通過調整沉積/刻蝕速率比(D/E比)可實現(xiàn)側壁傾角從0°到90°的連續(xù)調控

微負載效應補償:采用脈沖式射頻功率與分壓控制技術,有效緩解高深寬比結構中的刻蝕速率衰減問題

技術挑戰(zhàn)與發(fā)展方向

盡管干法刻蝕在精度與可控性方面優(yōu)勢顯著,但仍面臨三大技術瓶頸:其一,等離子體誘導損傷需通過低溫工藝與鈍化層優(yōu)化進行抑制;其二,多材料疊層刻蝕的選擇比需突破100:1量級;其三,EUV光刻膠的刻蝕兼容性亟待提升。當前研究聚焦于高密度等離子體源開發(fā)、原子層刻蝕(ALE)技術突破以及機器學習驅動的工藝窗口優(yōu)化,旨在滿足3nm及以下節(jié)點對極致精度與良率控制的需求。

該技術體系的發(fā)展,正持續(xù)推動著半導體器件向更高集成度、更低功耗方向演進,其工藝創(chuàng)新已成為摩爾定律延續(xù)的關鍵技術支柱之一。

濺射與離子銑刻蝕(純物理刻蝕)

濺射與離子銑刻蝕作為典型的純物理刻蝕工藝,其核心機理在于利用惰性氣體離子(如氬離子)在強電場加速下獲得的動能,通過垂直轟擊晶圓表面實現(xiàn)材料去除。該技術的顯著優(yōu)勢在于其極端的各向異性特性,離子束的直線傳播特性使得側壁傾角可控制在5°以內,這對亞微米級線寬的精確控制至關重要。然而,物理轟擊的普適性也帶來固有缺陷:

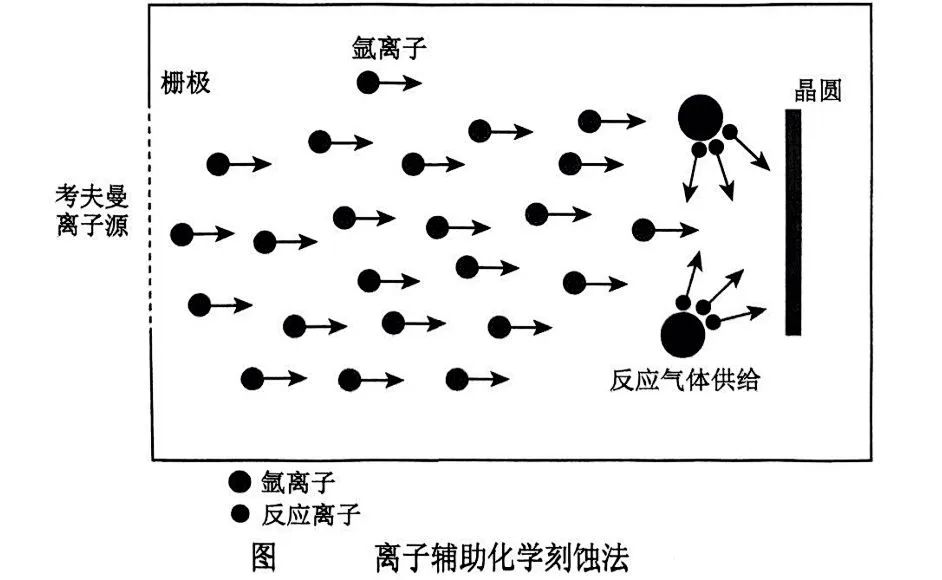

其一,刻蝕選擇比通常低于3:1,光刻膠與襯底材料的同步侵蝕問題突出,尤其在圖(a)所示的溝槽結構中,光刻膠側壁侵蝕可導致關鍵尺寸(CD)偏差超過20%;其二,濺射產(chǎn)物再沉積效應顯著,圖(b)顯示,光刻膠顆粒在離子反彈作用下的再淀積污染率可達15%,需通過高頻氬氣吹掃緩解;其三,離子溝槽效應如圖(c)所示,垂直入射離子在光刻膠斜面發(fā)生鏡面反射,在襯底形成二次刻蝕溝槽,深度可達原始刻蝕深度的30%。針對上述問題,行業(yè)開發(fā)出離子輔助化學刻蝕技術

通過在硅片表面引入含氯/氟反應氣體,使離子轟擊能量從純物理作用轉向促進表面化學反應,典型工藝如CF4/Ar混合氣體刻蝕硅氧化物,可將選擇比提升至8:1,同時保持50nm/min的刻蝕速率。

等離子體刻蝕(純化學刻蝕)

等離子體刻蝕技術則完全依托于高活性自由基團的化學反應。在射頻電場作用下,含氟/氯氣體(如SF6、Cl2)解離生成F·、Cl·等自由基,這些中性粒子通過擴散到達晶圓表面,與硅、二氧化硅等材料發(fā)生選擇性反應,生成SiF4、CO等揮發(fā)性產(chǎn)物。

該技術的核心優(yōu)勢在于其卓越的刻蝕選擇性,通過氣體組分的精確調控,可實現(xiàn)硅/光刻膠選擇比>50:1,二氧化硅/氮化硅選擇比>30:1,這對保護下層器件結構至關重要。

然而,化學反應的各向同性特性導致線寬控制能力受限,在深寬比>5:1的結構中,側向鉆蝕可使特征尺寸膨脹15%-20%。為突破此瓶頸,行業(yè)采用脈沖式等離子體技術,通過周期性通斷射頻電源,在自由基反應階段與副產(chǎn)物解吸階段之間建立動態(tài)平衡,使刻蝕剖面各向異性比從0.6提升至0.85。

典型應用如邏輯器件接觸孔刻蝕,采用C4F8/Ar脈沖等離子體,在保持120nm/min刻蝕速率的同時,將側向鉆蝕控制在2nm以內,滿足14nm節(jié)點精度要求。

反應離子刻蝕(物理+化學刻蝕)

反應離子刻蝕(RIE)作為半導體制造的核心工藝,通過物理轟擊與化學反應的協(xié)同作用,實現(xiàn)了刻蝕速率、選擇性與各向異性的突破性平衡。其技術本質可拆解為三大核心部分:

協(xié)同刻蝕機理

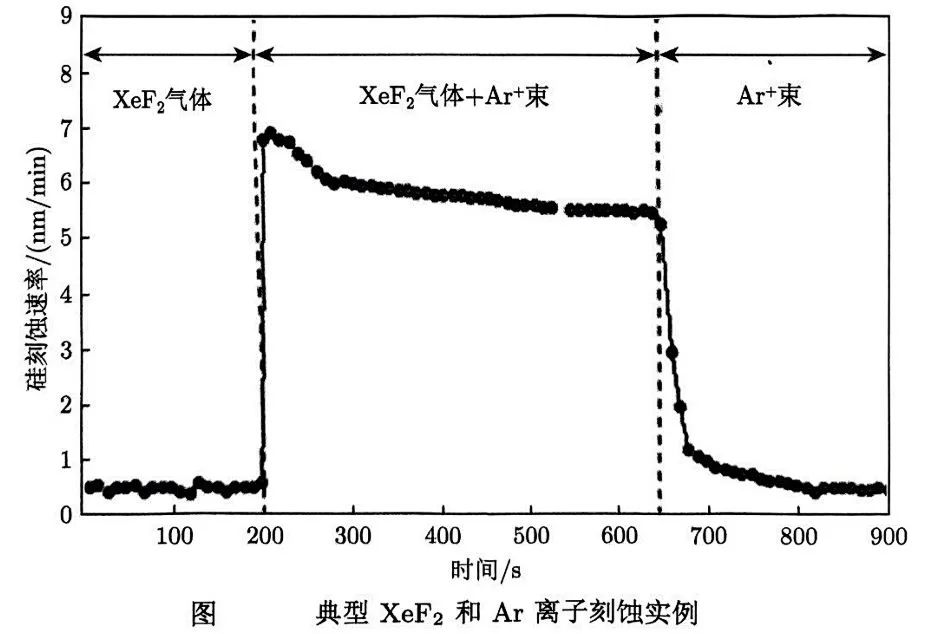

RIE工藝中,等離子體中的帶電離子(如Ar ^+^ )在射頻偏壓加速下獲得數(shù)百eV動能,通過垂直轟擊打破待刻蝕材料表面化學鍵,同時氟基/氯基自由基(F·、Cl·)與暴露出的活性位點發(fā)生選擇性化學反應,生成揮發(fā)性產(chǎn)物(如SiF4、AlCl3)。這種“物理清障+化學刻蝕”的協(xié)同效應,使刻蝕速率較純物理或純化學工藝提升1個數(shù)量級。

典型應用如硅刻蝕速率可達1-2μm/min,且硅/光刻膠選擇比>20:1。

聚合物調控技術

刻蝕過程中,含碳氣體(如CHF3、C4F8)解離生成的含碳聚合物在側壁沉積形成保護層,其沉積速率與刻蝕速率的動態(tài)平衡決定了側壁形貌:

高沉積速率模式:聚合物覆蓋速率>刻蝕速率,形成V形側壁,適用于淺溝槽隔離(STI)等結構;

低沉積速率模式:通過優(yōu)化氣體流量比(如CF4/CHF3比例),使聚合物僅在側壁沉積而表面保持清潔,獲得垂直度>88°的U形側壁,滿足FinFET柵極刻蝕需求。

工藝系統(tǒng)與參數(shù)優(yōu)化

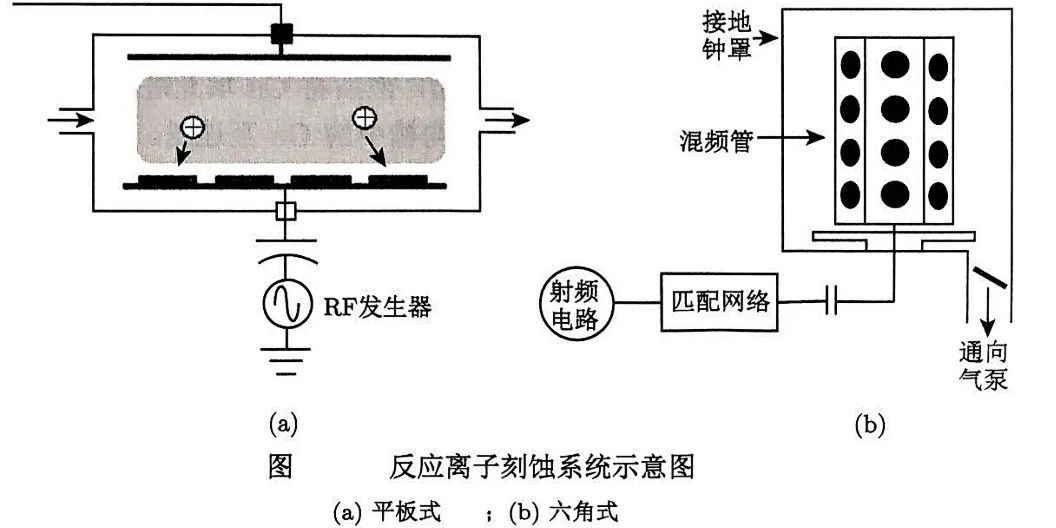

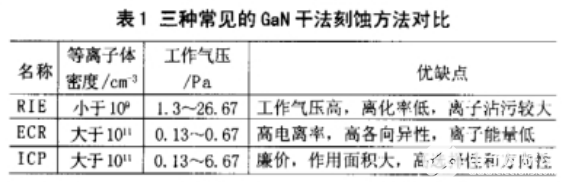

RIE設備分為平板式與電感耦合式(ICP)兩大架構:

平板式系統(tǒng):采用平行板電極結構,通過調節(jié)射頻功率(100-1000W)與腔體壓力(1-100mTorr)控制離子能量與通量,適用于介質層刻蝕;

六角式系統(tǒng):利用電感耦合產(chǎn)生高密度等離子體(>1012/cm3),結合可調偏壓電源,實現(xiàn)離子能量獨立控制,典型應用如3D NAND通道孔刻蝕,深寬比可達100:1。

典型工藝案例

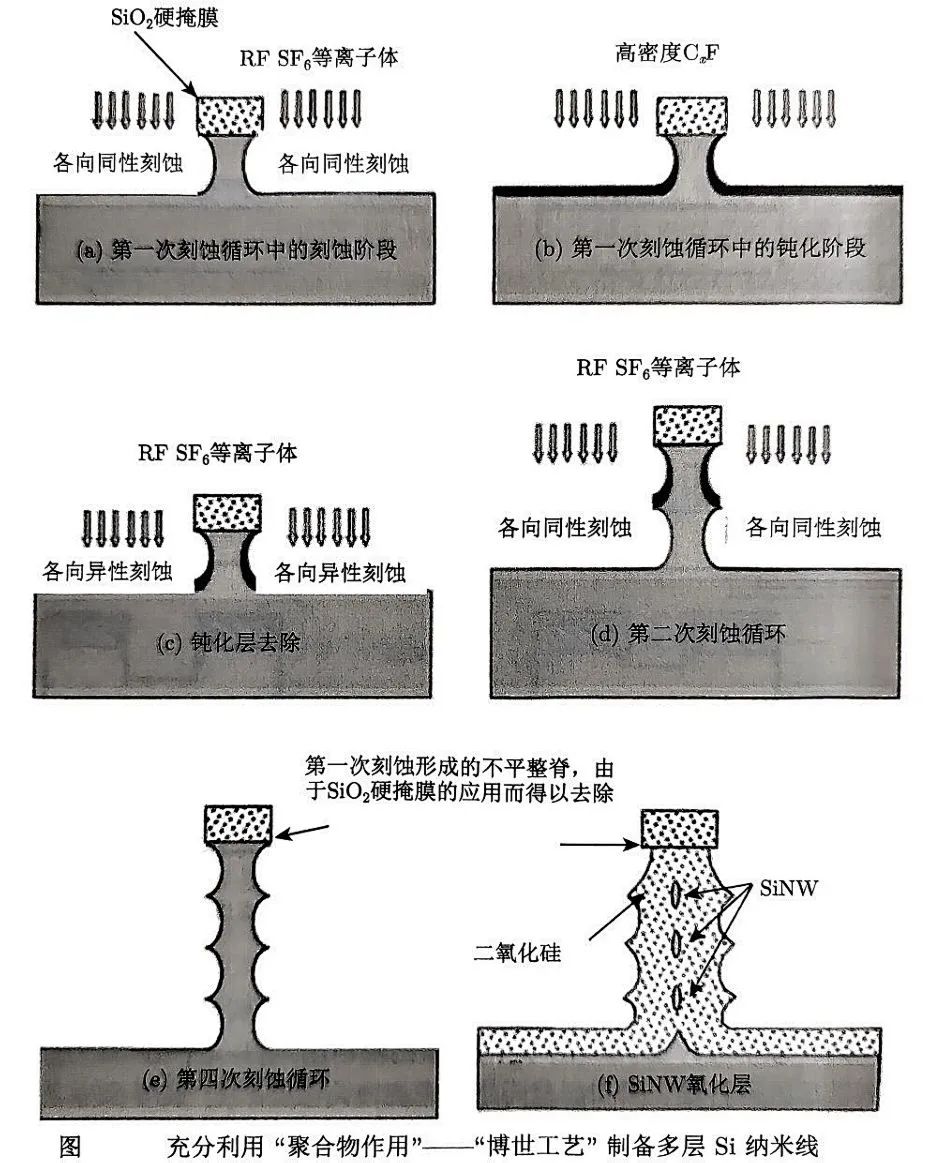

博世工藝:通過SF6刻蝕與C4F8鈍化的交替循環(huán),在硅表面形成周期性鋸齒狀結構。

最終通過熱氧化工藝將側壁形貌轉化為多層納米線,該工藝已實現(xiàn)深寬比60:1的通孔刻蝕;

硬掩膜集成工藝:針對多晶硅柵極刻蝕,采用SiO2硬掩膜替代光刻膠,通過兩步RIE工藝,將關鍵尺寸(CD)偏差控制在±3nm以內,顯著提升14nm節(jié)點器件良率。

技術邊界與材料適應性

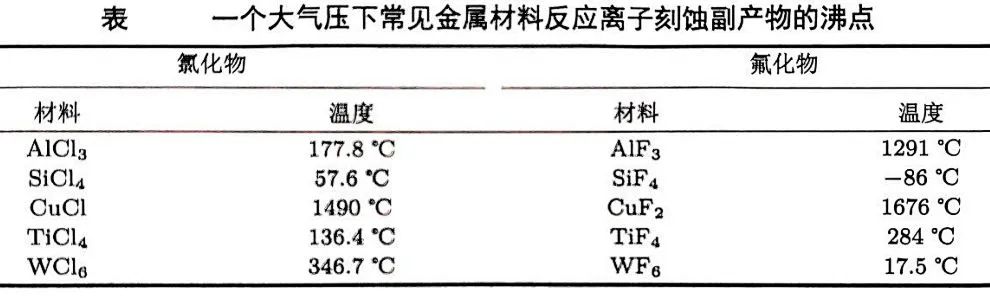

RIE工藝對材料的選擇性取決于副產(chǎn)物揮發(fā)性:

硅基材料:SiF4(沸點-86℃)的高揮發(fā)性使其成為RIE理想刻蝕對象;

金屬材料:Cu的刻蝕副產(chǎn)物CuCl(1490℃)因沸點過高易造成再沉積,故采用大馬士革工藝替代直接刻蝕;Al則可通過Cl基氣體(如BCl 3)實現(xiàn)可控刻蝕,副產(chǎn)物AlCl3沸點181℃,在150℃襯底溫度下可有效揮發(fā)。

-

半導體

+關注

關注

335文章

28553瀏覽量

232079 -

晶圓

+關注

關注

52文章

5112瀏覽量

129134 -

刻蝕工藝

+關注

關注

2文章

40瀏覽量

8567

原文標題:光刻基礎——干法刻蝕

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

干法刻蝕常用設備的原理及結構

釋放MEMS機械結構的干法刻蝕技術

【轉帖】干法刻蝕的優(yōu)點和過程

釋放MEMS機械結構的干法刻蝕技術

兩種基本的刻蝕工藝:干法刻蝕和濕法腐蝕

GaN材料干法刻蝕工藝在器件工藝中有著廣泛的應用

干法刻蝕解決RIE中無法得到高深寬比結構或陡直壁問題

干法刻蝕和清洗(Dry Etch and Cleaning)

干法刻蝕與濕法刻蝕各有什么利弊?

干法刻蝕工藝的不同參數(shù)

晶圓表面溫度對干法刻蝕的影響

干法刻蝕側壁彎曲的原因及解決方法

一文詳解干法刻蝕工藝

一文詳解干法刻蝕工藝

評論