本文介紹了干法刻蝕側(cè)壁彎曲的原因及解決方法。

什么是側(cè)壁彎曲?

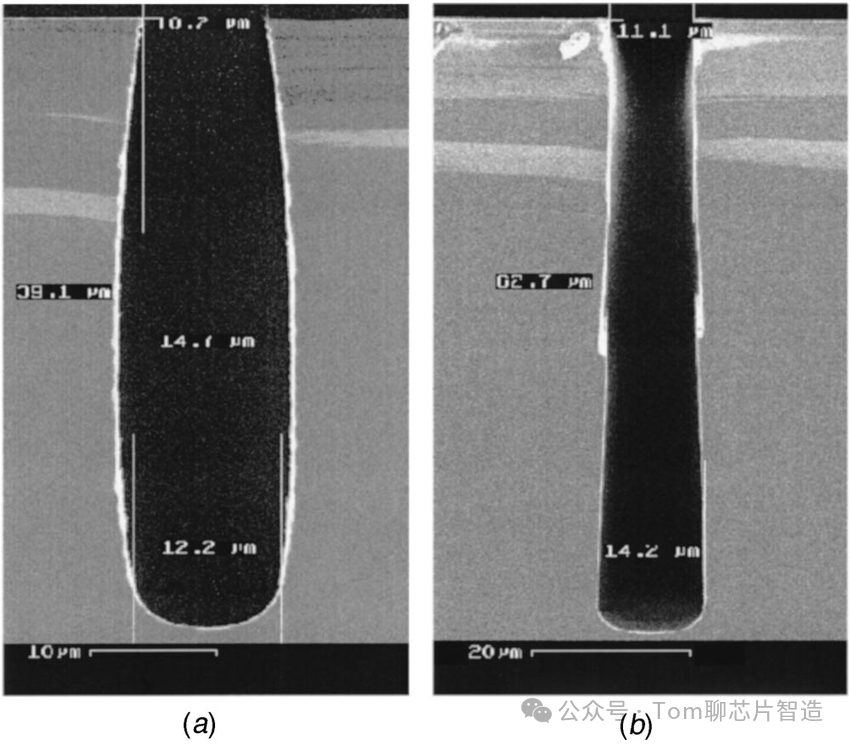

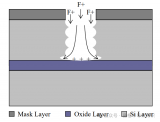

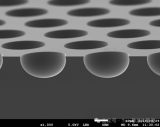

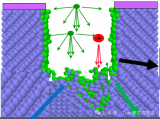

如上圖,是典型的干法刻蝕時,側(cè)壁彎曲的樣子,側(cè)壁為凹形或凸形結(jié)構(gòu)。而正常的側(cè)壁幾乎是垂直的,角度接近 90°。

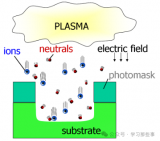

什么原因?qū)е铝藗?cè)壁彎曲? 1,離子從光刻膠掩模邊緣散射,以特定角度進入刻蝕區(qū)域,導(dǎo)致側(cè)壁形貌的偏差。這種散射取決于掩模的傾斜角度,如果角度較大,散射更顯著。

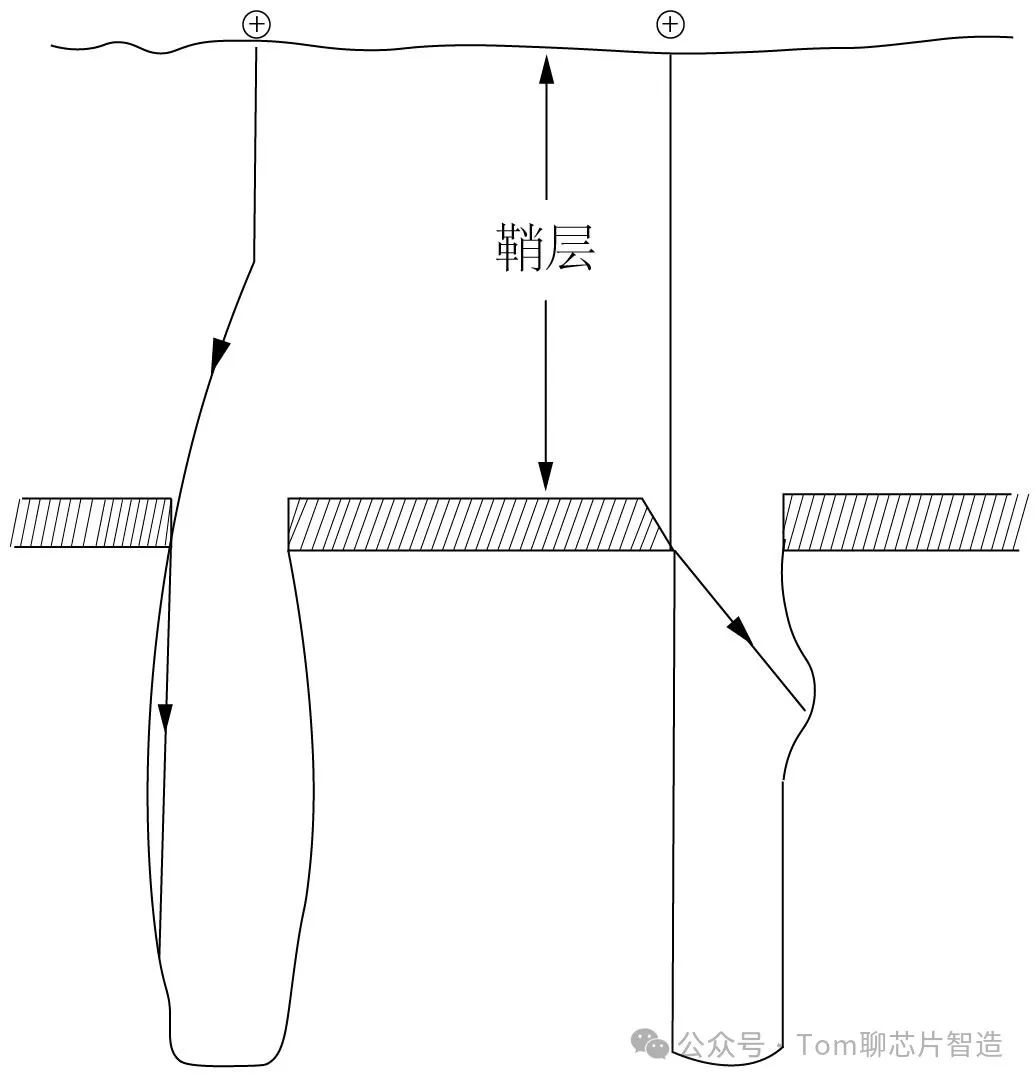

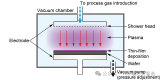

2,離子在鞘層中的散射:如果工藝壓力過高,在等離子體鞘層中,離子的碰撞和散射頻率增加,導(dǎo)致離子軌跡偏離,進而引起側(cè)壁彎曲。

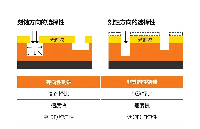

3,生成的聚合物分布不均:聚合物通常在孔頂部沉積得更好,而在深度較大的區(qū)域沉積較差。這種分布不均導(dǎo)致特征的頂部受保護,而側(cè)壁底部容易受到攻擊,進而形成彎曲的側(cè)壁。

解決方案

1,光刻膠的形貌盡量做的陡直,不要坡度太大

2,工藝腔壓力不要太大,降低工藝腔壓力,減少散射,改善側(cè)壁形貌。

3,控制保護氣體比例,確保側(cè)壁的聚合物保護層均勻分布。

-

光刻膠

+關(guān)注

關(guān)注

10文章

328瀏覽量

30779 -

刻蝕

+關(guān)注

關(guān)注

2文章

202瀏覽量

13321

原文標題:干法刻蝕側(cè)壁彎曲的原因及解決方法

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一文詳解干法刻蝕工藝

干法刻蝕的概念、碳硅反應(yīng)離子刻蝕以及ICP的應(yīng)用

上海伯東IBE離子束刻蝕機介紹

半導(dǎo)體濕法和干法刻蝕

干法刻蝕時側(cè)壁為什么會彎曲

芯片制造中的濕法刻蝕和干法刻蝕

晶圓表面溫度對干法刻蝕的影響

干法刻蝕工藝的不同參數(shù)

為什么干法刻蝕又叫低溫等離子體刻蝕

半導(dǎo)體干法刻蝕技術(shù)解析

半導(dǎo)體芯片制造技術(shù)之干法刻蝕工藝詳解

干法刻蝕側(cè)壁彎曲的原因及解決方法

干法刻蝕側(cè)壁彎曲的原因及解決方法

評論