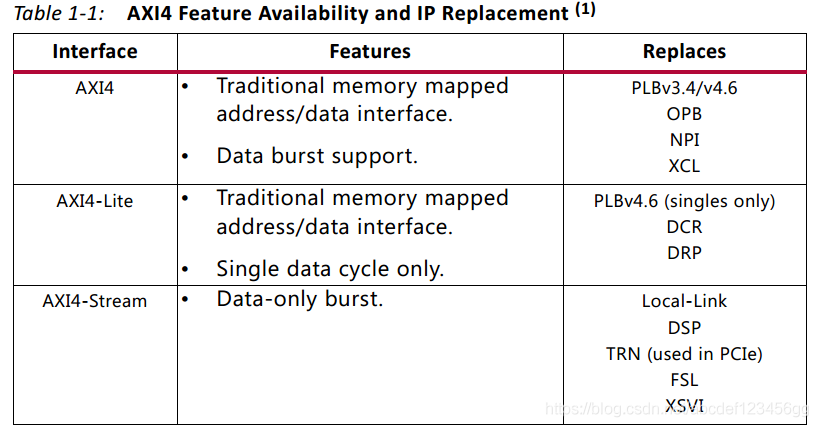

1、AXI 總線通道,總線和引腳的介紹

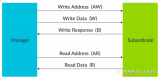

AXI接口具有五個獨立的通道:

(1)寫地址通道(AW):write address channel

(2)寫數據通道( W): write data channel

(3)寫響應通道( B) : write response channel

(4)讀地址通道(AR):read address channel

(5)讀數據通道( R): read data channel

五個通道圖為:

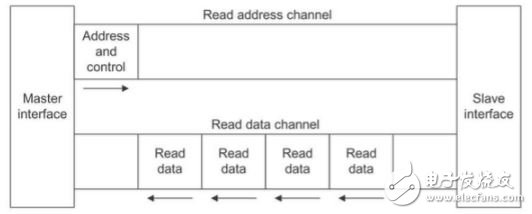

讀地址通道和讀數據通道

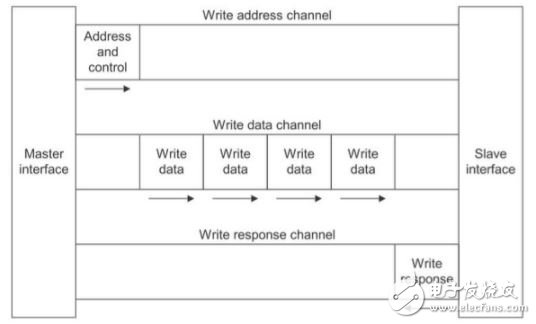

寫地址通道,寫數據通道和寫響應通道

讀地址通道的信號:S_AXI_ARADDR,S_AXI_ARPROT,S_AXI_ARVALID,S_AXI_ARREADY;

讀數據通道的信號:S_AXI_RDATA,S_AXI_RRESP,S_AXI_RVALID,S_AXI_RREADY;

寫地址通道的信號:S_AXI_AWADDR,S_AXI_AWPROT,S_AXI_AWVALID,S_AXI_AWREADY;

寫數據通道的信號:S_AXI_WDATA,S_AXI_WSTRB,S_AXI_WVALID,S_AXI_WREADY;

寫響應通道的信號:S_AXI_BRESP,S_AXI_BVALID,S_AXI_BREADY。

AXI接口的總線寬度:

C_S_AXI_ADDR_WIDTH : S_AXI數據總線的寬度

C_S_AXI_ADDR_WIDTH : S_AXI 地址總線的寬度

AXI接口的信號詳細說明:

總線的輸入時鐘信號

S_AXI_ARESETN : in std_logic;

全局性的復位信號,這個信號低電平有效

S_AXI_AWADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

寫地址通道(由主設備設置發送到從設備)

S_AXI_AWPROT : in std_logic_vector(2 downto 0);

寫通道保護類型,此信號表示事務的特權和安全級別,以及事務是數據訪問還是指令訪問。

S_AXI_AWVALID : in std_logic;

寫地址有效,此信號表示主設備正在發送有效的寫入地址和控制信息。

S_AXI_AWREADY : out std_logic;

寫地址就緒。這個信號表明,從設備將接受地址和相關的控制信號。

S_AXI_WDATA : in std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

寫數據(由主設備設置傳送到從設備)

S_AXI_WSTRB : in std_logic_vector((C_S_AXI_DATA_WIDTH/8)-1 downto 0);

寫數據選通,這個信號表明寫數據總線上哪個字節通道存著有效的數據。寫數據總線上每八個位對應一個寫選通位

S_AXI_WVALID : in std_logic;

寫有效,這個信號表明有效的寫數據和寫選通可用

S_AXI_WREADY : out std_logic;

寫準備,這個信號表明從設備可以獲取寫數據

S_AXI_BRESP : out std_logic_vector(1 downto 0);

寫響應,這個信號表明寫事務的完成狀態

S_AXI_BVALID : out std_logic;

寫響應有效。此信號表示信道正在發出有效的寫響應。

S_AXI_BREADY : in std_logic;

響應準備,這個信號表明主設備可以接受寫響應

S_AXI_ARADDR : in std_logic_vector(C_S_AXI_ADDR_WIDTH-1 downto 0);

讀地址(由主設備設置傳送到從設備)

S_AXI_ARPROT : in std_logic_vector(2 downto 0);

讀通道保護類型,此信號表示事務的特權和安全級別,以及事務是數據訪問還是指令訪問。

S_AXI_ARVALID : in std_logic;

讀地址有效,此信號表明讀地址通道正在發送有效的讀地址和控制信息

S_AXI_ARREADY : out std_logic;

讀地址準備,這個信號表明從設備已經準備接受地址和相關的控制信號

S_AXI_RDATA : out std_logic_vector(C_S_AXI_DATA_WIDTH-1 downto 0);

讀數據(由從設備設置)

S_AXI_RRESP : out std_logic_vector(1 downto 0);

讀響應,此信號表明讀數據傳輸的完成狀態

S_AXI_RVALID : out std_logic;

讀有效,此信號表明讀數據通道正在傳輸需要的讀數據

S_AXI_RREADY : in std_logic

讀準備,此信號表明主設備可以接受讀數據和響應信息

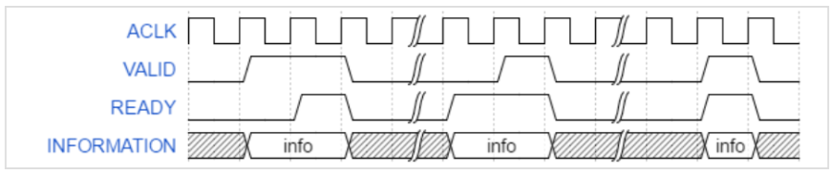

2、AXI 總線通道握手信號之間的依賴性

AXI總共有5個通道,每個通道都有一對valid & ready信號,發送方通過valid信號來指示什么時候數據和控制信息有效,接收方通過ready來指示可以接受數據和控制信息,傳輸的信息發生在vaild和ready同時為高電平的情況下。每個通道之間可以獨立握手,相互之間關系靈活。讀數據必須跟在與其數據相關聯的地址之后,寫響應必須在于其相關聯的寫事務之后出現。

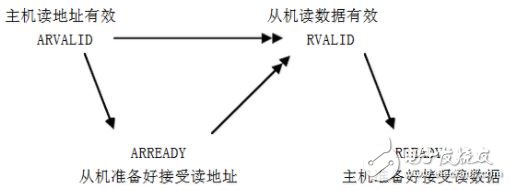

讀事務握手依賴關系如圖:

(1)設備可以在ARVALID出現的時候在給出ARREADY信號,也可以先給出ARREADY信號,再等待ARVALID信號。

(2)設備必須等待ARVALID和ARREADY信號都有效才能給出RVALID信號,開始數據傳輸。只有當讀地址發送完成后,才能進行讀數據的傳輸(箭頭形狀不同)

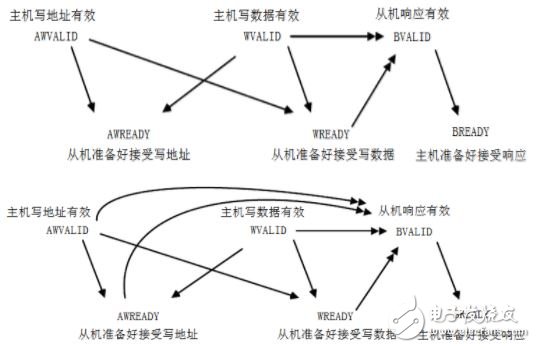

寫事務握手依賴關系如圖:

(1)主機不能等待設備先給出AWREADY或WREADY信號信號后再給出信號AWVALID或WVLAID。

(2)設備可以等待信號AWVALID或WVALID信號有效或者兩個都有效之后再給出AWREADY信號。

(3)設備可以等待AWVALID或WVALID信號有效或者兩個信號都有效之后再給出WREADY信號。

電子發燒友App

電子發燒友App

評論