。AXI4-Lite接口的特性如下: 1) 突發(fā)長度為1。 2) 所有訪問數(shù)據(jù)的寬度和數(shù)據(jù)總線寬度相同。 3) 支持數(shù)據(jù)總線寬度為32位或64位。 4) 所有的訪問相當于AWCACHE和ARCACHE

2020-09-27 11:33:02 8050

8050

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協(xié)議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI

2020-12-04 12:22:44 6179

6179

前面一節(jié)我們學會了創(chuàng)建基于AXI總線的IP,但是對于AXI協(xié)議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯(lián)合調(diào)試觀察AXI總線的信號。由于我們創(chuàng)建的接口是基于AXI_Lite協(xié)議

2020-12-23 15:32:37 2169

2169 FPGA+ARM是ZYNQ的特點,那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個實驗是創(chuàng)建一個基于AXI總線的GPIO IP,利用PL的資源來擴充GPIO資源。通過這個實驗迅速入門

2020-12-25 14:07:02 2957

2957

賽靈思 AXI Verification IP (AXI VIP) 是支持用戶對 AXI4 和 AXI4-Lite 進行仿真的 IP。它還可作為 AXI Protocol Checker 來使用。

2022-07-08 09:24:17 1280

1280 MPSoC有六個PL側(cè)高性能(HP)AXI主接口連接到PS側(cè)的FPD(PL-FPD AXI Masters),可以訪問PS側(cè)的所有從設備。這些高帶寬的接口主要用于訪問DDR內(nèi)存。有四個HP AXI

2022-07-22 09:25:24 2501

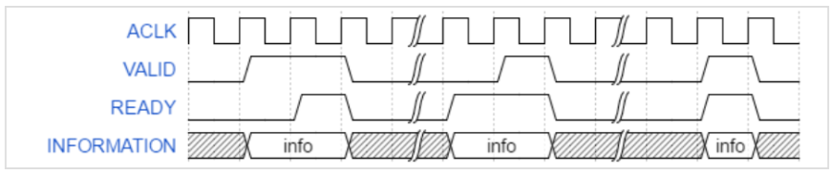

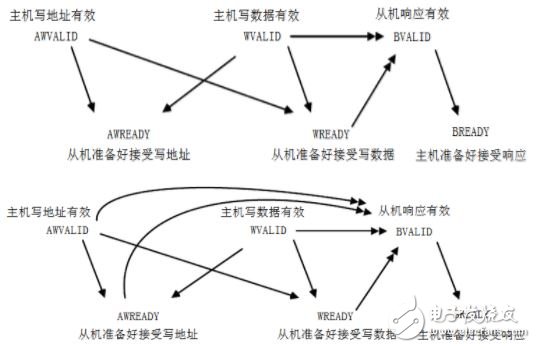

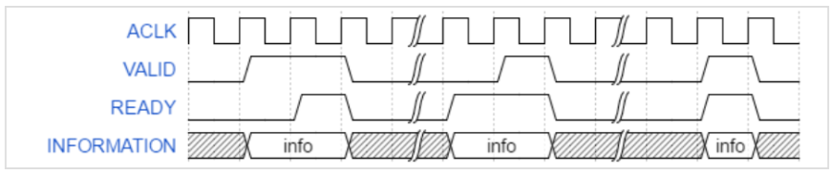

2501 由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊講解時序比較分散。所以筆者收藏AXI協(xié)議的幾種時序,方便編程。

2022-08-02 12:42:17 6661

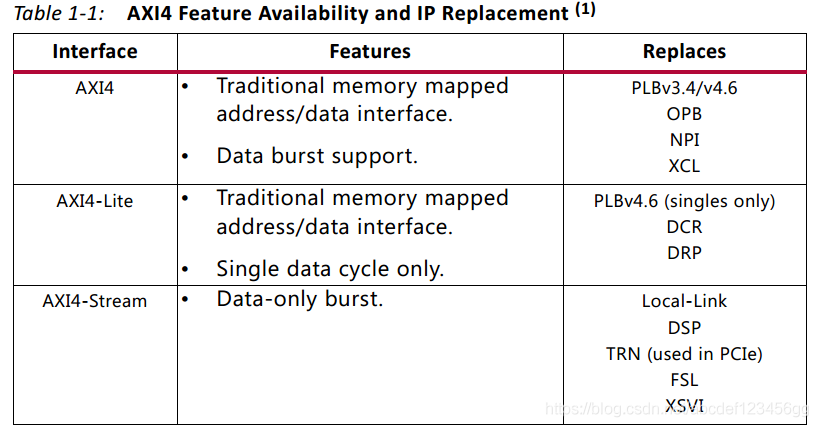

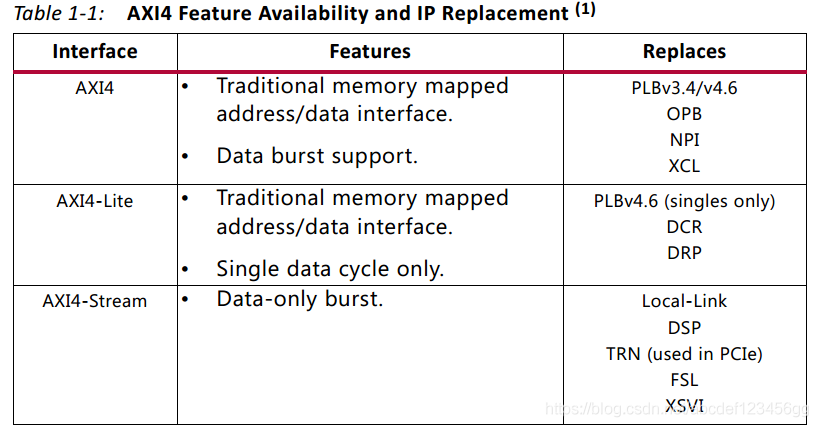

6661 首先我們看一下針對AXI接口的IP設計,在介紹之前我們先回顧一下AXI所具有的一些feature。

2024-02-20 17:12:56 518

518

各位大俠, 誰有AXI總線的手冊呀?如果有中文學習記錄+手冊就更完美了。謝謝先

2014-08-05 12:28:25

AXI總線學習AXI協(xié)議的主要特征主要結(jié)構(gòu)通道定義讀寫地址通道讀數(shù)據(jù)通道寫數(shù)據(jù)通道寫操作回應信號接口和互聯(lián)寄存器片基本傳輸Read burstOverlapping read burstWrite

2022-02-09 07:17:23

PL端的編寫和使用,接下來是PS端的介紹AXI_Lite總線使用方法(上)pl端讀寫B(tài)RAM一、總覽如圖,main函數(shù)實現(xiàn)的功能主要是初始化中斷,中斷來自WRRD模塊發(fā)送數(shù)據(jù)完畢,中斷觸發(fā)為上升沿。具體功能往下看。我們首先來看#define。不知道還有沒有記得..

2022-01-10 08:00:55

1、AXI接口協(xié)議詳解 AXI 總線 上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協(xié)議。其中三種AXI總線

2022-10-14 15:31:40

AXI 總線上面介紹了AMBA總線中的兩種,下面看下我們的主角—AXI,在ZYNQ中有支持三種AXI總線,擁有三種AXI接口,當然用的都是AXI協(xié)議。其中三種AXI總線分別為:AXI

2022-04-08 10:45:31

本文介紹了AMBA3.0AXI的結(jié)構(gòu)和特點,分析了新的AMBA3.0AXI協(xié)議相對于AMBA2.0的優(yōu)點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲設計。最后介紹了基于AXI協(xié)議的設計實例,探討了利用IP復用技術和DesginWareIP搭建基于AXI協(xié)議的SOC系統(tǒng)。

2023-09-20 08:30:25

AMBA_AXI總線詳解

2014-04-18 11:48:28

ARM處理器中有些總線APB AHB AXI 3 AXI 4,他們的有什么不同,各自作用?

2023-10-24 07:16:36

Arm AMBA協(xié)議集中,axi如何避免deadlock的,其它總線例如PCI是怎么避免的?

2022-10-20 11:07:56

IP核均采用AXI總線接口,已經(jīng)不再支持native接口。故做除法運算的重點從設計算法電路轉(zhuǎn)變成了調(diào)用AXI總線IP核以及HDL中有符號數(shù)的表示問題,極大降低了開發(fā)難度。以下就上述兩個方面進行探討

2018-08-13 09:27:32

的理解:1)DMA連接到IP總線。2)OCRAM連接到AXI64總線。3) ITCM和DTCM連接到TCM接口。是否可以將 DMA 緩沖區(qū)放在 OCRAM 中,將任務的緩沖區(qū)放在 DTCM 或 ITCM

2023-04-04 07:09:50

SPI總線協(xié)議介紹(接口定義,傳輸時序)

2021-03-03 07:45:16

擦除閃存扇區(qū)時,我需要為外部看門狗提供服務。被擦除的扇區(qū)位于執(zhí)行代碼的同一閃存組中。在嘗試從 RAM 跳躍和奔跑之前,我有幾個問題。參考手冊中哪里討論了閃存失速?考慮到芯片架構(gòu),在進行扇區(qū)擦除時切換端口 G 上的引腳是否有任何問題?換句話說,AXI總線矩陣是否在閃存擦除期間停止?謝謝!

2022-12-12 06:52:59

,我注意到Vivado希望我為XADC AXI4Lite接口分配I / O引腳。它是否正確 ?我正在閱讀PG091,我找不到任何建議自己實施XADC AXI4Lite I / O規(guī)劃的部分。有人可以澄清

2018-11-01 16:07:36

本帖最后由 何立立 于 2018-1-9 15:03 編輯

ZYNQ 、AXI協(xié)議、PS與PL內(nèi)部通信 三種AXI總線分別為:AXI4:(For high-performance

2018-01-08 15:44:39

1.AXI簡要介紹

AXI全稱(Advanced eXtensible Interface),主要描述了主設備和從設備之間的數(shù)據(jù)傳輸方式。適合高帶寬低延時設計,無需復雜的橋就能實現(xiàn)高頻操作,能滿足

2023-11-03 10:51:39

VARON是一款AXI性能分析工具。VARON幫助對AXI總線進行性能分析,該總線用于FPGA/ASIC設計的各個階段,如架構(gòu)、RTL設計、原型濾波網(wǎng)絡等。 VARON捕獲AXI總線信號和可視化

2020-11-02 16:54:39

[]合成了內(nèi)存),輸出端口合成為ap_fifo,這意味著,由于AXi4Lite不支持fifo結(jié)構(gòu),因此只能使用AXI4Stream接口/總線從輸出端口result []讀取數(shù)據(jù)。我也是這個嵌入式總線和接口

2019-02-28 13:47:30

請問在開源的E203的AXI總線支持burst傳輸嗎?在sirv_gnrl_icb2axi.v模塊中看到了

請問如何使用呢?相應的在NucleiStudio中的代碼中需要做什么修改呢?有大佬指點一下想要使用AXI做burst傳輸具體需要做那些步驟呢?

2023-08-12 06:13:08

我必須為我的包含AXI總線的項目創(chuàng)建測試平臺。我開始編寫用于寫入和讀取的接口和事務。我閱讀了以下博客:http://blog.verificationgentleman.com/2016/08

2020-05-06 09:04:55

我有一個simpleregister讀/寫/重置測試接口代碼(在VHDL中),我想與我的頂級處理系統(tǒng)7wrapper代碼鏈接。我想使用AXI總線協(xié)議對寄存器進行讀/寫/復位。實際上,我的測試接口

2019-09-09 10:03:44

現(xiàn)在我要用block design搭建SOC,需要將總線轉(zhuǎn)為AXI。按照論壇中的帖子,將e203_subsys_mems模塊中的sirv_gnrl_icb2axi模塊放到system層中,然后聲明

2023-08-12 06:12:28

`1、在開發(fā)zynq工程時遇到多個axi_hp總線讀寫ddr時,總線鎖死。現(xiàn)象就是axi_hp的wready信號一直為低。架構(gòu)圖: 2、應用write1、wrtie2、read1同時并行讀寫ddr3

2020-04-15 21:57:28

本指南介紹了高級微控制器總線體系結(jié)構(gòu)(AMBA)AXI的主要功能。

該指南解釋了幫助您實現(xiàn)AXI協(xié)議的關鍵概念和細節(jié)。

在本指南中,我們介紹:

?AMBA是什么。

?為什么AMBA在現(xiàn)代SoC設計中

2023-08-09 07:37:45

嗨,我將通過測試驗證這一點,但我對AXI-Lite外設“寄存器寫入”如何出現(xiàn)在AXI-Lite總線上有疑問。AXI標準表明數(shù)據(jù)和地址可以非常相互獨立地出現(xiàn),從靈活性的角度來看這是很好的,但是

2019-04-12 13:45:01

介紹參考文檔《玩轉(zhuǎn)Zynq-基礎篇:AXI總線協(xié)議介紹.pdf》。3 AXI GP外設配置在zstar_ex53實例的基礎上,需要對ZYNQ7Processing System(PS)配置頁面做更改

2019-11-12 10:23:42

的邏輯設計。2 AXI總線協(xié)議介紹參考文檔《玩轉(zhuǎn)Zynq-基礎篇:AXI總線協(xié)議介紹.pdf》。3Zynq PS的AXI HP配置在ZYNQ7 ProcessingSystem中,點擊左側(cè)Page

2019-11-26 09:47:20

不同通道使用情況下的數(shù)據(jù)吞吐量。大家可以在此基礎上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協(xié)議介紹參考文檔《玩轉(zhuǎn)Zynq-基礎篇:AXI總線協(xié)議介紹

2019-11-28 10:11:38

`玩轉(zhuǎn)Zynq連載3——AXI總線協(xié)議介紹1 更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s 1 AXI協(xié)議簡介AMBA AXI(Advanced

2019-05-06 16:55:32

無論是做SOC設計還是FPGA設計,AXI4總線是經(jīng)常提及的。關于AXI4總線關于什么是AXI4總線的定義,網(wǎng)絡上相關的文章不勝枚舉,也是無論是做FPGA還是ASIC都是必須要了解和掌握的知識,這里

2022-08-02 14:28:46

最近做的東西涉及到將原有的DSP+FPGA架構(gòu)的程序移植到ZYNQ-7系列FPGA上,請問如何將原DSP程序移植到ZYNQ-7的ARM上,可不可以做一個EMIF總線和AXI總線轉(zhuǎn)換的模塊呢?

2014-05-12 21:51:09

microblaze通過串口讀寫FPGA內(nèi)部axi4總線上的寄存器

2020-12-23 06:16:11

本文將討論AMBA的第三次修訂版,該修訂版向世界介紹了高級可擴展接口(AXI)協(xié)議。AXI協(xié)議最初是為高頻系統(tǒng)而設計的,旨在滿足各種組件的接口要求,同時允許靈活地互連這些組件。適用于高頻,低延遲

2020-09-28 10:14:14

VMM驗證方法在AXI總線系統(tǒng)中的實現(xiàn):本文基于中科院計算所某項目實際工作,介紹如何利用高級驗證語言、驗證基本庫、以及成熟的驗證模型,快速建立可隨機產(chǎn)生測試向量、向量場

2009-12-14 09:26:55 32

32 日前瑞思微電子正式宣布推出XSoC平臺,該平臺是一款基于AXI總線,擴展性很強的SoC平臺。

2011-09-07 10:20:39 1140

1140

目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現(xiàn)基于AXI總線的雙核嵌入式系統(tǒng)設計以及共享實現(xiàn)LED燈的時控.

2012-03-09 14:17:01 91

91 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 11

11 本節(jié)介紹的AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。 書上講的AXI比較具體,本節(jié)呢不打算落入俗套,從應用角度解釋AXI。

2018-07-13 07:08:00 10226

10226

詳細介紹AXI總線

2017-02-28 21:03:54 1

1 AXI總線的MicroBlaze雙核SoPC系統(tǒng)設計

2017-10-31 08:54:44 8

8 基于AXI4Stream總線協(xié)議,在Xilinx公司提供的FPGA上實現(xiàn)了一個具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實時圖像采集與顯示功能的視頻系統(tǒng)。AXI4Stream總線協(xié)議由ARM公司

2017-11-17 08:58:01 4189

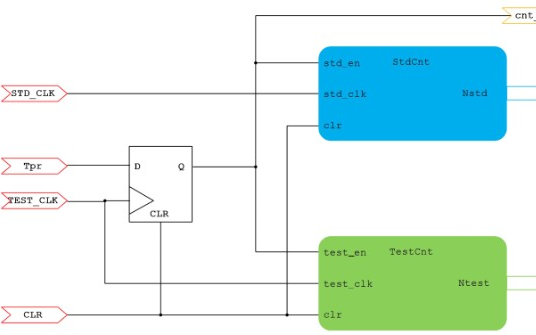

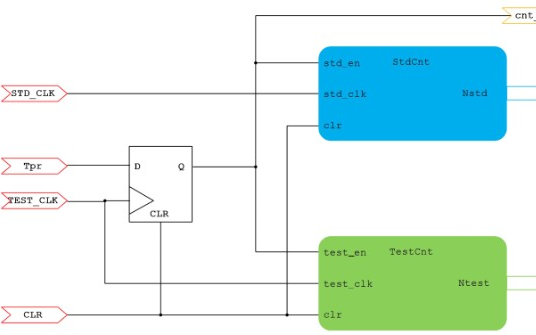

4189 這一節(jié)我們實現(xiàn)一個稍微復雜一點的功能——測量未知信號的頻率,PS和PL通過AXI總線交互數(shù)據(jù),實現(xiàn)我們希望的功能。

2018-12-08 11:00:30 1406

1406

由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊講解時序比較分散。所以筆者收藏AXI協(xié)議的幾種時序,方便編程。

2019-05-12 09:10:33 10860

10860

AXI總線是一種多通道傳輸總線,將地址、讀數(shù)據(jù)、寫數(shù)據(jù)、握手信號在不同的通道中發(fā)送,不同的訪問之間順序可以打亂,用BUSID來表示各個訪問的歸屬。主設備在沒有得到返回數(shù)據(jù)的情況下可發(fā)出多個讀寫操作。讀回的數(shù)據(jù)順序可以被打亂,同時還支持非對齊數(shù)據(jù)訪問。

2019-12-19 10:02:05 5367

5367 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現(xiàn),不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

新的賽靈思器件設計中不可或缺的一部分。充分了解其基礎知識對于賽靈思器件的設計和調(diào)試都很有幫助。 本篇博文將介紹賽靈思器件上的 AXI3/AXI4 的相關基礎知識。首先,我們將從一些通俗易懂的知識、理論

2020-09-27 11:06:45 5857

5857

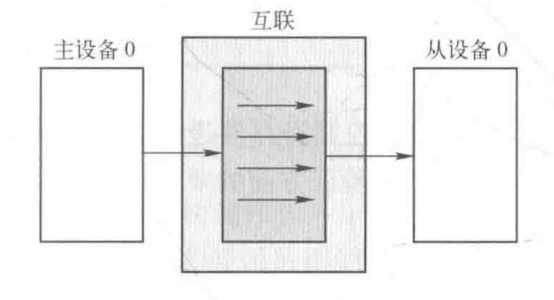

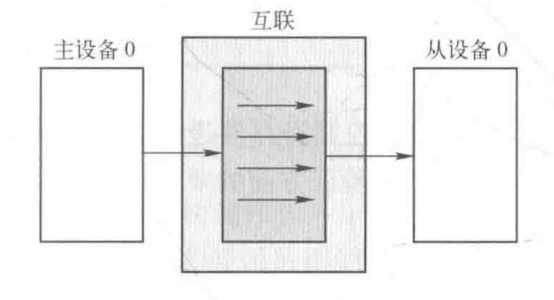

互聯(lián)結(jié)構(gòu)包括直通模式、只轉(zhuǎn)換模式、N-1互聯(lián)模式、N-M互聯(lián)模式。 1. 直通模式 當只有一個主設備和一個從設備使用AXI互聯(lián)時,AXI互聯(lián)不執(zhí)行任何轉(zhuǎn)換或流水線功能,AXI互聯(lián)結(jié)構(gòu)退化成直接

2020-11-16 17:39:24 3093

3093

XDMA是Xilinx封裝好的PCIE DMA傳輸IP,可以很方便的把PCIE總線上的數(shù)據(jù)傳輸事務映射到AXI總線上面,實現(xiàn)上位機直接對AXI總線進行讀寫而對PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 2692

2692 不同類型的DMA GPIO PL general purpose AXI GP AXI utlilizing PS DMAC High performance w/DMA ACP w/DMA 幾種

2020-10-09 18:05:57 6391

6391

,進入等待觸發(fā)狀態(tài)。 圖4?56 等待觸發(fā) 單擊 SDK 中的運行按鈕后, VIVADO 中 HW_ILA2 窗口采集到波形輸出,可以看到 AXI 總線的工作時序。 SDK中 mian.c 程

2020-10-30 17:10:22 2040

2040

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯(lián)系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯(lián)

2020-11-02 11:27:51 3880

3880

在 AMBA 系列之 AXI 總線協(xié)議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯(lián),多 Master,多 Slave的場景

2022-02-08 11:44:02 12802

12802 在介紹AXI之前,先簡單說一下總線、接口以及協(xié)議的含義。總線、接口和協(xié)議,這三個詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

2022-02-08 11:38:56 6550

6550

在介紹AXI之前,先簡單說一下總線、接口以及協(xié)議的含義。總線、接口和協(xié)議,這三個詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。

2021-02-04 06:00:15 10

10 在 AMBA 系列之 AXI 總線協(xié)議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯(lián),多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2021-03-17 21:40:29 25

25 本文介紹了AMBA3。0AXI的結(jié)構(gòu)和特點,分析了新的AMBA3。0AXI協(xié)議相對于AMBA2。0的優(yōu)點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲設計。

2021-03-29 09:46:43 8

8 為實現(xiàn)片上系統(tǒng)不同P核之間的協(xié)議轉(zhuǎn)換與高效通信,提出一種高效率PLB2AⅪI總線橋設計方案。利用PLB與AXI高性能總線的帶寬優(yōu)勢,通過引入流水線傳輸和讀寫重疊傳輸機制,將PLB總線協(xié)議中的地址

2021-03-30 15:21:33 8

8 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 4970

4970

本文介紹了AMBA 3.0 AXI的結(jié)構(gòu)和特點,分析了新的AMBA 3.0 AXI協(xié)議相對于AMBA 2. 0的優(yōu)點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28

28 學習內(nèi)容 近期設計需要用到AXI總線的IP,所以就對應常用的IP進行簡要的說明,本文主要對AXI互聯(lián)IP進行介紹。 基礎架構(gòu)IP 基礎的IP是用于幫助組裝系統(tǒng)的構(gòu)建塊。基礎架構(gòu)IP往往是一個通用IP

2021-05-11 14:52:55 5612

5612

AXI總線學習AXI協(xié)議的主要特征主要結(jié)構(gòu)通道定義讀寫地址通道讀數(shù)據(jù)通道寫數(shù)據(jù)通道寫操作回應信號接口和互聯(lián)寄存器片基本傳輸Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 uart2axi_master_intf程序源碼:/**************************************************** Module Name

2021-12-28 20:04:42 14

14 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文...

2022-02-07 11:36:33 4

4 AXI——Advanced eXtensible Interface,直譯過來就是先進的可擴展接口,是由ARM公司提出的,是一種高性能、高帶寬、低延遲的片內(nèi)總線。FPGA工程師會發(fā)現(xiàn)其大量運用于FPGA設計中,Vivado中的接口類IP全部都配有AXI接口,可見其重要性。

2022-03-14 14:13:01 4699

4699 本文主要介紹關于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 6846

6846 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數(shù)據(jù)流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 關于AXI總線協(xié)議的一些簡單知識,通過閱讀Xilinx的使用指導手冊(UG1037),結(jié)合正點原子的ZYNQ視頻進行梳理總結(jié)。

2022-07-15 09:16:29 2230

2230 本文主要介紹了AXI通道以及在每個通道下信號的概述。

2022-08-04 10:49:17 9635

9635 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2022-08-29 14:58:44 1272

1272 AXI (高性能擴展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機總線系列中的一個協(xié)議,是計劃用于高性能、高主頻的系統(tǒng)設計的。AXI協(xié)議是被優(yōu)化

2022-10-10 09:22:22 8632

8632 V1.0 ASB、APB是第一代AMBA協(xié)議的一部分。主要應用在低帶寬的外設上,如UART、 I2C,它的架構(gòu)不像AHB總線是多主設備的架構(gòu),APB總線的唯一主設備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。

2023-04-14 10:54:54 2764

2764 之前文章為大家介紹了AXI的協(xié)議與架構(gòu),本篇我們接著往下講AXI的讀寫傳輸

內(nèi)容概括

2023-05-04 14:41:27 1423

1423

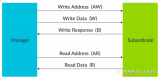

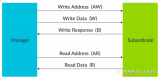

AXI 規(guī)范描述了兩個接口之間的點對點協(xié)議:manager and subordinate接口。

2023-05-05 11:42:40 462

462

在zynq開發(fā)過程中,AXI總線經(jīng)常遇到,每次看到AXI總線相關的信號時都一頭霧水,仔細研究一下,將信號分分類,發(fā)現(xiàn)其實也不難。

2023-05-25 11:22:54 570

570

AXI4協(xié)議是ARM的AMBA總線協(xié)議重要部分,ARM介紹AXI4總線協(xié)議是一種性能高,帶寬高,延遲低的總線協(xié)議。

2023-06-19 11:17:42 2097

2097

最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線進行數(shù)據(jù)和指令傳輸。如果有多個設備需要使用AXI協(xié)議對AXI接口的BRAM進行讀寫,總線之間該如何進行仲裁,通信?

2023-06-19 15:45:14 4243

4243

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

LogiCORE?IPAXI IIC總線接口連接到AMBA?AXI規(guī)范,提供低速、兩線串行總線接口,可連接大量流行的設備。

2023-09-28 15:56:16 4484

4484 LogiCORE JTAG至AXI Master IP核是一個可定制的核,可生成AXIAXI總線可用于處理和驅(qū)動系統(tǒng)中FPGA內(nèi)部的AXI信號。AXI總線接口協(xié)議可通過IP定制Vivado

2023-10-16 10:12:42 410

410

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經(jīng)常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

在介紹AXI之前,先簡單說一下總線、 接口 以及協(xié)議的含義 總線、接口和協(xié)議,這三個詞常常被聯(lián)系在一起,但是我們心里要明白他們的區(qū)別。 總線是一組傳輸通道,是各種邏輯器件構(gòu)成的傳輸數(shù)據(jù)的通道,一般

2023-12-16 15:55:01 248

248 本文主要集中在AMBA協(xié)議中的AXI4協(xié)議。之所以選擇AXI4作為講解,是因為這個協(xié)議在SoC、IC設計中應用比較廣泛。

2024-01-17 12:21:22 224

224

電子發(fā)燒友App

電子發(fā)燒友App

評論