ZYNQ中DMA與AXI4總線

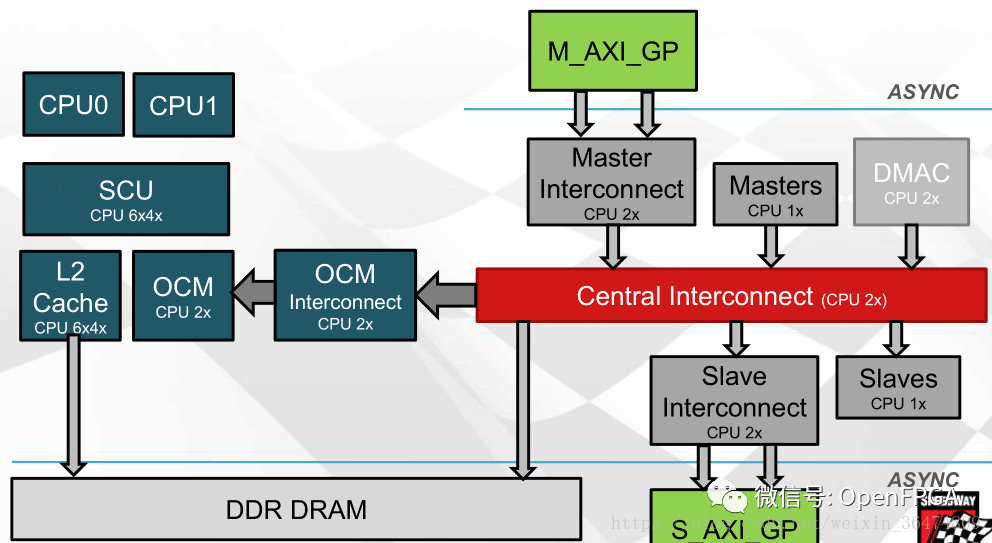

為什么在ZYNQ中DMA和AXI聯(lián)系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關(guān)功能的:

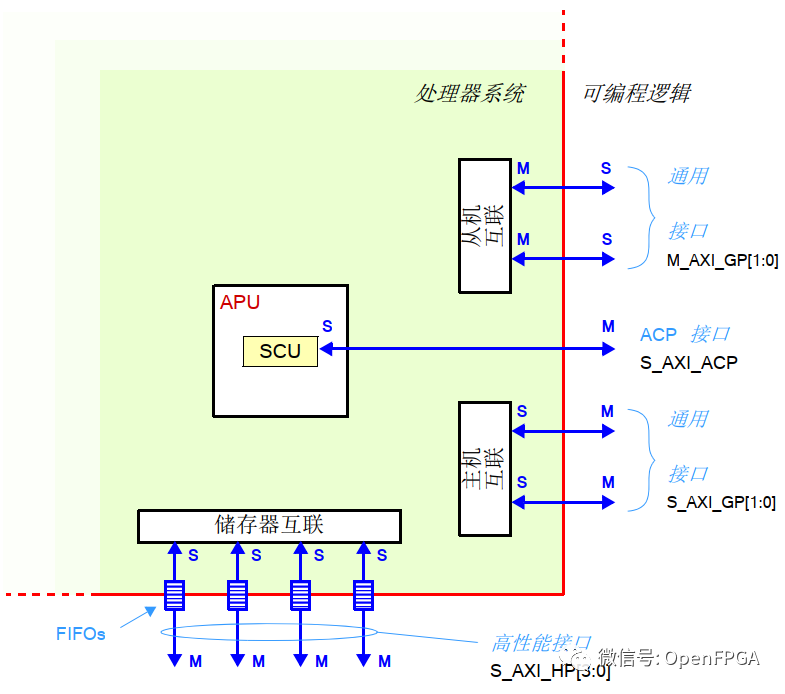

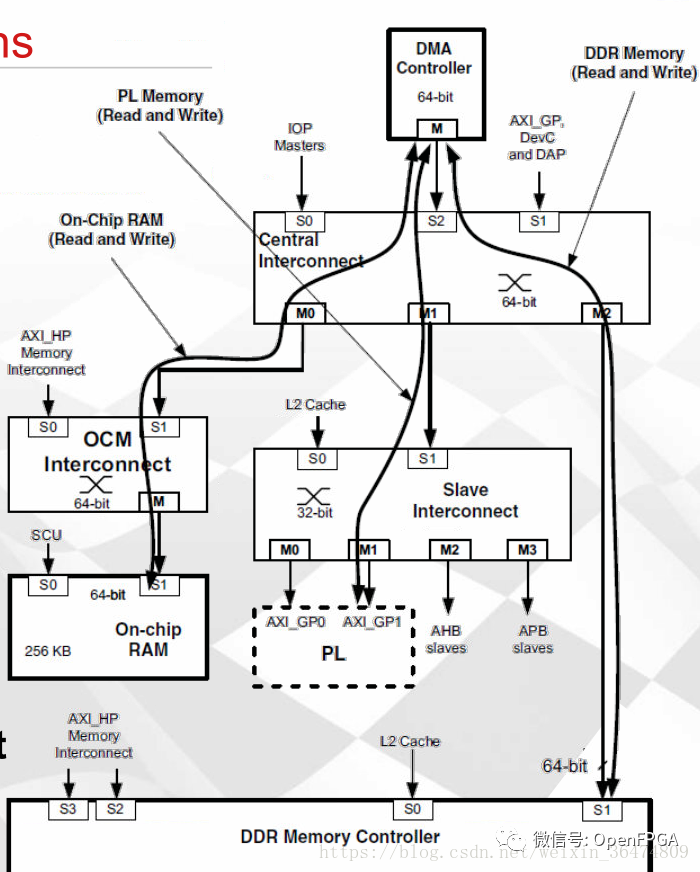

圖4?34連接 PS 和 PL 的 AXI 互聯(lián)和接口的構(gòu)架

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實(shí)現(xiàn),不能直接和PS相連,必須通過AXI-Lite或AXI4轉(zhuǎn)接。PS與PL之間的物理接口有9個,包括4個AXI-GP接口和4個AXI-HP接口、1個AXI-ACP接口。

Xilinx提供的從AXI到AXI-Stream轉(zhuǎn)換的IP核有:AXI-DMA,AXI-Datamover,AXI-FIFO-MM2S以及AXI-vDMA等

AXI-DMA:實(shí)現(xiàn)從PS內(nèi)存到PL高速傳輸高速通道AXI-HP<---->AXI-Stream的轉(zhuǎn)換

AXI-FIFO-MM2S:實(shí)現(xiàn)從PS內(nèi)存到PL通用傳輸通道AXI-GP<----->AXI-Stream的轉(zhuǎn)換

AXI-Datamover:實(shí)現(xiàn)從PS內(nèi)存到PL高速傳輸高速通道AXI-HP<---->AXI-Stream的轉(zhuǎn)換,只不過這次是完全由PL控制的,PS是完全被動的。

AXI-VDMA:實(shí)現(xiàn)從PS內(nèi)存到PL高速傳輸高速通道AXI-HP<---->AXI-Stream的轉(zhuǎn)換,只不過是專門針對視頻、圖像等二維數(shù)據(jù)的。

除了上面的還有一個AXI-CDMA IP核,這個是由PL完成的將數(shù)據(jù)從內(nèi)存的一個位置搬移到另一個位置,無需CPU來插手。

上面的IP是完成總線協(xié)議轉(zhuǎn)換,如果需要做某些處理(如變換、迭代、訓(xùn)練……),則需要生成一個自定義Stream類型IP,與上面的Stream接口連接起來,實(shí)現(xiàn)數(shù)據(jù)輸入輸出。用戶的功能在自定義Stream類型IP中實(shí)現(xiàn)。

綜上,在ZYNQ中DMA和AXI是不可分割的兩者,所以介紹DMA也是必須的。

1.1.1DMA簡介

DMA是一種內(nèi)存訪問技術(shù),允許某些計算機(jī)內(nèi)部的硬件子系統(tǒng)可以獨(dú)立的直接讀寫內(nèi)存,而不需要CPU介入處理,從而不需要CPU的大量中斷負(fù)載,否則,CPU需要從來源把每一片段的數(shù)據(jù)復(fù)制到寄存器,然后在把他們再次寫回到新的地方,在這個時間里,CPU就無法執(zhí)行其他的任務(wù)。

DMA是一種快速數(shù)據(jù)傳送方式,通常用來傳送數(shù)據(jù)量較多的數(shù)據(jù)塊。使用DMA時,CPU向DMA控制器發(fā)送一個存儲器傳輸請求,這樣當(dāng)DMA控制器在傳輸?shù)臅r候,CPU執(zhí)行其他的操作,傳輸完成時DMA以中斷的方式通知CPU。

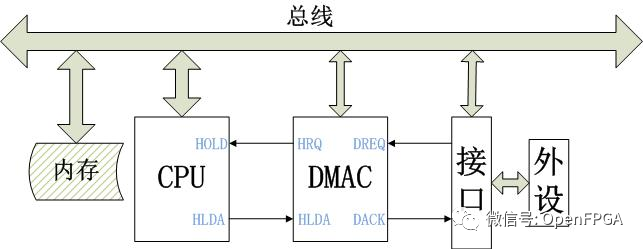

DMA傳輸過程的示意圖為:

圖4?35DMA傳輸過程的示意圖

DMA的傳輸過程為:

1、為了配置用DMA傳輸數(shù)據(jù)到存儲器,處理器(Cortex-A9)發(fā)出一條指令。

2、DMA控制器把數(shù)據(jù)從外設(shè)傳輸?shù)酱鎯ζ骰蛘邚拇鎯ζ鱾鬏數(shù)酱鎯ζ鳎瑥亩^少CPU處理的事務(wù)量。

3、輸出傳輸完成后,向CPU發(fā)出一個中斷通知DMA傳輸可以關(guān)閉。

為了發(fā)起傳輸事務(wù),DMA控制器必須得到以下信息:

(1)、源地址——數(shù)據(jù)被讀出的地址

(2)、目的地址——數(shù)據(jù)被寫入的地址

(3)、傳輸長度——應(yīng)傳輸?shù)淖止?jié)數(shù)

我們可以理解,無論是程序控制方式還是中斷控制方式,數(shù)據(jù)的傳輸都必須經(jīng)過處理器。而在一個嵌入式微處理器為主控的應(yīng)用系統(tǒng)中,當(dāng)有大量數(shù)據(jù)在存儲器和外設(shè)之間傳輸時,采用程序控制方式顯然不合適,但是若采用中斷控制方式,會造成中斷次數(shù)過于頻繁,不僅速度上不去,還需要處理器及時干預(yù)進(jìn)行處理,大大降低了工作的效率。

然而,使用DMA的好處就是它不需要CPU的干預(yù)而直接服務(wù)外設(shè),這樣CPU就可以去處理別的事務(wù),從而提高系統(tǒng)的效率,對于慢速設(shè)備,其作用只是降低CPU的使用率,但對于高速設(shè)備,它不只是降低CPU的使用率,而且能大大提高硬件設(shè)備的吞吐量。因?yàn)閷τ谶@種設(shè)備,CPU直接供應(yīng)數(shù)據(jù)的速度太低。因CPU只能一個總線周期最多存取一次總線,而且對于處理器,它不能把內(nèi)存中A地址的值直接搬到B地址。它只能先把A地址的值搬到一個寄存器,然后再從這個寄存器搬到B地址。也就是說,對于處理器,要花費(fèi)兩個總線周期才能將A地址的值送到B地址。而DMA就不同了,一般系統(tǒng)中的DMA都有突發(fā)(Burst)傳輸?shù)哪芰Γ谶@種模式下,DMA能一次傳輸幾個甚至幾十個字節(jié)的數(shù)據(jù),所以使用DMA能使設(shè)備的吞吐能力大為增強(qiáng)。

鑒于上面的優(yōu)勢,系統(tǒng)中使用DMA是必要的,能夠提高數(shù)據(jù)吞吐量,減輕了CPU的負(fù)擔(dān),使得整個系統(tǒng)的性能得到提高。

說了這么多優(yōu)點(diǎn),那么DMA缺點(diǎn)是什么呢?DMA傳送期間CPU被掛起,部分或完全失去對系統(tǒng)總線的控制,這可能會影響CPU對中斷請求的及時響應(yīng)與處理。因此,在一些小系統(tǒng)或速度要求不高、數(shù)據(jù)傳輸量不大的系統(tǒng)中,一般并不用DMA方式。因?yàn)镈MA允許外設(shè)直接訪問內(nèi)存,從而形成對總線的獨(dú)占。這在實(shí)時性強(qiáng)的硬實(shí)時系統(tǒng)嵌入式開發(fā)中將會造成中斷延時過長。

DMAC為DMA控制器

DMA傳送雖然脫離CPU的控制,但并不是說DMA傳送不需要進(jìn)行控制和管理。通常是采用DMA控制器來取代CPU,負(fù)責(zé)DMA傳送的全過程控制。目前DMA控制器都是可編程的大規(guī)模集成芯片。

圖4?36DMAC結(jié)構(gòu)

DMA控制器是內(nèi)存儲器同外設(shè)之間進(jìn)行高速數(shù)據(jù)傳送時的硬件控制電路,是一種實(shí)現(xiàn)直接數(shù)據(jù)傳送的專用處理器,它必須能取代在程序控制傳送中由CPU和軟件所完成的各項(xiàng)功能。它的主要功能是:

(1)DMAC同外設(shè)之間有一對聯(lián)絡(luò)信號線--外設(shè)的DMA請求信號DREQ以及 DMAC向外設(shè)發(fā)出的DMA響應(yīng)信號DACK;(如下圖)

(2)DMAC在接收到DREQ后,同CPU之間也有一對聯(lián)絡(luò)信號線--DMAC向CPU 發(fā)出總線請求信號(HOLD或BUSRQ),CPU在當(dāng)前總線周期結(jié)束后向DMAC發(fā)出總線響應(yīng)信號(HLDA或BUSAK),DMAC接管對總線的控制權(quán),進(jìn)入DMA操作方式;

(3)能發(fā)出地址信息,對存儲器尋址,并修改地址指針,DMAC內(nèi)部必須有能自動加1或減1的地址寄存器;

(4)能決定傳送的字節(jié)數(shù),并能判斷DMA傳送是否結(jié)束。DMA內(nèi)部必須有能自動減1的字計數(shù)寄存器,計數(shù)結(jié)束產(chǎn)生終止計數(shù)信號;

(5)能發(fā)出DMA結(jié)束信號,釋放總線,使CPU恢復(fù)總線控制權(quán);

(6)能發(fā)出讀、寫控制信號,包括存儲器訪問信號和I/O訪問信號。DMAC內(nèi)部必須有時序和讀寫控制邏輯。

圖4?37DMAC在DMA中的作用示意圖(一)

圖4?38DMAC在DMA中的作用示意圖(二)

責(zé)任編輯:xj

原文標(biāo)題:ZYNQ中DMA與AXI4總線-DMA簡介

文章出處:【微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

dma

+關(guān)注

關(guān)注

3文章

576瀏覽量

102879 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14536 -

Zynq

+關(guān)注

關(guān)注

10文章

614瀏覽量

48130

原文標(biāo)題:ZYNQ中DMA與AXI4總線-DMA簡介

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

RDMA簡介9之AXI 總線協(xié)議分析2

RDMA簡介8之AXI 總線協(xié)議分析1

NVMe IP之AXI4總線分析

NVMe簡介之AXI總線

NVMe協(xié)議簡介之AXI總線

NVMe控制器IP設(shè)計系列之接口轉(zhuǎn)換模塊

NVMe控制器IP設(shè)計之接口轉(zhuǎn)換

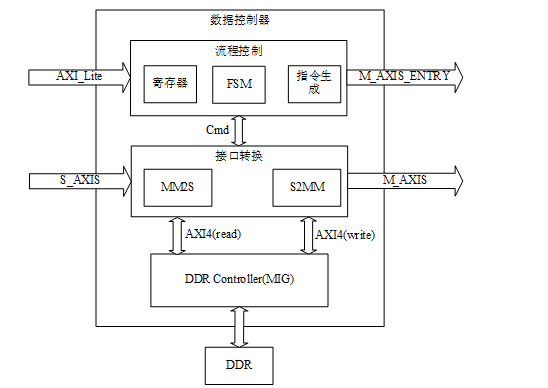

高速SSD存儲系統(tǒng)中數(shù)據(jù)緩存控制器整體頂層設(shè)計

一文詳解AXI DMA技術(shù)

ZYNQ基礎(chǔ)---AXI DMA使用

AMBA AXI4接口協(xié)議概述

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

ZYNQ中DMA與AXI4總線

ZYNQ中DMA與AXI4總線

評論