NVMe AXI4 Host Controller IP

介紹

NVMe AXI4 Host Controller IP可以連接高速存儲PCIe SSD,無需CPU,自動加速處理所有的NVMe協議命令,具備獨立的數據寫入和讀取AXI4接口,不但適用高性能、順序訪問的應用,也適用于隨機訪問的應用,同時結合外部存儲器(比如DDR),使得Host端的數據訪問管理更加靈活。

無需CPU,NVMe Host Controller IP自動執行對PCIe SSD的PCIe設備枚舉和配置、NVMe控制器識別和初始化、NVMe隊列設置和初始化,實現必須以及可選的NVMe Admin Command Set和NVM Command Set,實現對PCIe SSD的復位/斷電/SMART/Error Information/Device Self-test管理、IO(Page)讀寫、DMA讀寫和數據擦除功能,提供用戶一個簡單高效的接口實現高性能存儲解決方案。

NVMe AXI4 Host Controller IP讀寫的順序傳輸長度是RTL運行時動態可配置的,最小是4K-Byte,最大是512K-Byte。每次讀寫訪問,用戶可以指定本次傳輸的順序傳輸長度(4K~512K Byte),不同的順序傳輸長度對應不同的DMA讀寫性能。

針對多路數據通道訪問PCIe SSD,使用NVMe的多隊列特性,NVMe AXI4 Host Controller IP支持靈活配置DMA讀寫的通道個數,按照NVMe隊列優先級仲裁(循環仲裁或加權循環仲裁)機制,實現多個DMA通道對同一塊PCIe SSD的高效訪問,從而達到多路數據通道訪問的并行需求和QoS要求。

特性

支持Ultrascale+,Ultrascale,7 Series FPGA

支持PCIe Gen4,PCIe Gen3,PCIe Gen2 SSD

無需CPU

自動實現對PCIe SSD的PCIe設備枚舉、NVMe控制器識別和NVMe隊列設置

支持對PCIe SSD的NVM Subsystem Reset、Controller Reset和Shutdown

支持NVMe Admin Command Set:Identify、SMART、Error Information、Device Self-test、Create/Delete IO Submission/Completion Queue、Set Features – Volatile Write Cache/Arbitration

支持NVMe NVM Command Set:Write、Read、Flush、Dataset Management

提供1個Admin命令接口,實現對PCIe SSD的復位/斷電/SMART/Error Information/Device Self-test管理功能

提供1個IO命令接口,實現對PCIe SSD的IO(Page)讀寫、Cache Flush和邏輯數據塊擦除功能;提供1個IO-AXI4-MM接口讀寫IO(page)數據

提供1個DMA命令接口,實現對PCIe SSD的DMA讀寫功能

提供1個DMA-AXI4接口實現DMA數據的輸入和輸出

DMA讀寫的順序傳輸長度可以動態配置,4K-Byte~512K-Byte;不同的順序傳輸長度對應不同的DMA讀寫性能

針對多通道DMA需求,可以配置4個DMA命令接口,1個DMA-AXI4接口

NVMe隊列的個數(配置DMA通道的個數)和深度可配置,平衡對PCIe SSD的DMA性能和消耗的邏輯資源

支持循環仲裁(Round Robin Arbitration)和加權循環仲裁(Weighted Round Robin Arbitration)

支持NVMe Admin和IO命令的超時和錯誤處理恢復機制,提供詳盡以及擴展的訪問錯誤狀態輸出

支持的NVMe設備:

Base Class Code:01h(mass storage),Sub Class Code:08h(Non-volatile),Programming Interface:02h(NVMHCI)

MPSMIN(Memory Page Size Minimum):0(4K-byte)

MDTS(Maximum Data Transfer Size):大于等于順序傳輸長度或0(無限制)

LBA Unit:512-byte,1024-byte,2048-byte或4096-byte

一個NVMe AXI4 Host Controller IP直接連接到PCIe SSD

易于集成的同步、可綜合Verilog設計

通過完全驗證的NVMe AXI4 Host Controller IP

概述

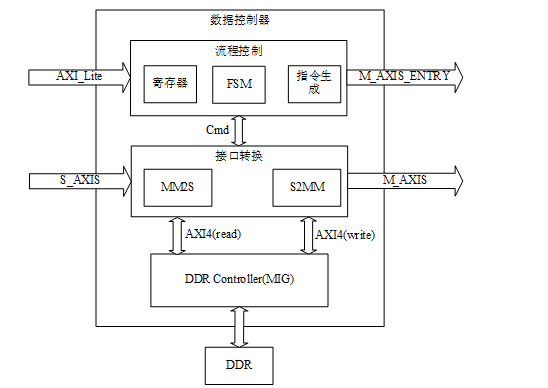

NVMe AXI4 Host Controller IP作為一個對PCIe SSD的高性能存儲控制器,不但提供對PCIe SSD的配置管理功能,而且提供對PCIe SSD的IO(Page)讀寫以及DMA讀寫功能。

NVMe AXI4 Host Controller IP具備PCIe SSD Management,實現對PCIe SSD的復位/斷電/SMART/Error Information/Device Self-test管理功能。

NVMe AXI4 Host Controller IP具備ASQ/ACQ引擎,實現NVMe Admin Command Set:Identify、SMART、Error Information、Device Self-test、Create/Delete IO Submission/Completion Queue、Set Features – Volatile Write Cache/Arbitration。

NVMe AXI4 Host Controller IP具備IO(Page) Wr/Rd引擎和SQ1/CQ1引擎,實現對PCIe SSD的IO(Page)讀寫、Cache Flush和邏輯數據塊擦除功能。

NVMe AXI4 Host Controller IP具備DMA Wr/Rd引擎和SQn/CQn引擎,實現對PCIe SSD的DMA讀寫功能。

上電后,NVMe AXI4 Host Controller IP內置的PCIe Device Enumerate & Configuration自動實現對PCIe SSD的PCIe設備枚舉和配置;然后內置的NVMe Controller Identify & Initialization自動實現對PCIe SSD的NVMe控制器識別和初始化;最后內置的Queue Setup & Initialization自動實現對PCIe SSD的NVMe隊列設置和初始化。至此,NVMe AXI4 Host Controller IP完成對PCIe SSD的所有配置和初始化工作,可以開始提供對PCIe SSD的讀寫、擦除、復位、斷電、SMART、Device Self-test操作。

圖 2 NVMe AXI4 Host Controller IP結構框圖

產品規格

性能

PCIe配置參數:Max Payload Size=256-byte,Max Read Request Size=512-byte

PCIe Gen3 SSD(三星990 Pro 4TB),Seq=512KB,1個DMA通道:

DMA寫入速度3380MB/s

DMA讀取速度3550MB/s

PCIe Gen3 SSD(三星970EVO Plus 1TB),Seq=512KB,1個DMA通道:

DMA寫入速度3320MB/s

DMA讀取速度3480MB/s

PCIe Gen3 SSD(Intel D5-P5530 3.84TB),Seq=512KB,1個DMA通道:

DMA寫入速度3350MB/s

DMA讀取速度3440MB/s

PCIe Gen3 SSD(三星980 Pro 1TB),Seq=512KB,1個DMA通道:

DMA寫入速度2950MB/s

DMA讀取速度3430MB/s

資源

KU040

表3.1 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,1-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 16016 | 21927 | 21 | 1 |

| NVMe Host Controller | 10518 | 13878 | 4 | 0 |

| PCIe Bridge | 5499 | 8049 | 17 | 1 |

表3.2 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,2-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 20546 | 26994 | 25 | 1 |

| NVMe Host Controller | 15043 | 18949 | 8 | 0 |

| PCIe Bridge | 5499 | 8049 | 17 | 1 |

表3.3 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,4-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 29686 | 36972 | 33 | 1 |

| NVMe Host Controller | 24188 | 28933 | 16 | 0 |

| PCIe Bridge | 5499 | 8049 | 17 | 1 |

ZU7EV

表3.4 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,1-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 21920 | 31099 | 38 | 1 |

| NVMe Host Controller | 10558 | 13962 | 4 | 0 |

| PCIe Bridge | 11363 | 17137 | 34 | 1 |

表3.5 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,2-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 26448 | 36126 | 42 | 1 |

| NVMe Host Controller | 15083 | 19029 | 8 | 0 |

| PCIe Bridge | 11363 | 17137 | 34 | 1 |

表3.6 PCIe Gen3 SSD,Seq=512K,Queue Depth=8,4-DMA

| LUTs | FFs | BRAMs | PCIe | |

| 總資源 | 35462 | 46253 | 50 | 1 |

| NVMe Host Controller | 24045 | 29160 | 16 | 0 |

| PCIe Bridge | 11363 | 17137 | 34 | 1 |

審核編輯 黃宇

-

PCIe

+關注

關注

16文章

1322瀏覽量

84670 -

主機控制器

+關注

關注

0文章

17瀏覽量

11925 -

AXI4

+關注

關注

0文章

20瀏覽量

9023 -

nvme

+關注

關注

0文章

243瀏覽量

23110

發布評論請先 登錄

NVMe IP之AXI4總線分析

NVMe簡介之AXI總線

NVMe控制器IP設計之接口轉換

NVME控制器之隊列管理模塊

一文詳解AXI DMA技術

一文詳解Video In to AXI4-Stream IP核

AMBA AXI4接口協議概述

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

評論