PYNQ經典項目分享:可重配置IO

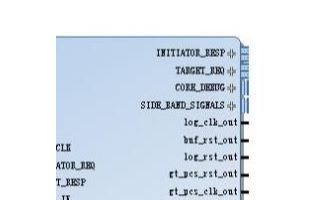

上圖為工程項目示意圖。通過軟硬件劃分,在PS端中負責Linux和通信,PL端例化了6個PR(Part....

Aurora IP建立仿真及測試

在Vivado軟件中,我們生成好IP后可以可以打開帶有例子的工程,進行仿真查看LANE_UP和CHA....

為什么在Verilog HDL設計中一定要用同步而不能用異步時序邏輯?

同步時序邏輯是指表示狀態的寄存器組的值只可能在唯一確定的觸發條件發生時刻改變。只能由時鐘的正跳沿或負....

通信中dBFS、dBm、dBV、dBW、0dB、-3dB的定義解析

dBV(V大寫),dBu(u小寫),是模擬音頻時代最常用到的兩個單位。

簡單來說專業音頻領域,標準....

介紹FPGA設計中時序分析的一些基本概念

時鐘的時序特性主要分為抖動(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Di....

FPGA復位電路的實現——以cycloneIII系列芯片為例

有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,....

初識FPGA CLB之LUT實現邏輯函數

LUT中文名字叫查找表。以7系列的FPGA為例,每一個Slice里面有四個LUT。FPGA就是通過L....

仔細看完你就懂卡爾曼濾波(Kalman Filter)

回憶一下HMM的基本模型(例如以下圖所看到的)。當中涂有陰影的圓圈(yt-2, yt-1, yt)相....

數據采集(DAQ)基礎知識:重要準則和通用術語

數據采集系統所使用的計算機會極大地影響連續采集數據的最大速度,而當今的技術已可以使用Pentium和....

SRIO IP核的三層協議的作用?

數據從遠程設備(假設為DSP的SRIO端)傳輸過來,FPGA端(假設我們這端為FPGA的SRIO端口....

基于EV10AQ190的高速ADC接口設計

外部給該ADC芯片提供一個時鐘CLK,頻率為2.5GHz,通過內部時鐘電路,2分頻之后的時鐘送到核A....

一種傅里葉分析新穎的理解方法

有了“1”,還要有“0”才能構成世界,那么頻域的“0”是什么呢?cos(0t)就是一個周期無限長的正....

解讀ADC采樣芯片EV10AQ190A的工作模式

直接說重點,任意一個輸入端口輸入的模擬信號同時進入ADC芯片的四個核(也可以理解為4個通道),這四個....

解讀ADC采樣芯片(EV10AQ190A)的工作模式(四通道模式)

由上圖可知,四通道模式有4個輸入端口,我們分別稱其為A端口,B端口,C端口,與D端口,四個端口分別對....

解讀ADC采樣芯片(EV10AQ190A)的采樣(工作)模式(雙通道模式)

當信號從A輸入端口輸入時,就意味著使用ADC A和ADC B通道對輸入的模擬信號進行采樣,雙通道組態....

手把手教系列之一階數字濾波器設計實現(附代碼)

一階數字濾波計算簡單,實現代價非常低。在濾除高頻噪聲時應用很廣泛。其本質是 IIR 濾波器,為啥要單....

如何理解FPGA的配置狀態字寄存器

賽靈思的FPGA有多種配置接口,如SPI,BPI,SeletMAP,Serial,JTAG等;如果從....

ARM和FPGA究竟是如何進行通信的呢?

ZYNQ擁有ARM+FPGA這個神奇的架構,那么ARM和FPGA究竟是如何進行通信的呢?本章通過剖析....

FPGA的算法解析1:整數操作與加減法器

整數在 IEEE 的規定上有短整數 short integer , 中整數 integer 和 長整....

傅立葉變換的實質-正交之美

對于信號,如果我們想用諧波來表示它的話,我們最好基于不同的頻率將之進行分解,那么接下來的問題就是尋找....

Xilinx FPGA的FMC接口

FMC標準定義了單寬度(69mm*76.5mm)和雙寬度(139mm*76.5mm)兩種尺寸。單寬度....

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces”

S_AXI_ACP_FPD接口實現了PS 和PL 之間的低延遲連接,通過這個128位的接口,PL端可....

Vivado怎么避免信號被優化掉

剛寫了一段 Verilog代碼,辛辛苦苦花了很長時間綜合,在debug的過程中,卻找不到需要debu....